����Ŀ¼

ǰ��

(������������ĩ,���������ļ�������ļ�,ͨ��������弶��֤)��������verilog����ʵ��uart�����첽ͨ��,FPGA���մ��ڷ���������,�������յ�������ͨ��tx�˷��͵�PC��,��PC�˴��ڴ�ӡ��ʾ����

������:SF-AT7

����ƽ̨:Vivado 2016.2

һ��Uart����ͨ��

- uart����ͨ����һ���첽����ȫ˫��ͨ�ŷ�ʽ,tx���������ݷ���,rx���������ݽ��ա��ź��߿���ʱΪ�ߵ�ƽ��

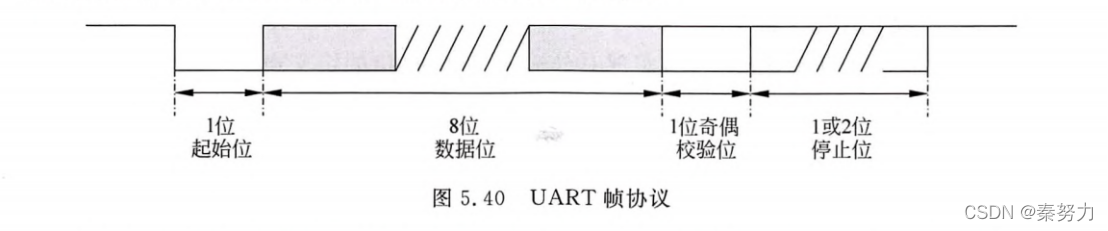

- �������첽ͨ�ŷ�ʽ,���ݷ��ͻ��װ������֡����ʽ����,֡��ʽΪ:1����ʼλ(0)��8������λ(�û�����)��1����żУ��λ(���ڼľ����Ա�֤����Ŀɿ���)��1��2��ֹͣλ(1),������żУ��λ���DZ���ġ���ͼΪ֡��ʽ�ṹ��

- ��ô����μ����ݷ�����?����ע�����֡��ʽ�е�һ��bit�ǵ͵�ƽ,��FPGA��rx�˼��ź��������½��ز���ʱ,��ʾ�����ݴ�����,����Ԥ�����úõIJ����ʶ����ݽ��ս���,���������Ǵ��дӵ�λ����λ����,���յ���������ʱ�洢�ڼĴ�����,��������1�ֽڵ�����,ͨ������ת��������յ������ݡ�

- ����ʱͨ��tx�ź��߰������úõIJ����ʽ����ݷ��ͳ�ȥ,���ݷ�����ȻҪ��������֡��ʽ����,���ȷ���1bit�ĵ͵�ƽ,�ٴӵ�λ����λ�������ݡ�

���������첽ͨ��ʵ��

1.�����ͼ

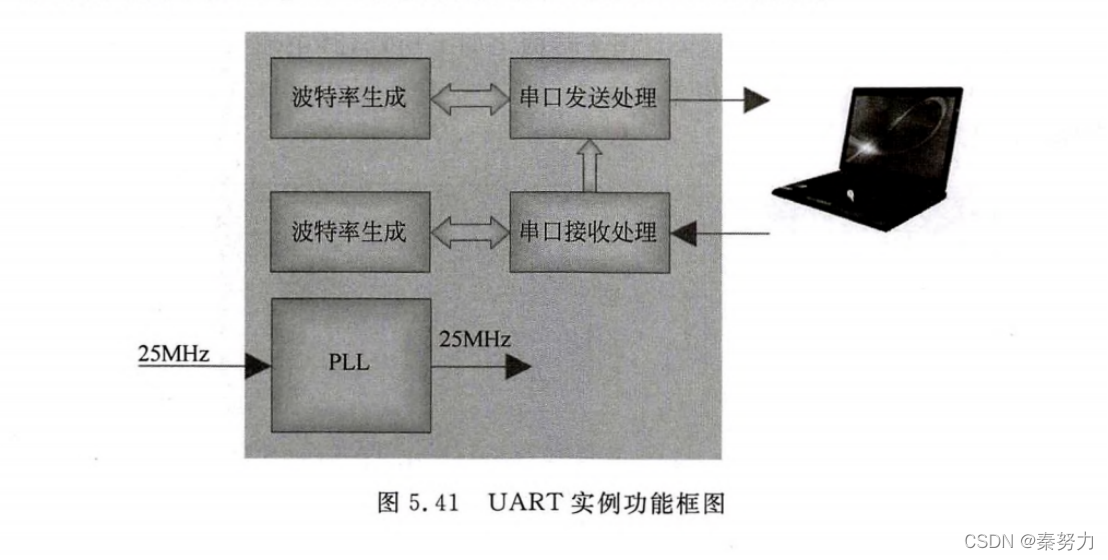

FPGAʵʱ���uart_rx�ź��Ƿ�������,�����յ�����,��ѽ��յ�������ͨ��uart_tx����PC�ˡ�

����֪���������ݴ��������õIJ������½���,�����Ҫ��ר�ŵIJ����ʲ�����Ԫ,�ҷ�������շֱ��Ӧһ�������ʲ�����Ԫ,�����������ð�װ��һ��ģ��,�ֱ��ڷ�������ն�������ģ�鼴��,��������������Ӳ����Դ,����������,��������Դ������

�����������ʵ�ֹ��̾�����һ������ģ��,�ڶ���ģ������������������ģ�顢���ڷ�������մ���ģ�顣

speed_setting u2_speed_rx(

.clk(clk_25m), //������ѡ��ģ��

.rst_n(sys_rst_n),

.bps_start(bps_start1),

.clk_bps(clk_bps1)

);

//UART�������ݴ���

my_uart_rx_q u3_my_uart_rx(

.clk(clk_25m), //��������ģ��

.rst_n(sys_rst_n),

.uart_rx(uart_rx),

.rx_data(rx_data),

.rx_int(rx_int),

.clk_bps(clk_bps1),

.bps_start(bps_start1)

);

//-------------------------------------

//UART�����źŲ���������

speed_setting u4_speed_tx(

.clk(clk_25m), //������ѡ��ģ��

.rst_n(sys_rst_n),

.bps_start(bps_start2),

.clk_bps(clk_bps2)

);

//UART�������ݴ���

my_uart_tx_q u5_my_uart_tx(

.clk(clk_25m), //��������ģ��

.rst_n(sys_rst_n),

.rx_data(rx_data),

.rx_int(rx_int),

.uart_tx(uart_tx),

.clk_bps(clk_bps2),

.bps_start(bps_start2)

);

2.����������ģ��

- ǰ��˵�����������ñ�����һ��������,���õIJ�������9600��115200����ָ1s�ȴ������ݵĸ���,1/9600����һ����������Ӧ��ʱ������25MHzΪ��,һ��������40ns ,��ô�������ھ���:1/9600/40ns*1000000000(ע�ⵥλͳһ),����һ��������,�����������ﵽ9600bpsʱ,��־λ��һ�����ڵĸ������ź�,�ñ�־λ�ź���������tx�˴�������λ���л�����rx�˽�������λ���л���

- ��������ķ������,����verilog���Ա��ʵ��,������һ��always����ʵ�ּ�����,��һ��always��ʵ�ֱ�־λ��λ��Ϊ�˱�֤���ݲɼ�������,����ѡ�������ݴ����м����,���������ǵ�9600һ���ʱ��������ݲ�����

- ��Խ��ն�,uart�˿�rx�˽��յ��������ߵ��źš����������ݶ������ֽڵ���ʽ����,��uartͨ��Э���й涨�����Ǵ��н��յ�,��˽���ʱҪ���д���ת��,����ת���������ɲ����ʾ��������յ��źź���������ģ�鿪ʼ����,��ʱ����ά��һ�����ڸߵ�ƽ�IJ����źš�

��������:

module speed_setting(

input clk,

input rst_n,

input bps_start,

output clk_bps

);

`define BPS_9600

`define CLK_PERIORD 40 //����ʱ������Ϊ40ns(25MHz)

`define BPS_SET 9600 //����ͨ�Ų�����Ϊ9600bps(����Ҫ�IJ�����ʡȥ��������弴��)

`define BPS_PARA (1_000_000_000/`CLK_PERIORD/`BPS_SET)//10_000_000/`CLK_PERIORD/96; //������Ϊ9600ʱ�ķ�Ƶ����ֵ

`define BPS_PARA_2 (`BPS_PARA/2)//BPS_PARA/2; //������Ϊ9600ʱ�ķ�Ƶ����ֵ��һ��,�������ݲ���

reg[12:0] cnt; //��Ƶ����

reg clk_bps_r; //������ʱ�ӼĴ���

//----------------------------------------------------------

reg[2:0] uart_ctrl; // uart������ѡ��Ĵ���

//����������

always@(posedge clk or negedge rst_n)begin

if(!rst_n) cnt <= 13'd0 ;

else if(bps_start)begin

if(cnt < BPS_PARA) cnt <= cnt + 13'd1 ;

else cnt <= 13'd0 ;

end

else cnt <= 13'd0 ;

end

//�����źű�־λ

always@(posedge clk or negedge rst_n)begin

if(!rst_n) clk_bps_r <= 1'b0 ;

else if(cnt == BPS_PARA_2) clk_bps_r <= 1'b1 ;

else clk_bps_r <= 1'b0 ;

end

assign clk_bps = clk_bps_r ;

endmodule

3.���ڷ��Ϳ���ģ��

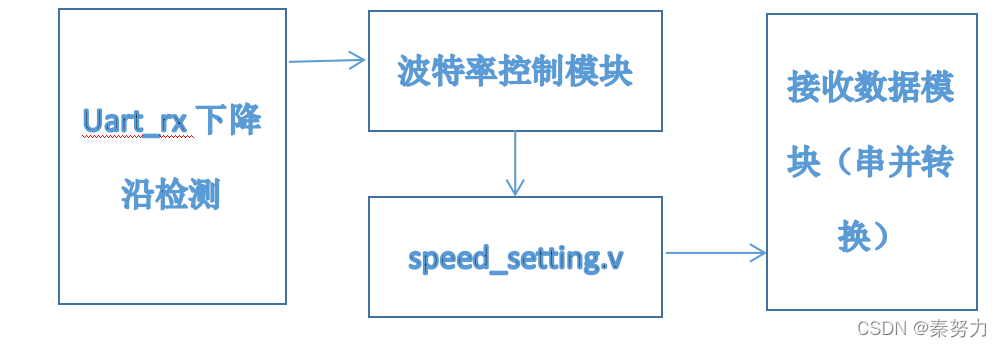

��ģ��ʵ�ֶ�UART�����ź�uart_rx���н���,��ʵ�ִ���ת��,�������ݱ����ڡ�rx_data[7:0]���С���������ڲ�ʵ�ֿ�ͼ����:

- �½��ؼ��

ͨ������źš�uart_rx���ź��½��ء����ж��Ƿ����źŷ����������ؼ��һ������ö��������,����uart_rx��״̬,����ǰ��״̬���������������ж�,���ǰһ��״̬�Ǹߵ�ƽ,���µ�״̬Ϊ�͵�ƽ,���ʾ�������½��ء�

module my_uart_rx(

clk,rst_n,

uart_rx,rx_data,rx_int,

clk_bps,bps_start

);

input clk; // 25MHz��ʱ��

input rst_n; //�͵�ƽ��λ�ź�

input uart_rx; // RS232���������ź�

input clk_bps; // clk_bps�ĸߵ�ƽΪ���ջ��߷�������λ���м������

output bps_start; //���յ����ݺ�,������ʱ�������ź���λ

output[7:0] rx_data; //�������ݼĴ���,����ֱ����һ����������

output rx_int; //���������ж��ź�,���յ������ڼ�ʼ��Ϊ�ߵ�ƽ

//----------------------------------------------------------------

reg uart_rx0,uart_rx1,uart_rx2,uart_rx3; //�������ݼĴ���,�˲���

wire neg_uart_rx; //��ʾ�����߽��յ��½���

always @ (posedge clk or negedge rst_n)

if(!rst_n) begin

uart_rx0 <= 1'b0;

uart_rx1 <= 1'b0;

uart_rx2 <= 1'b0;

uart_rx3 <= 1'b0;

end

else begin

uart_rx0 <= uart_rx;

uart_rx1 <= uart_rx0;

uart_rx2 <= uart_rx1;

uart_rx3 <= uart_rx2;

end

assign neg_uart_rx = uart_rx3 & uart_rx2 & ~uart_rx1 & ~uart_rx0;

-

�����ʿ���ģ��

��ģ����Ϊ�ź��½��صĵ���,ʹ�á�bps_start���ź���Ϊ1,��������������ģ�顣 -

��������ģ��

�������ݴӵ�λ����λ���д���,����Ҫ����һ���Ĵ����ݴ�����,�ҵ�һλ�DZ�ʶλ,��Ӧ�ý���洢�ڼĴ�����,���á�num����0��ʼ����,������1ʱ��ÿ�������ʸߵ�ƽ��Ч��һ�������ڴӵ�λ����λ�������ݡ�

always @ (posedge clk or negedge rst_n)

if(!rst_n) begin

rx_temp_data <= 8'd0;

num <= 4'd0;

rx_data_r <= 8'd0;

end

else if(rx_int) begin //�������ݴ���

if(clk_bps) begin //��ȡ����������,��������Ϊһ����ʼλ,8bit����,1��2������λ

num <= num+1'b1;

case (num)

4'd1: rx_temp_data[0] <= uart_rx; //�����0bit

4'd2: rx_temp_data[1] <= uart_rx; //�����1bit

4'd3: rx_temp_data[2] <= uart_rx; //�����2bit

4'd4: rx_temp_data[3] <= uart_rx; //�����3bit

4'd5: rx_temp_data[4] <= uart_rx; //�����4bit

4'd6: rx_temp_data[5] <= uart_rx; //�����5bit

4'd7: rx_temp_data[6] <= uart_rx; //�����6bit

4'd8: rx_temp_data[7] <= uart_rx; //�����7bit

default: ;

endcase

end

else if(num == 4'd9) begin //���ǵı�����ģʽ��ֻ��1+8+1(2)=11bit����Ч����

num <= 4'd0; //���յ�STOPλ�����,num����

rx_data_r <= rx_temp_data; //���������浽���ݼĴ���rx_data��

end

end

assign rx_data = rx_data_r;

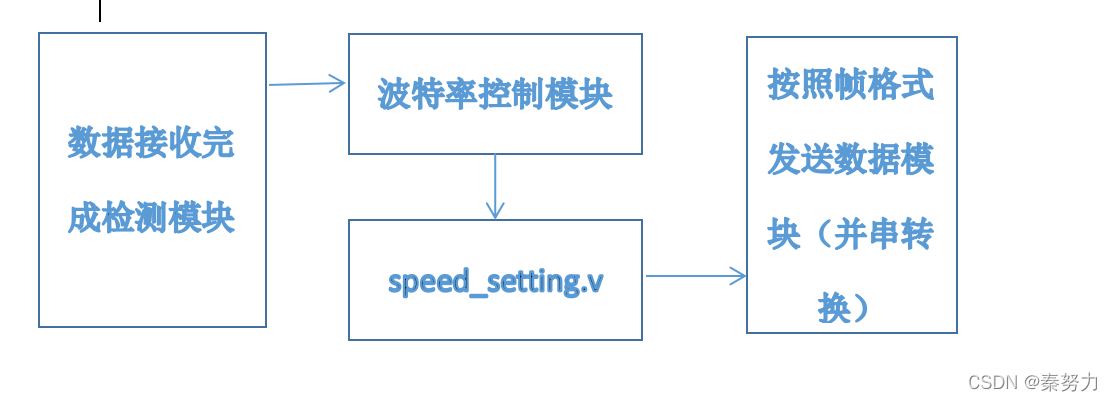

4.���ڷ��Ϳ���ģ��

uart���ն˽���������ɺ�,ͨ����uart_tx���˽����յ������ݡ�rx_data��f���ͳ�ȥ���������̿�ͼ����:

ע��:��ΪҪ��ȫ����֡��ʽ��������,����Ҫ�ȷ���һ�����������ڵĵ͵�ƽ,�ڴӵ͵��ߴ�������λ��

reg uart_tx_r ;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

num <= 4'd0 ;

uart_tx_r <= 1'b1;

end

else if(tx_en)begin

if(clk_bps)begin

num <= num + 4'd1 ;

case(num)

4'd0 : uart_tx_r <= 1'b0 ;

4'd1 : uart_tx_r <= tx_data[0] ;

4'd2 : uart_tx_r <= tx_data[1] ;

4'd3 : uart_tx_r <= tx_data[2] ;

4'd4 : uart_tx_r <= tx_data[3] ;

4'd5 : uart_tx_r <= tx_data[4] ;

4'd6 : uart_tx_r <= tx_data[5] ;

4'd7 : uart_tx_r <= tx_data[6] ;

4'd8 : uart_tx_r <= tx_data[7] ;

4'd9 : uart_tx_r <= 1'b1 ;

default: uart_tx_r <= 1'b1;

endcase

end

else if(num == 4'd10)begin

num <= 4'd0 ;

end

end

end

assign uart_tx = uart_tx_r;

�������

1��������

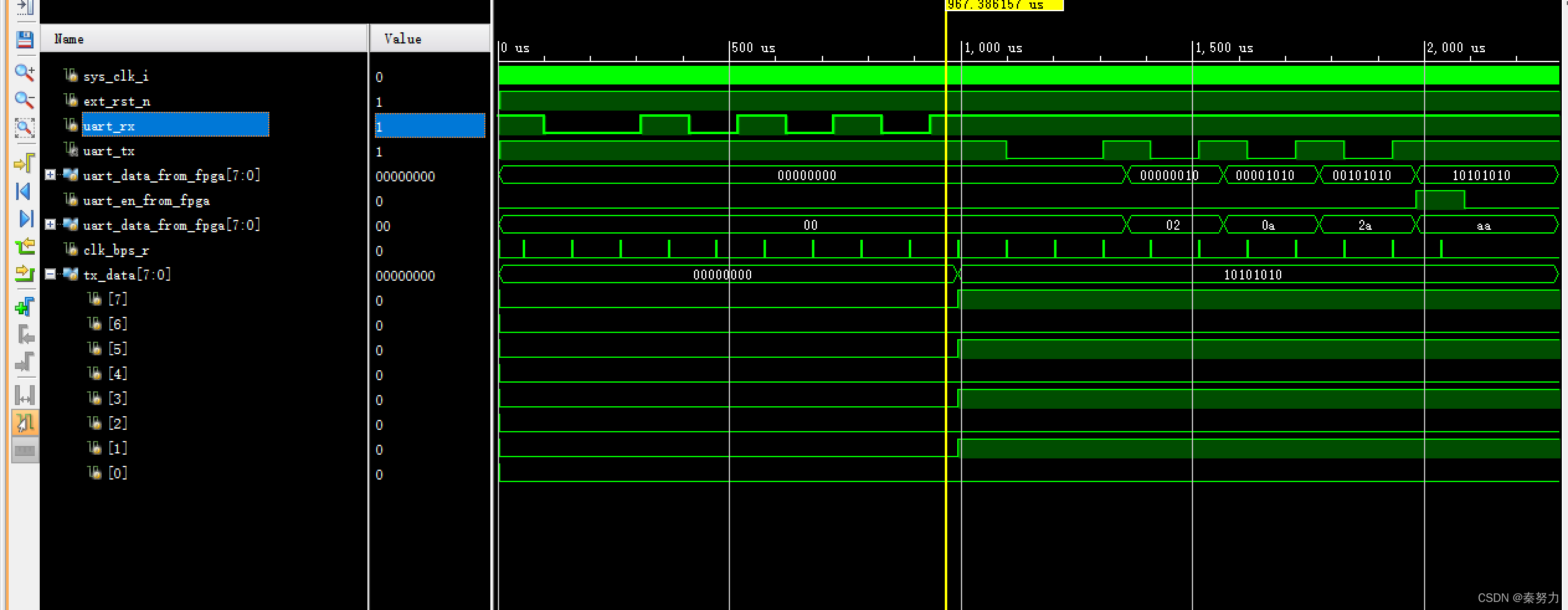

- ���沨�ο��Կ���,uart_rx�˽��źš�8��haa�����չ���,������ÿ��bps���ڵ��м����,Ȼ����ͨ����uart_tx���˷��ͳ�ȥ,��ÿ����clk_bps����Ч��һ��ʱ�������ڴӵ�λ����λ������յ�������

2���弶���Խ��

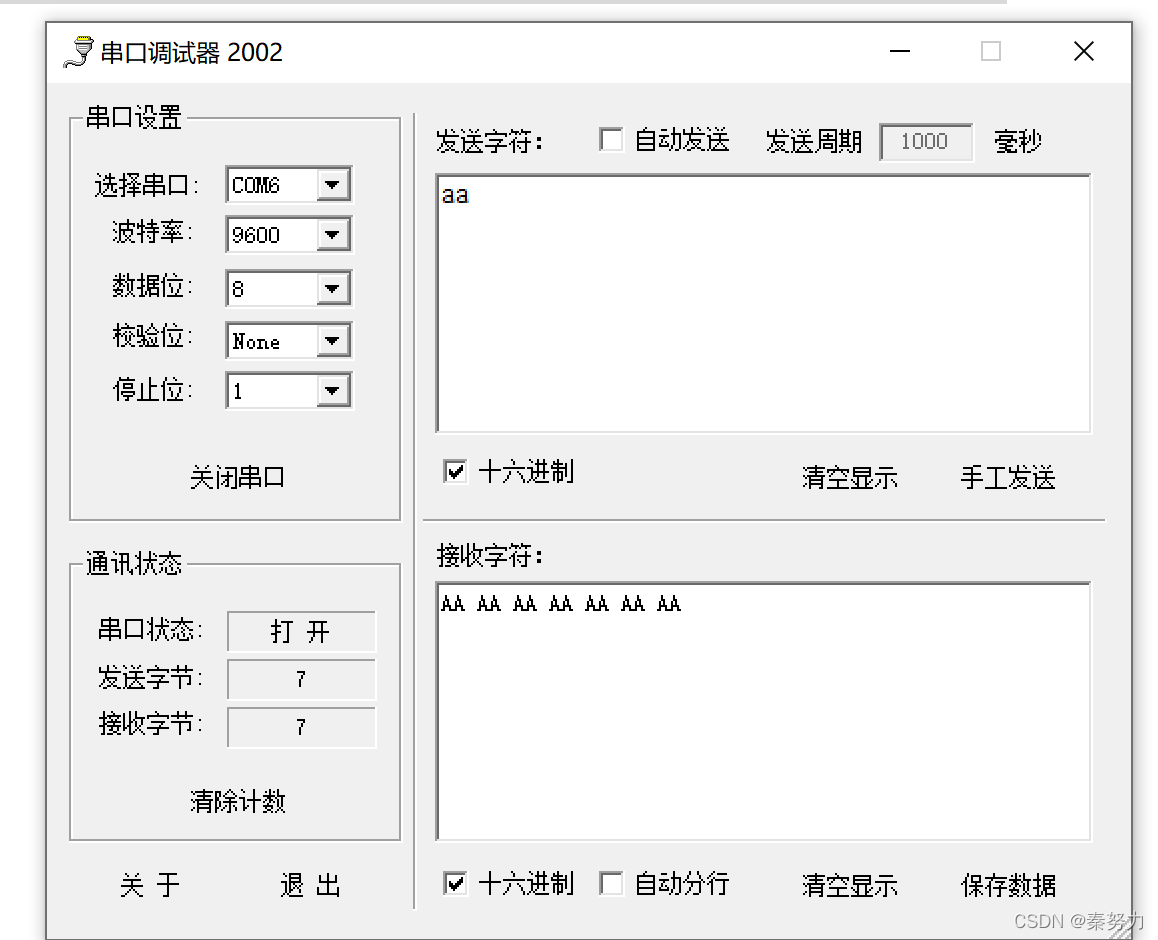

- ���ô��ڵ��Թ���,����8bit���ݡ�aa��,���Կ������ն˳ɹ����յ������ݡ�

����ļ�������ļ�

https://pan.baidu.com/s/1dnoyo84pEtMlk5fSQdaqSA ��ȡ��:p4q1