第三章

Transfers

本章描述读写传输。它包括以下部分:

– 基本传输 on page 3-28.

– 传输类型 on page 3-30.

– 锁定传输 on page 3-32.

– 传输大小 on page 3-33.

– 突发操作 on page 3-34.

– 等待传输 on page 3-39.

– 保护控制 on page 3-44.

– 内存类型 on page 3-45.

3.1 Basic transfers

传输由两个阶段组成:

Address:持续一个HCLK周期,除非它被之前的总线传输扩展。

Data:可能需要几个HCLK周期。使用HREADY信号控制完成传输所需的时钟周期的数量。

HWRITE控制数据向主机或从主机传输的方向。因此,当:

-HWRITE为高,表明是写传输,主机广播数据在写数据总线上HWDATA[31:0]

-HWRITE为低 ,执行读数据传输,从机必须在读数据总线上生成数据HRDATA[31:0].

最简单的传输是没有等待状态的传输,因此传输由一个地址周期和数据周期组成。

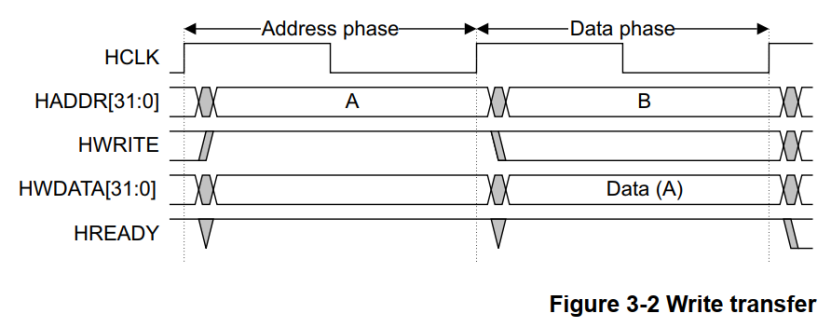

图 3-1 显示一个简单的读传输和图3-2显示一个简单的写传输.

在一个没有等待状态的简单传输中:

- 主机在HCLK上升沿后将地址和控制信号驱动到总线上。

- 然后从机在HCLK的下一个上升沿上采样地址和控制信息。

- 在slave对地址和控制进行采样后,它可以开始驱动适当的HREADYOUT响应。该响应由主控器在HCLK的第三个上升沿采样。

这个简单的例子演示了传输的地址和数据阶段在不同的时钟周期是如何发生的。

在前一个传输的数据阶段期间,任何传输的地址阶段产生。当仍然为从机提供足够的时间来对传输提供响应时,这种地址和数据的重叠是总线流水线性质的基础,能够实现高性能操作。

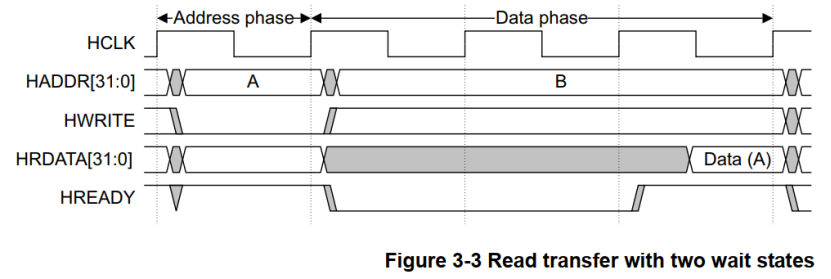

从机可以在任何传输中插入等待状态,以增加完成的时间。每个从机都有一个HREADYOUT信号,它在传输的数据阶段驱动。互连负责组合所有从站的HREADYOUT信号,生成一个单独的HREADY信号,用于控制整个进程。

Figure 3-3 显示具有两个等待状态的读传输。

Figure 3-4 显示有一个等待状态的写传输。

Note

对于写操作,主机在整个扩展周期内保持数据稳定。对于读操作,直到传输即将完成之前,从机不必提供有效的数据。关于稳定数据使用的更多信息,请参见第7-68页的Clock。

当一个传输以这种方式扩展时,当以这种方式扩展一个传输时,它具有扩展下一个传输的地址阶段的副作用。

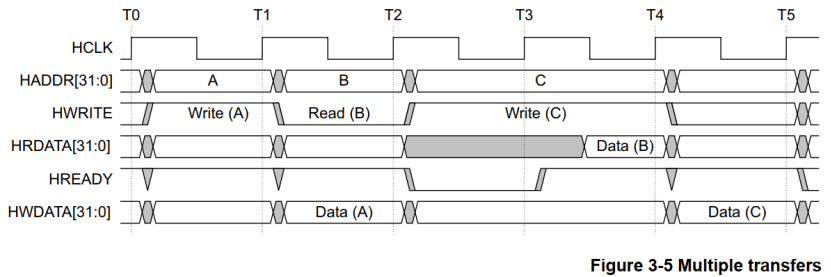

图3-5所示为3个不相关地址A、B和C的传输,地址C有一个扩展的地址阶段。

在图3 - 5:

- 对地址A和C的传输是零等待状态。

- 传输到地址B有一个等待状态。

- 对地址B的数据阶段的扩展传输对地址C的地址阶段传输由影响。

3.2 Transfer types

传输可分为四种类型之一,由HTRANS控制[1:0]。Table 3-1列出了这些.

Table 3-1 传输类型编码

| HTRANS[1:0] | Type | Description |

|---|---|---|

| 0b00 | IDLE | 表示不需要数据传输。当主机不想执行数据传输时,它使用IDLE传输。建议主机用IDLE传输终止锁定传输。从机必须始终为IDLE传输提供一个零等待状态的OKAY响应,并且该传输必须被slave忽略 |

| 0b01 | BUSY | BUSY传输类型使主机在突发传输中插入idle周期。这种传输类型表明主机正在以突发传输继续,但下一个传输不能立即发生。当主机使用BUSY传输类型时,地址和控制信号必须反映在突发中的下一个传输。只有未定义长度的突发才能将BUSY传输作为突发的最后一个周期。参见第3-35页的BUSY传输后突发终止。从机必须始终为BUSY传输提供一个零等待状态的OKAY响应,并且传输必须被从机忽略。 |

| 0b10 | NONSEQ | 表明一个SINGLE传输或突发传输第一个传输。地址和控制信号与之前的传输无关。总线上的SINGLE传输被视为长度为1的突发,因此传输类型是NONSEQUENTIAL。 |

| 0b11 | SEQ | 在一个突发中,剩余的传输是顺序的,地址与前一次传输有关。控制信息与前一次传输相同。该地址等于前一个传输的地址加上传输大小(以字节为单位),传输大小由HSIZE[2:0]信号发出。在环回突发传输的情况下,传输的地址在地址边界环回 |

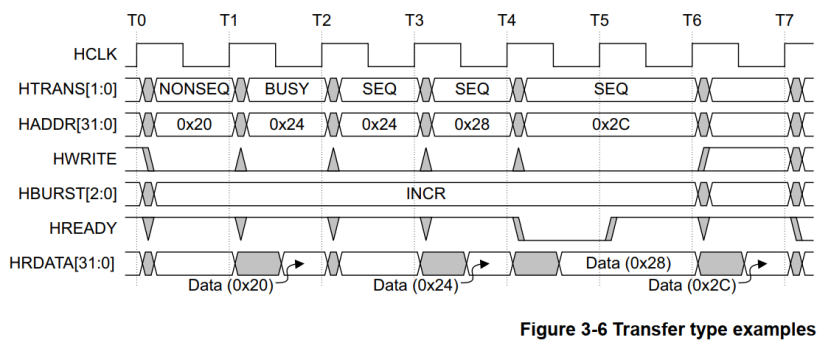

NONSEQ、BUSY和SEQ三种传输类型的使用如图3-6所示。

在图3 - 6:

T0-T1 四拍读取从NONSEQ传输开始。

T1-T2 主机无法执行第二个节拍,并插入一个BUSY传输来延迟第二个节拍的开始。从机为第一个节拍提供读数据。

T2-T3 主机现在准备开始第二个传输,因此一个SEQ传输被信号标识。主机忽略从机提供在读数据总线上的数据。

T3-T4 主机执行第三个节拍。从机为第二个节拍提供数据。

T4-T5 主机提供最后一个节拍。从机不能完成传输,使用HREADYOUT

插入一个等待状态。

T5-T6 从机为第三个节拍提供读数据。

T6-T7 从机为最后一拍提供读数据。

3.3 Locked transfers

如果主机需要锁定访问,那么它还必须插入HMASTLOCK信号。这个信号指示任何slave当前的传输序列是不可分割的,因此必须在任何其他传输被处理之前被处理。通常,锁定传输用于维护信号量的完整性,通过确保从机在微处理器SWP指令的读和写阶段之间不执行其他操作。

图3-7显示了带有微处理器SWP指令的HMASTLOCK信号。

Note

在锁定传输之后,建议主机插入IDLE传输。

大多数从机没有实现HMASTLOCK的要求,因为它们只能按照接收到的顺序执行传输。可以被多个主机访问的从机,例如,一个多端口内存控制器(MPMC)必须实现HMASTLOCK信号。

允许主机在一个锁定传输序列的开始、中间或结尾为IDLE传输插入HMASTLOCK。允许在锁定传输序列的开始或结束处使用锁定的IDLE传输,但不推荐,因为这种行为会对系统的仲裁产生不利影响。

也允许(但不建议)对主机插入HMASTLOCK一定数量的IDLE传输,然后在不执行非idle传输的情况下去解除断言HMASTLOCK。这种行为会对系统的仲裁产生不利影响。

要求在锁定序列中的所有传输都是到相同的从机地址区域。

Note

在本规范的问题a中,不存在确保在一个锁定序列中的所有传输都是到同一从地址区域的要求。必须对遗留组件进行验证,以确保它不会出现这种行为。

3.4 Transfer size

HSIZE[2:0]表示数据传输的大小。可能的传输大小如表3-2所示。

Table 3-2传输大小编码

| HSIZE[2] | HSIZE[1] | HSIZE[0] | Size(bits) | Description |

|---|---|---|---|---|

| 0 | 0 | 0 | 8 | Byte |

| 0 | 0 | 1 | 16 | Halfword |

| 0 | 1 | 0 | 32 | Word |

| 0 | 1 | 1 | 64 | Doubleword |

| 1 | 0 | 0 | 128 | 4-word line |

| 1 | 0 | 1 | 256 | 8-word line |

| 1 | 1 | 0 | 512 | - |

| 1 | 1 | 1 | 1024 | - |

Note

HSIZE设置的传输大小必须小于或等于数据总线的宽度。例如,对于32位数据总线,HSIZE必须只使用值0b000、0b001或0b010。

将HSIZE与HBURST结合使用,以决定环回突发的地址边界。

HSIZE信号与地址总线具有完全相同的时序。然而,它们必须在整个突发传输过程中保持恒定。

3.5 Burst operation

在此协议中定义了4拍,8拍和16拍,未定义长度的突发,SINGLE传输。它支持递增和环回突发:

– 在突发中每一次传输的递增突发访问顺序位置和地址是前一个地址的增量。

– 当跨越地址边界时,环回突发会环回。地址边界计算为突发中节拍数与传输大小的乘积。节拍数由HBURST控制,传输大小由HSIZE控制。

例如,一个四拍的字(4字节)访问在16字节边界处环回。因此,如果burst的起始地址是0x34,那么它包含了对地址0x34、0x38、0x3C和0x30的4次传输。

HBURST[2:0]控制突发类型.

Table 3-3 列出可能的突发类型.

| HBURST[2:0] | Type | Description |

|---|---|---|

| 0b000 | SINGLE | SINGLE传输突发 |

| 0b001 | INCR | 未定义长度的递增突发 |

| 0b010 | WRAP4 | 4拍环回突发 |

| 0b011 | INCR4 | 4拍递增突发 |

| 0b100 | WRAP8 | 8拍环回突发 |

| 0b101 | INCR8 | 8拍递增突发 |

| 0b110 | WRAP16 | 16拍环回突发 |

| 0b111 | INCR16 | 16拍递增突发 |

master不能尝试启动一个跨越1KB地址边界的递增突发。

master可以使用以下任意一种方式执行SINGLE传输:

– SINGLE传输突发.

– 长度为1的未定义长度的突发

Note

突发大小是指突发中的节拍数,而不是传输的字节数。用节拍数乘以每个节拍的数据量,如HSIZE[2:0]所示,计算出突发中传输的数据总量。

在一个突发中的所有传输必须与地址边界对齐,地址边界等于传输的大小。例如,字传输必须对齐到字地址边界(HADDR[1:0] = 0b00),半字传输到半字地址边界(HADDR[0] = 0)。IDLE传输的地址也必须对齐,否则在仿真过程中,总线监视器很可能报告虚假的警告。

3.5.1 Burst termination after a BUSY transfer

在突发开始后,如果需要更多的时间才能继续进行突发中的下一个传输,主机就会使用BUSY传输。

在未定义长度突发INCR期间,主机可能插入BUSY传输,然后决定不再需要更多的数据传输。在这些情况下,主机可以执行NONSEQ或IDLE传输,然后有效地终止未定义的长度突发。

对于固定长度的突发类型,协议不允许master用BUSY传输结束突发:

– 递增INCR4, INCR8, and INCR16.

– 环回WRAP4, WRAP8, and WRAP16.

这些固定长度的突发类型必须以SEQ传输结束。

主机不允许在SINGLE突发后立即执行BUSY传输。SINGLE突发必须紧随一个IDLE传输或一个NONSEQ传输。

3.5.2 Early burst termination

突发可以通过以下两种方式终止:

– 从机错误响应

– 多层互联终止

从机错误响应

如果从机提供了一个ERROR响应,那么主机可以取消突发中剩余的传输。然而,这不是一个严格的要求,对于主机来说,在突发中继续剩余的传输也是可以接受的。

如果主机取消了突发中剩余的传输,那么它必须在两个周期的Error响应期间更改HTRANS以表明IDLE。

如果主机没有完成这个突发传输,那么当它下次访问那个从机时,没有要求去重建这个突发。例如,如果一个主机只完成了一个8拍脉冲的3拍,那么当它下次访问这个从机时,它不需要完成剩下的5次传输。

多层互联中止

虽然主机不允许提前终止突发请求,但从机必须在突发未完成时能够正常工作。当多层互连组件在多主系统中使用时,它可以终止突发,这样另一个主机就可以访问从机。如果发生这种情况,从机必须终止来自原始主机的突发,然后对新主机作出适当的响应。

3.5.3 Burst examples

以下部分展示了集中突发的实例:

– 四拍环回突发, WRAP4.

– 四拍递增突发, INCR4 on page 3-37.

– 八拍环回突发, WRAP8 on page 3-37.

– 八拍递增突发, INCR8 on page 3-38.

-未定义长度突发, INCR on page 3-38.

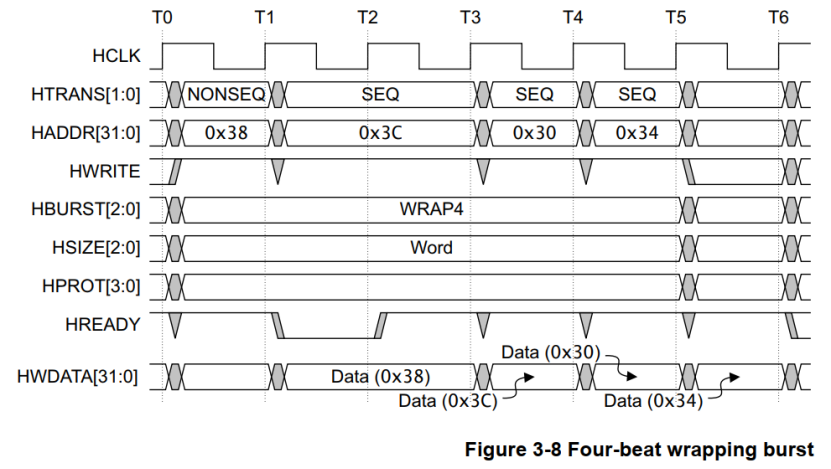

四拍环回突发, WRAP4

图3-8显示了一个使用四拍环回突发的写传输,并为第一次传输增加了一个等待状态。

因为这个突发是字传输的四拍突发,地址环回在16字节边界,向地址0x3C的传输之后是向地址0x30的传输。

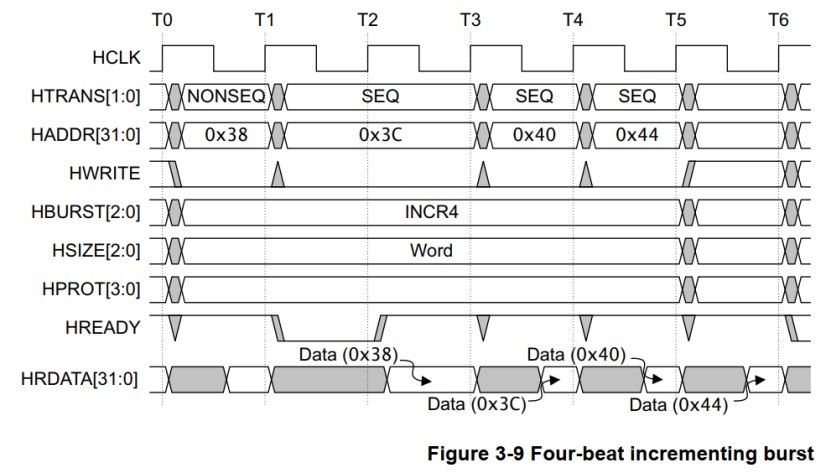

四拍递增突发, INCR4

图3-9显示了一个使用四拍递增突发的读传输,并且第一个传输具有等待状态。在这种情况下,地址在16字节边界没有环回,地址0x3C之后是地址0x40的传输。

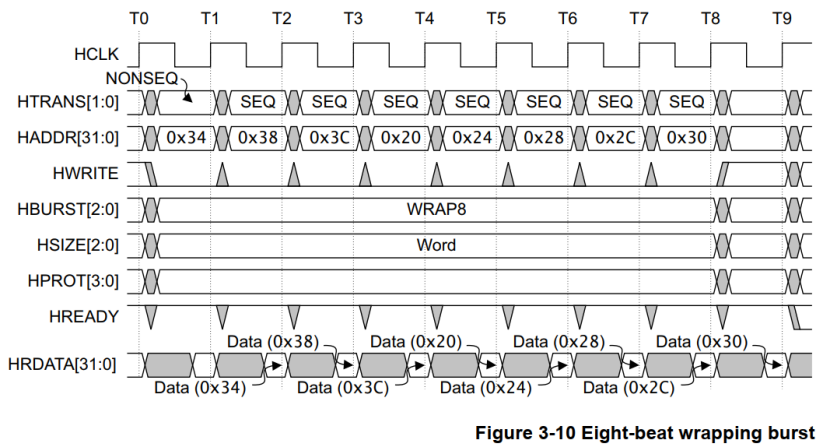

八拍环回突发, WRAP8

图3-10展示了一个使用八拍环回的读传输。

因为这个突发是一个八拍的字传输,地址环回在32字节边界处,地址0x3C的传输之后是到地址0x20的传输。

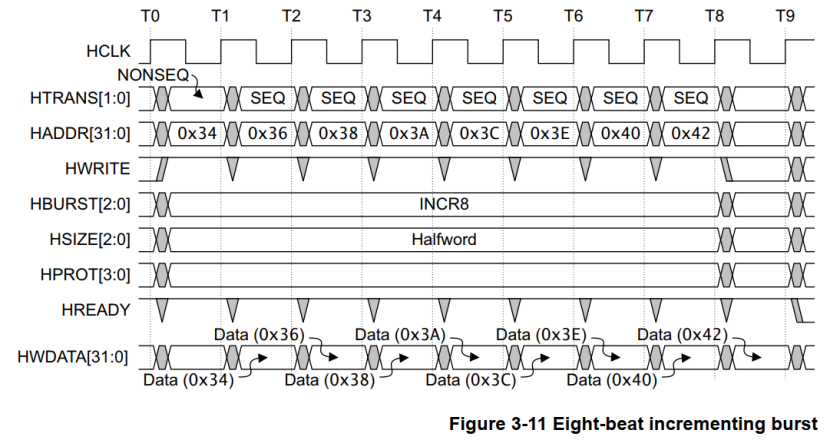

八拍递增突发, INCR8

图3-11展示了使用八拍递增突发的写传输。

这个突发使用半字节传输,因此地址增加2。因为突发是递增的,地址继续增加到超过16字节边界。

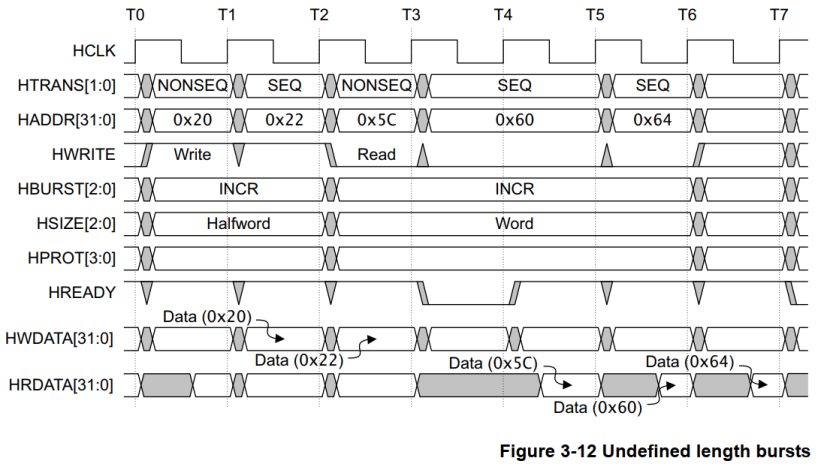

未定义长度突发, INCR

图3-12展示了未定义长度的递增突发。

图3-12显示了两个突发:

– 第一个突发是由两个从地址0x20开始的半字传输组成的写。这些传输地址地递增2。

– 第二个突发是由从地址0x5C开始的三个字传输组成的读取。这些传输地址递增4。

3.6 Waited transfers

如果需要更多的时间来提供数据或对数据进行采样,从机可以使用HREADYOUT来插入等待状态。在等待的传输期间,主机被限制为它可以对传输类型和地址做什么更改。这些限制将在以下章节中描述:

– 在等待状态期间传输类型更改。

– 在3-42页的等待状态期间的地址变化。

3.6.1 Transfer type changes during wait states

当从机处于请求等待状态时,master不能改变传输类型,除非如下所述:

– IDLE传输

– BUSY传输, 固定长度突发on page 3-40.

– BUSY传输, 未定义长度突发on page 3-41.

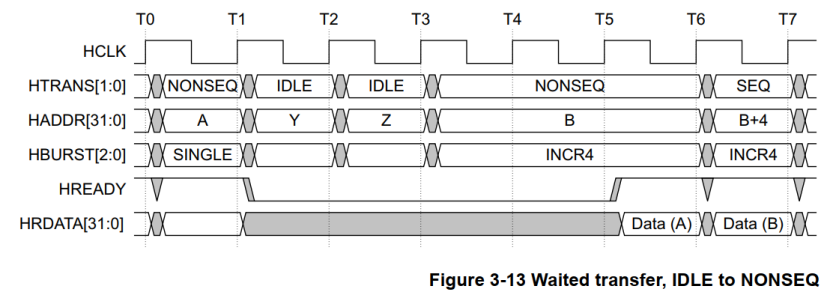

IDLE传输

在等待状态传输期间,主机允许可以将传输类型从IDLE更改为NONSEQ。当HTRANS传输类型变为NONSEQ时,主机必须保持HTRANS不变,直到HREADY为高。

图3-13显示了一个SINGLE突发的等待状态,传输类型熊IDLE更改为NONSEQ。

在图3-13:

T0-T1 主机发起一个SINGLE突发到地址A。

T1-T2 主机发起一个IDLE传输到地址Y。从机插入一个具有HREADYOUT = LOW的等待状态。

T2-T3 主机插入一个IDLE传输到地址Z。

T3-T4 主机将传输类型更改为NONSEQ,并向地址B发起INCR4传输。

T4-T6 HREADY LOW时,主机必须保持HTRANS恒定。

T5-T6 SINGLE突发到地址A以HREADY HIGH完成,主机开始第一拍带地址B。

T6-T7 INCR4向地址B传输的第一个节拍完成,主机开始向地址B+4传输的下一个节拍。

BUSY传输, 固定长度突发

在固定长度突发的等待状态传输过程中,主机允许传输类型从BUSY改变到SEQ。当HTRANS传输类型更改为SEQ时,主机必须保持HTRANS不变,直到HREADY为HIGH。

Note

因为BUSY传输必须只插入连续的突发节拍之间,这不适用于SINGLE。 因此,这种情况适用于以下几种突发类型:

? INCR4, INCR8, and INCR16.

? WRAP4, WRAP8, and WRAP16.

图3-14所示为固定长度突发的等待传输,传输类型从BUSY转换为SEQ。

In Figure 3-14:

T0-T1 主机启动INCR4的下一个节拍到地址0x24。

T1-T3 主机向地址0x28插入一个BUSY传输。从机插入HREADYOUT = LOW的等待状态。

T3-T4 主机改变传输类型到SEQ,启动突发的下一拍到地址0x28。

T4-T5 HREADY LOW时,主机必须保持HTRANS恒定。

T5-T6 HREADY HIGH时,到地址0x24这一拍完成。

T6-T7 INCR4向地址0x28传输的第三个节拍完成,主机开始向地址0x2C传输的最后一个节拍。

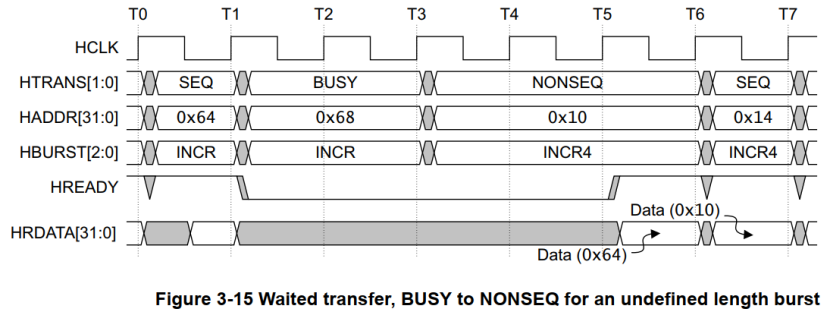

BUSY传输, 未定义长度突发

在一个未定义长度的突发(INCR)等待传输期间,当HREADY为LOW时,允许主机从BUSY切换到任何其他传输类型。如果SEQ传输被执行,突发将继续,但是如果IDLE或NONSEQ传输被执行,突发将终止。

图3-15显示了一个未定义长度突发的等待传输,传输类型从BUSY转换为NONSEQ。

在图3-15中:

T0-T1 主机启动INCR突发的下一拍到地址0x64。

T1-T3 主机插入BUSY传输到地址0x68。从机插入HREADYOUT = LOW的等待状态。

T3-T4 主机改变传输类型为NONSEQ,并且启动一个新的突发到地址0x10。

T4-T6 HREADY LOW时,主机必须保持HTRANS恒定。

T5-T6 未定义长度的突发以HREADY HIGH结束,master开始第一个节拍到地址0x10。

T6-T7 INCR4向地址0x10传输的第一个节拍完成,主机开始向地址0x14传输的下一个节拍。

3.6.2 Address changes during wait states

当从机处于请求等待状态时,主机只能修改一次地址,除非有如下描述:

– 在IDLE传输期间。

– 在3-43页的错误响应后。

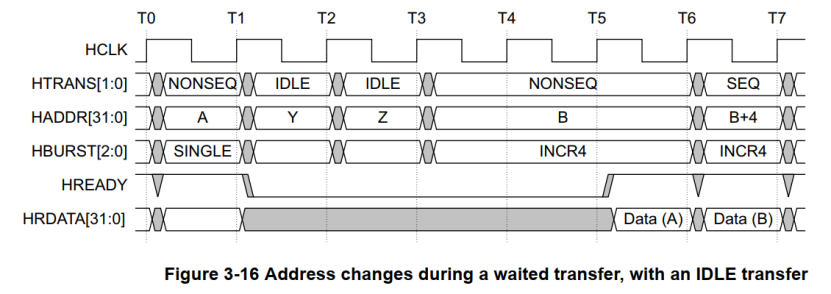

在IDLE传输期间

在等待传输期间,允许主机为IDLE传输更改地址。当HTRANS传输类型改变为NONSEQ时,主机必须保持地址不变,直到HREADY为HIGH。

图3-16所示为SINGLE突发等待传输,在IDLE传输过程中地址发生了变化。

在图3-16:

T0-T1 主机启动一个SINGLE突发到地址A。

T1-T2 主机插入一个IDLE传输到地址Y。从机插入一个HREADYOUT = LOW的等待状态。

T2-T3 主机插入一个IDLE传输到地址Z。

T3-T4 主机将传输类型更改为NONSEQ,并向地址B发起INCR4传输,直到HREADY达到HIGH,不再允许地址更改。

T5-T6 到地址A的SINGLE突发以HREADY HIGH结束,主机开始到地址B的第一拍。

T6-T7 INCR4向地址B传输的第一个节拍完成,主机开始向地址B+4传输的下一个节拍。

在错误响应之后

在一个等待的传输过程中,如果从机响应一个ERROR响应,那么当HREADY为LOW时,主机被允许改变地址。关于ERROR响应的更多信息,请参见5-57页的ERROR响应。

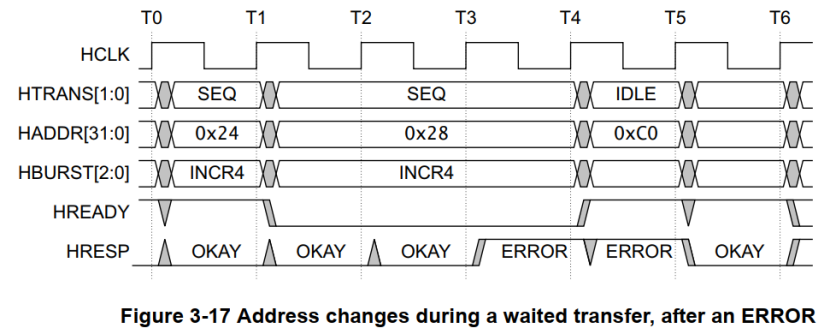

图3-17显示了一个等待的传输,地址改变后,从站的错误响应。

在图3-17:

T0-T1 主机启动突发的下一拍到地址0x24。

T1-T3 主机启动突发的下一拍到地址0x28。从机以OKAY响应。

T3-T4 从机以ERROR响应。

T4-T5 当HREADY为LOW时,主机改变传输类型为IDLE,并且允许改变地址。从机完成ERROR响应。

T5-T6 从机在地址0xC0以OKAY响应。

3.7 Protection control

本规范的版本A定义了一个4bit的HPORT信号,这个信号在这一部分描述。

本规范的版本B增加了扩展内存类型,在3-45页的内存类型中有更详细的描述。

Note

HPROT[3]的名称在本规范的Issue A和Issue B之间发生了变化,但定义保持不变。在Issue A中HPROT[3]被指定为可缓存的,在Issue B中被指定为可修改的。

保护控制信号,HPROT[3:0],提供关于总线访问的附加信息,主要用于实现某种级别保护的任何模块。

信号指示此传输是否是:

– 一种操作码提取或数据存取。

– 特权模式访问或用户模式访问

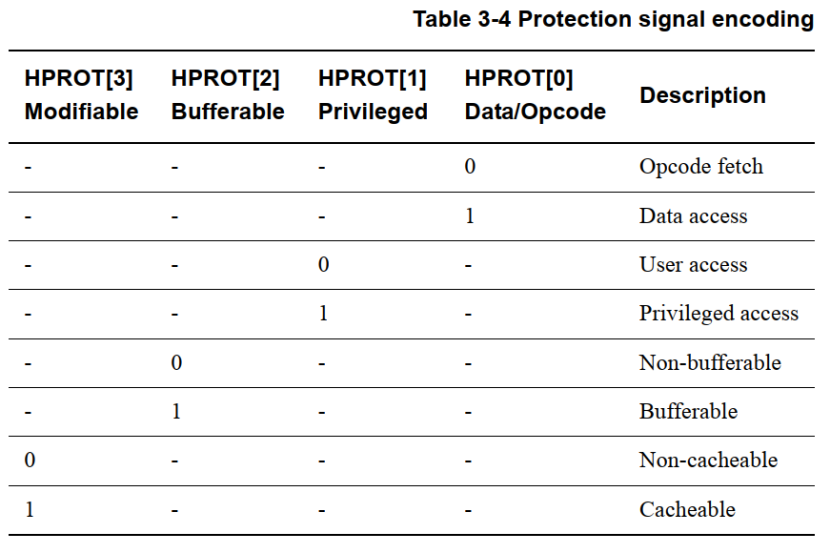

对于具有内存管理单元的主机,这些信号还表明当前访问是可缓存的还是可缓冲的。HPROT信号编码如表3-4所示。

表3-4保护信号编码

Note

许多主机无法生成准确的保护信息。如果主机无法生成准确的保护信息,本规范建议:

– 主节点将HPROT设置为0b0011,以对应非缓存、非缓冲、特权的数据访问。

– 除非绝对必要,从机不会使用HPROT。

HPROT控制信号与地址总线具有完全相同的时序。然而,它们必须在整个突发传输过程中保持恒定。

3.8 Memory types

AHB5定义了Extended_Memory_Types属性。此属性定义接口是否支持本节中描述的扩展内存类型。如果没有定义此属性,则接口不支持扩展内存类型

该规范的这一版本增加了额外的HPROT信号,并为每种内存类型提供了更详细的需求列表。

每个HPROT位的含义如表3-5所示,第3-46页的表3-6给出了HPROT[6:2]与内存类型的对应关系。

Table 3-5 Meaning of the HPROT bits

| Bit | Name | Description |

|---|---|---|

| HPROT[0] | Data/Inst | 当有效时,这个位表示传输是一个数据访问。当无效时,该位表示转移是指令取回。 |

| HPROT[1] | Privileged | 当有效时,此位表示传输是特权访问。当无效时,该位表示传输是无特权访问。 |

| HPROT[2] | Bufferable | 如果HPROT[4:3]都无效时,那么当该位为:1.无效,写响应必须从最终目的地给出。2.有效, 写响应可以从中间点给出,但写传输必须及时地在最终目的地可见。 |

| HPROT[3] | Modifiable | 当生效时,传输的特征可以被修改。当无效时,传输的特征不可被修改。 |

| HPROT[4] | Lookup | 当生效时,传输必须在缓存中查找。当无效时,传输不需要在缓存中查找,并且传输必须传播到最终目的地。 |

| HPROT[5] | Allocate | 当生效时,出于性能原因,该规范建议在缓存中分配此传输。当无效时,出于性能原因,该规范建议不在缓存中分配此传输。 |

| HPROT[6] | Shareable | 当有效时,表示这个转移是到与系统中其他主机共享的内存区域。在传输对其他主机可见之前,不能提供对传输的响应。当无效时,表示此传输是不可共享的,该内存区域不与系统中的其他主机共享。对传输的响应并不保证传输对其他主机是可见的。 |

3.8.1 Data or Instruction

所有传输包括数据或指令保护位HPROT[0]:

-当生效时,此位表示这个传输是数据访问。

-当无效时,该位表示传输是指令存取。

协议将此指示定义为提示。它并不是在所有情况下都是准确的,例如,当一个事务包含指令和数据项的混合时。

本规范建议主机将HPROT[0]设置为HIGH,以指示数据访问,除非该访问是明确知道的指令访问。

3.8.2 Unprivileged or Privileged

所有传输包括特权或非特权保护位,HPROT[1]:

– 当生效时,该位表示传输是特权访问。

– 当无效时,该位表示传输为非特权访问。

Note

有些处理器支持多种级别的特权,请参阅所选处理器的文档来确定到AHB特权级别的映射。所提供的唯一区别是特权访问和非特权访问。

3.8.3 Memory type

本节提供了关于HPROT保护控制信号的附加信息,以及这些信号如何与不同的内存类型相关联。HPROT[6:2]信号与内存类型的对应关系如表3-6所示。不允许表3-6中未显示的组合位。

设备内存类型E后缀表示允许提前写响应。

设备内存类型nE后缀表示不允许提前写响应,写响应必须来自最终目的地。

下面几节详细介绍每种内存类型的需求。

3.8.4 Device memory requirements

对于所有的设备内存,即“Device- nE”和“Device-E”,需要的行为为:

– 读数据必须从最终目的地获得。

– 传输不能分隔为多次传输,或与其它传输合并。

– 读取不能预取或推测的执行。

– 写不能被合并。

– 从同一主服务器到同一从服务器的所有读和写传输必须保持顺序。

– 传输的大小,如HSIZE所示,不能更改。

– 传输的突发可以被分解成若干个较小的突发。但是,原始突发中NONSEQ和SEQ传输的总数必须与由此产生的较小突发中NONSEQ和SEQ传输的总数相同。

– HPROT允许的惟一更改是将传输从Bufferabe转换为Non-bufferable。

此外, 对Device-nE:

– 写响应必须从最终目的地获得。

此外, 对Device-E:

– 写响应可以从中间点获得。

– 写传输必须在给出写响应时对所有其他主机都是可观察的。

– 写传输必须及时到达最终目的地。

3.8.5 Normal memory requirements

对于所有普通内存,即Normal Non-cacheable内存、Write-through和Write-back,所需的行为是:

– 读取可能是推测的。

– 读取可以获取比需要的更多的数据。

– 写可以被合并。

– 如HBURST和HSIZE所示,传输特性是可以改变的。

– 从同一个主服务器到重叠地址的读写传输必须保持有序。

– 对于可共享事务,响应必须只在传输对所有其他主机可见时才给出。

此外, 对于Normal Non-cacheable内存:

1写传输必须在最终目的地及时可见。

Note

没有机制来确定写传输何时到达最终目的地。

2 读数据必须获得从:

– 最终目的地。

– 正在进行到最终目的地的写传输。

3 如果读数据从写传输获取:

– 它必须从写操作的最新版本中获取。

– 数据不能缓存为以后的读取服务。

4 读取操作不能缓存获得的数据以供以后使用。

Note

对于一个Normal Non-cacheable内存,读数据可以从一个仍在向最终目的地前进的写传输中获得,这与同时传播到最终目的地的读和写传输是不可区分的。 以这种方式返回的读数据并不表示写传输在最终目的地是可见的。

此外, 对于Write-through:

– 写响应可以从中间缓存或缓冲区获得。

– 读数据可以缓存在中间的缓存或缓冲区中。

– 读写传输需要缓存查找。

– 写事务必须及时地在最终目的地可见。

Note

没有机制来确定写事务何时在最终目的地是可见的。

此外,对于Write-back:

– 写响应可以从中间缓存或缓冲区获得。

– 读数据可以缓存在中间的缓存或缓冲区中。

– 读写传输需要缓存查找。

– 写事务不需要在最终目的地可见。

3.8.6 Allocate attribute

Write-through和Write-back传输包括分配属性, HPROT[5]:

– 当生效时,出于性能原因,此规范建议在缓存中分配此传输。

– 当无效时,出于性能原因,该规范建议在缓存中不分配此传输。

3.8.7 Legacy Considerations

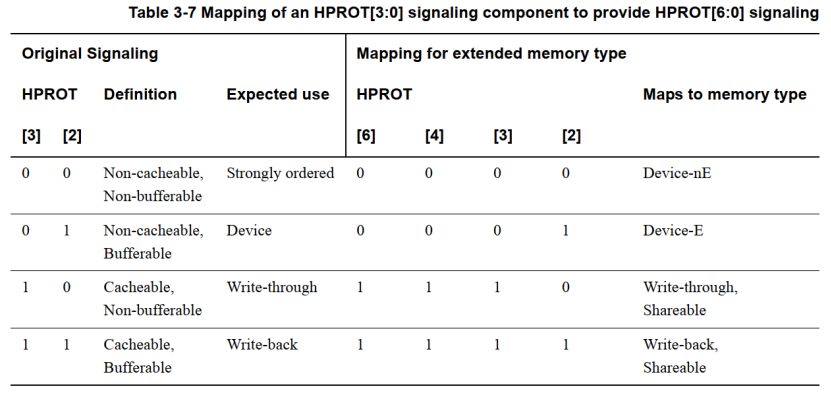

表3-7显示了本规范建议为仅包含HPROT[3:0]信号的组件提供HPROT[6:0]信号的映射。

当在只包含HPROT[3:0]的系统中使用支持HPROT[6:0]的组件时,高阶HPROT位可以被移除。

Note

这种方法导致了Non-cacheable 内存到 Non-cacheable内存的映射。但是,可以使用另一种方案,特别是在提供了其他信息以确定更合适的映射时。.