SDRAM(synchronous dynamic random access memory),同步动态随机存储器,所谓同步就是指需要时钟信号来控制命令数据,动态是指存储阵列需要不断地刷新来保证数据不会丢失,随机是指存取数据可以根据需要在不同地址上进行,不需要像FIFO一样只能线性存储。

操作芯片选型;Winbond的W9825G6KH。

一、SDRAM操作流程

1.芯片初始化,

SDRAM上电之后需要一段初始化的过程,以保证芯片按照需要进行正常工作,初始化过程如下:

上电200us稳定期,所有Bank预充电,8个自动刷新周期,模式寄存器设置周期,8个总动刷新周期

2.芯片工作状态

行激活,列写/读,数据输入/输出,突发模式,预充电,刷新,

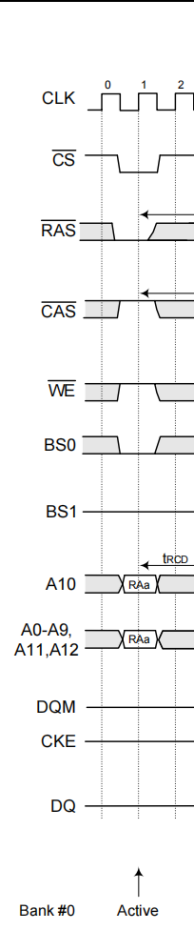

2.1行激活

在执行任何读写操作之前,必须先激活SDRAM中的一行此时将片选信号#CS置为低电平,#RAS置为低电平、#CAS置为高电平,同时地址端口给出地址信号用来选中某一L-Bank的某一行。

行激活指令又名Bank Active,从翻译上看是对L-Bank进行激活,实际上是对具体某一L-Bank中的某一行进行激活,所以一般会直接说成行激活。

2.2列写/读

在行激活后,经过tRCD延迟后通过将#RAS置为高电平、#CAS低电平来进行写/读操作,同时地址端口给出地址信号用来选中被激活行中的具体某一列,即选中存储阵列中的单元此时#WE置为低电平时为写操作,#WE置为高电平时为读操作。

tRCD这一段时间可产看具体芯片的数据手册,一般会给出最小时间,在程序编写时只需要略大于这个时间即可。

注意:在SDRAM中行列地址是共用的,#RAS为低电平时地址线上的地址数据认为是行地址数据,#CAS为低电平时地址线上的地址数据认为是列地址数据。

2.3 数据输入/输出

2.3.1数据输入(写操作)

在列地址被选通的同时,数据端口给出数据,即进行写操作,但此时数据并没有立即写入存储单元,在经过tWR延迟后,数据才被真正写入存储单元,在W9825G6KH中tWR为2个时钟周期。

注意:在下一次读写命令开始前,即下一次行激活前,实际上还存在预充电周期tRP,这一段时间可产看具体芯片的数据手册,一般会给出最小时间,在程序编写时只需要略大于这个时间即可。

2.3.2数据输出(读操作)

在选定列地址后,就已经确定了具体的存储单元,接下来就是数据到达数据端口,但是在CAS发出之后,要经过一定的时间才能有数据输出,从 CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS潜伏期),通过设置模式寄存器MR给出具体的CL时钟周期。

2.4 突发模式

由于CL的存在,导致在CL期间无法进行其他操作,浪费了时间和资源,于是突发模式诞生,突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(Burst Lengths,简称BL)。

事实上,实际对SDRAM操作时,很少会对单一的存储单元进行读写,而是对连续的存储空间进行读写操作,那么突发模式是如何操作的呢?

只需要指定起始列地址和突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址,BL的宽度通过设置模式寄存器MR具体给出。

2.5 预充电

在对SDRAM某一存储地址进行读写操作结束后,如果要对同一L-Bank的另一行进行寻址,就要将原来有效(工作)的行关闭,重新发送行/列地址。L-Bank关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。在读写过程中,工作行内的存储体由于“行激活”而使存储电容受到干扰,因此在关闭工作行前需要对本行所有存储体进行重写。预充电实际上就是对工作行中所有存储体进行数据重写,并对行地址进行复位,以准备新行工作的过程。

预充电包括自动预充电和预充电两种。

2.5.1 自动预充电

如果在发出读或写命令时 将地址位的某一位设置为高电平(W9825G6KH为A10),则进入自动预充电功能。

若为读操作,在自动预充电期间,读取命令将照常执行,但激活行将在所有突发读取周期完成之前自动开始预充电。无论突发长度如何,都会在突发读结束后的一定数量的时钟进行自动开始预充电,时钟数等于CL的时钟数。

若为写操作,SDRAM 在突发写入周期后经过两个时钟延迟后才能自动进入预充电操作。此延迟称为写入 tWR。在满足 tWR 和 tRP 之前,无法重新激活正在进行 Auto-precharge 的 bank。这称为 tDAL,即数据输入到活动延迟 (tDAL = tWR + tRP)。使用自动预充电命令时,行激活命令和内部预充电操作开始之间的间隔必须满足 tRAS (min)。

2.5.2 预充电

与自动预充电不同的是预充电是在读写操作后对控制端口进行高低电平控制后手动进行预充电,当 #CS、 #RAS 和 #WE 为低电平且 #CAS为高电平进入预充电。预充电命令可用于单独预充电每个 Bank 或同时预充电所有 Bank。三个地址位 A10、BS0和BS1用于定义在发出命令时要对哪些Bank进行预充电。预充电命令和下一次行激活命令之间的延迟必须大于等于预充电时间 tRP。

2.6 刷新

SDRAM之所以称为同步“动态”随机存储器,就是因为它要不断进行刷新才能保留住数据,因此刷新是SDRAM最重要的操作。刷新电包括自动预刷新和自刷新两种。

2.6.1自动刷新(AR)

对于自动刷新,SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址。在自动刷新过程中,所有L-Bank都停止工作。每次刷新操作所需要的时间为自动刷新周期 (tRC),在自动刷新指令发出后需要等待tRC才能发送其他指令。显然,刷新操作肯定会对SDRAM的性能造成影响,但这是没办法的事情,也是DRAM相对于SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。

通过将CKE、#WE置为高电平,将#CS、#RAS、#CAS置为低电平即为自动刷新模式。

注意:tRC数据手册中查到,需要注意的是要将所有的行在tRC时间段内完成刷新,比如W9825G6KH行地址为A0-A12共8192行。

2.6.2 自刷新(SR)

自刷新(SR)主要用于休眠模式低功耗状态下的数据保存,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新将CKE置为高电平才能退出自刷新模式并进入正常工作状态。

通过将#WE置为高电平,将CKE、#CS、#RAS、#CAS置为低电平即为自刷新模式。