51单片机的组成

(1)8位微处理器(CPU)

(1)8位微处理器(CPU)

(2)数据存储器(128B RAM)

(3)程序存储器(4KB Flash ROM)

(4)4个8位并行I/O口(P0口~P3口)

(5)1个全双工异步串口

(6)2个16位定时器/计数器

(7)1个看门狗定时器

(8)中断系统:5个中断源、5个中断向量;

(9)特殊功能寄存器(SFR)26个;

(10)低功耗的空闲模式和掉电模式;

(11)3个程序加密位;

优点

相比AT89C51,AT89S51有

(1)增加在线可编程功能ISP功能(In System Program),现场程序调试和修改更加方便灵活

(2)数据指针2个,方便对片外RAM的访问过程

(3)看门狗定时器,提高系统抗干扰能力

(4)增加断电标志;

(5)增加掉电状态下的中断恢复模式;

各部件的功能

- CPU(微处理器)

8位,包括运算器和控制器两部分,还有位处理功能。 - 数据存储器(RAM)

128B(52子系列为256B),最多可扩64KB。片内RAM为高速RAM,可加快速度和降低功耗。 - 程序存储器(Flash ROM)

4KB Flash(AT89S52 则为8KB;AT89C55片内20KB),如不够,片外可外扩至64KB。 - 中断系统

5个中断源,2级中断优先权。 - 定时器/计数器

2个16位定时器/计数器(52子系列有3个),4种工作方式。 - 1个看门狗定时器WDT

当CPU由于干扰使程序陷入死循环或跑飞时,WDT可使程序恢复正常运行。 - 串行口

全双工异步串行口,4种工作方式。可进行串行通信,扩展并行I/O口,可与多个单片机构成多机系统。 - P1口、P2口、P3口、P0口:4个8位并行I/O口。

- 特殊功能寄存器(SFR)

26个,对片内各功能部件管理、控制和监视。是各功能部件的控制寄存器和状态寄存器,映射在片内RAM区80H~FFH内。

引脚的功能

1.电源引脚

(1)VCC(40脚):+5V电源。

(2)VSS(20脚):数字地。

左下脚接地,右上脚接电源

2.时钟引脚

(1)XTAL1(19脚)

输入端。使用片内振荡器时,应接外部石英晶体和微调电容。外接时钟源时,该脚接外部时钟振荡器输出的信号。

(2)XTAL2(18脚):

片内振荡器反相放大器的输出端。

- 使用片内振荡器,该脚连接外部石英晶体和微调电容。

- 当使用外部时钟源时,本脚悬空。

3. 控制引脚

(1)RST (RESET,9脚)

复位信号输入端

单片机要想复位,需要在RST加持续时间大于2个机器周期的高电平,可使单片机复位。

正常工作应≤0.5V。

当看门狗定时器溢出输出时,该脚将输出长达96个时钟振荡周期的高电平。

(2)EA*/VPP (31脚)

- EA*:第一功能:允许访问外部程序存储器控制。

- EA*=1

PC值≤0FFFH时,单片机读片内4KB Flash中的程序,

PC值 >0FFFH (超出片内4KB Flash地址范围)时,转向读取片外60KB(1000H-FFFFH)程序存储器空间中的程序。 - EA*=0

只读取外部的程序存储器中的内容,读取地址范围0000H~FFFFH,片内4KB Flash无效。

- EA*=1

- VPP:第二功能,对片内Flash编程,接编程电压。

(3)ALE/PROG*(30脚)

-

ALE:第一功能

为访问外部存储器提供低8位地址锁存信号,将低8位地址锁存在片外地址锁存器中。 -

PROG*:第二功能

对片内 Flash编程的编程脉冲输入

4. 并行I/O端口

剩下的32个引脚都是并行I/O口引脚

p0,p1,p2,p3共四个引脚,每个引脚8位

4个8位并行I/O端口,为P0、P1、P2和P3。

输出锁存器属特殊功能寄存器。

端口组成:每位均由输出锁存器、输出驱动器和输入缓冲器组成,

4个端口均可位寻址。

P0口

8位,漏极开路的双向 I/O口

漏极开路意味着有一个高阻态

可作为系统总线低8位地址总线及数据总线分时复用端口。

也可作通用I/O口,需加上拉电阻,这时为准双向口。如作通用I/O输入,应先向端口写入1,可驱动8个LS型TTL负载。

双功能的8位并行端口,字节地址为80H,位地址为80H~87H。

电路结构

P0口位电路包括:

(1)1个数据输出的锁存器。

(2)2个三态的数据输入缓冲器,分别是用于读锁存器数据的输入缓冲器BUF1和读引脚数据的输入缓冲器BUF2。

(3)1个多路转接开关 MUX,它的一个输入来自锁存器的 Q*端,另一个输入为地址/数据信号的反相输出。MUX由“控制”信号控制,实现锁存器输出和地址/数据信号间转接。

(4)数据输出的控制和驱动电路,由2个场效应管(FET)组成。

工作过程

(1)P0口用作地址/数据总线

P0口作为复用的地址/数据总线使用。

当作为地址或数据输出时,“控制”信号为1,硬件自动使转接开关MUX打向上面,接通反相器的输出,同时使“与门” 开启。

当输出的地址/数据信息=1,“与门”输出为1,上方场效应管导通,下方场效应管截止,P0.x引脚输出为1

当输出的地址/数据信息=0,上方场效应管截止,下方场效应管导通,P0.x引脚输出为0。

由上、下两个场效应管形成的推拉式结构,大大提高负载能力,上方的场效应管这时起到内部上拉电阻的作用。

当P0口作为数据输入时,仅从外部引脚读入信息, “控制”信号为0,MUX接通锁存器Q*端。

P0口作为地址/数据复用方式访问外部存储器时,CPU自动向P0口写入FFH,使下方场效应管截止,上方场效应管由于控制信号为0也截止,从而保证数据信息的高阻抗输入,从外部输入的数据直接由P0.x引脚通过输入缓冲器BUF2进入内部总线。

具有高阻抗输入的I/O口应具有高电平、低电平和高阻抗3种状态的端口。因此,P0口作为地址/数据总线使用时是真正的双向端口,简称双向口。

(2)P0口用作通用I/O口

对应的“控制”信号=0,MUX打向下面,接通锁存器的Q端,“与门”输出为0,上方场效应管截止,形成的P0口输出电路为漏极开路输出。

P0口作输出口时,CPU的“写”脉冲加在D锁存器的CP端,内部总线上的数据写入D锁存器,并由引脚P0.x输出。

当D锁存器为1时, Q端为0,下方场效应管截止,输出为漏极开路,此时,必须外接上拉电阻才能有高电平输出;当D锁存器为0时,下方场效应管导通,P0口输出为低电平。

P0口作I/O输入使用时,两种读入方式:“读锁存器”和“读引脚”。

当CPU发出**“读锁存器”指令时,锁存器的状态由Q端经上方的三态缓冲器BUF1进入内部总线;

当CPU发出“读引脚”指令**时,锁存器的输出状态Q=1(Q*端为0),而使下方场效应管截止,引脚的状态经下方的三态缓冲器BUF2进入内部总线。

p0口总结

双功能口――地址/数据复用口和通用I/O口

(1)当用作地址/数据复用口时,为真正双向口

(2)当P0口用作通用I/O口时,需在片外接上拉电阻,端口不存在高阻(悬浮)状态,是一准双向口。

为保证正确读入引脚,应先向锁存器写1。

单片机复位后,锁存器自动被置1;

P0口大多作地址/数据复用口,就不能再作通用I/O口使用。

P1口

8位,准双向I/O口,具有内部上拉电阻。

准双向I/O口,作为I/O输入时,应先向端口锁存器写1

p1口电路结构:

仅作I/O口,字节地址为90H,位地址为 90H~97H。

1.位电路结构

P1口位电路结构由以下3部分组成:

(1)数据输出位输出锁存器。

(2)2个三态的数据输入缓冲器BUF1和BUF2,控制读锁存器数据和读引脚数据。

(3)数据输出驱动电路,由一个场效应管(FET)和一个片内上拉电阻组成。

2.工作过程分析

P1口只作为通用I/O口。

(1)作输出时:

若CPU输出1,Q=1,Q*=0,场效应管截止,P1.x脚输出为1

若CPU输出0,Q=0,Q*=1,场效应管导通,P1.x脚输出为0

(2)作输入口时,分为“读锁存器”和“读引脚” 。

“读锁存器”,输出Q状态经输入缓冲器BUF1进入内部总线;

“读引脚”,先向锁存器写1,使场效应管截止,P1.x引脚上的电平经输入缓冲器BUF2进入内部总线。

3.P1口的特点

由于内部有上拉电阻,无高阻抗输入状态,故为准双向口。

P1口“读引脚”输入时,必须先向锁存器写入1。

P2口

8位,准双向I/O口,具有内部上拉电阻。

当外扩存储器及I/O口时,P2口输出高8位地址。

P2口也可作为通用I/O使用。当作输入时,应先向端口输出锁存器写1。

可驱动 4个LS型TTL负载。

双功能口,字节地址为A0H,位地址为A0H~A7H。

P2口位电路结构

1.位电路结构

P2口某一位的电路包括:

(1)1个数据输出锁存器,用于输出数据的锁存。

(2)2个三态数据输入缓冲器BUF1和BUF2,分别用于读锁存器数据和读引脚数据的输入缓冲。

(3)1个多路转接开关MUX,一个输入是锁存器的Q端,另一个输入是高8位地址。

(4)输出驱动电路,场效应管+内部上拉电阻。

2.工作过程分析

(1)P2口用作地址总线

在控制信号作用下,MUX与 “地址”接通。当“地址”为0时,场效应管导通,P2口引脚输出0;当“地址”线为1时,场效应管截止,P2口引脚输出1。

(2)P2口用作通用I/O口

在内部控制信号作用下,MUX与锁存器Q端接通。

CPU输出1时,Q=1,场效应管截止,P2.x引脚输出1;

CPU输出0时,Q=0,场效应管导通,P2.x引脚输出0。

P2口输入时,分“读锁存器”和“读引脚”两种方式:

“读锁存器”时,Q端信号经输入缓冲器BUF1进入内部总线

“读引脚”时,先向锁存器写1,使场效应管截止,P2.x引脚上的电平经输入缓冲器BUF2进入内部总线。

3.P2口的特点

作为地址输出线时,P2输出高8位地址,P0输出低8位地址寻址64KB地址空间。

作为通用I/O口时,P2口为准双向口。功能与P1口一样。

一般情况下,P2口大多作为高8位地址总线口使用,这时就不能再作为通用I/O口使用。

P3口

8位,准双向I/O口,具有内部上拉电阻。

可作为通用I/O口使用。如作通用I/O输入,应先向端口输出锁存器写入1。可驱动4个LS型TTL负载。

P3口还可提供第二功能,定义如表2-1,应熟记。

由于引脚数目有限,P3口增加第二功能。每1位都可分别定义为第二输入/输出功能。P3口字节地址B0H,位地址B0H~B7H。

P3口的位电路结构

1.位电路结构

P3口位电路包括:

(1)1个数据输出锁存器,锁存输出数据位。

(2)3个三态数据输入缓冲器BUF1、BUF2和BUF3,分别用于读锁存器、读引脚数据和第二功能数据的输入缓冲。

(3)输出驱动,由“与非门”、场效应管(FET)和内部上拉电阻组成。

2.工作过程分析

(1)P3口用作第二输入/输出功能

当选择第二输出功能时,该位的锁存器需要置“1”,使“与非门”为开启状态。

当第二输出为1时,场效应管截止,P3.x引脚输出为1;

当第二输出为0时,场效应管导通,P3.x引脚输出为0。

当选择第二输入功能时,该位的锁存器和第二输出功能端均应置1,保证场效应管截止,P3.x引脚的信息由输入缓冲器BUF3的输出获得。

(2)P3口用作第一功能――通用I/O口

用作第一功能通用输出时,第二输出功能端应保持“1”,“与非门” 开启。CPU输出1时,Q=1,场效应管截止,P3.x引脚输出为1;CPU输出0时,Q=0,场效应管导通,P3.x引脚输出为0。

用作第一功能通用输入时,P3.x位的输出锁存器和第二输出功能均应置1,场效应管截止,P3.x引脚信息通过输入BUF3和BUF2进入内部总线,完成“读引脚”操作。

当P3口第一功能通用输入时,也可执行“读锁存器”操作,此时Q端信息经过缓冲器BUF1进入内部总线。

3.P3口的特点

P3口内部有上拉电阻,无高阻抗输入态-准双向口。P3口作为第二功能的输出/输入,或第一功能通用输入,均须将相应位的锁存器置1。实际应用中,由于复位后P3口锁存器自动置1,满足第二功能所需的条件,所以不需要任何设置工作,就可以进入第二功能操作。

当某位不作为第二功能用时,可作为第一功能通用I/O使用。

引脚输入部分有两个缓冲器,第二功能的输入信号取自缓冲器BUF3的输出端,第一功能的输入信号取自缓冲器BUF2的输出端。

时钟电路与时序

时钟电路产生必需的控制信号,严格按时序执行指令。

执行程序时,CPU首先取指令,然后译码,由时序电路产生一系列控制信号完成规定的操作。

CPU时序信号两类:

(1)对片内各个功能部件控制,用户无须了解;

(2)对片外存储器或I/O端口的控制,这部分时序对分析、设计硬件接口电路至关重要。

时钟电路设计

时钟频率直接影响单片机运行速度,电路质量直接影响单片机系统的稳定性。常用的时钟电路有两种方式,一种是内部时钟方式,另一种是外部时钟方式。

- 内部时钟方式

AT89S51内部有一个用于构成振荡器的高增益反相放大器,输入端为芯片引脚XTAL1,输出端为引脚XTAL2。这两个引脚跨接石英晶体振荡器和微调电容,构成一个稳定的自激振荡器,如下图AT89S51内部时钟方式的电路。

C1和C2的典型值通常选择为30pF。

电容大小会影响振荡器频率高低、振荡器的稳定性和起振的快速性。

晶振频率范围通常是1.2~12MHz。频率越高,单片机速度就越快。速度快对存储器的速度要求就高,印制电路板的工艺要求也高,即线间寄生电容要小。晶体和电容应尽可能与单片机靠近,以减少寄生电容,保证振荡器稳定、可靠工作。为提高温度稳定性,采用温度稳定性能好的电容。

常选6MHz或12MHz的石英晶体。随着集成电路制造技术的发展,单片机的时钟频率也在逐步提高,已达33MHz。

- 外部时钟方式

用现成的外部振荡器产生脉冲信号,常用于多片AT89S51同时工作,便于多片AT89S51同步,一般为低于12MHz的方波。

外部时钟源接到XTAL1端,XTAL2端悬空,如图

- 时钟信号的输出

当使用片内振荡器,XTAL1、XTAL2引脚还能为应用系统中的其他芯片提供时钟,但需增加驱动能力。其引出的方式有两种,如图

机器周期、指令周期与指令时序

各种指令时序与时钟周期相关。

- 时钟周期

时钟控制信号的基本时间单位。

若晶振频率为fosc,则时钟周期Tosc=1/fosc。如fosc=6MHz,Tosc=166.7ns。 - 机器周期

CPU 完成一个基本操作所需时间为机器周期。

执行一条指令分为几个机器周期。每个机器周期完成一个基本操作,如取指令、读或写数据等。每12个时钟周期为1个机器周期

1个机器周期包括12个时钟周期,分6个状态:S1~S6。每个状态又分两拍:P1和P2。因此,一个机器周期中的12个时钟周期表示为S1P1、S1P2、S2P1、S2P2、…、S6P2,如图

- 指令周期

执行一条指令所需的时间。

简单的单字节指令,取出指令立即执行,只需一个机器周期的时间。而有些复杂的指令,如转移、乘、除指令则需两个或多个机器周期。

从指令执行时间看:

- 单字节和双字节指令一般为单机器周期和双机器周期;

- 3字节指令都是双机器周期;

- 乘、除指令占用4个机器周期。

指令周期

执行一条指令所需的时间。

简单的单字节指令,取出指令立即执行,只需一个机器周期的时间。而有些复杂的指令,如转移、乘、除指令则需两个或多个机器周期。

从指令执行时间看:

单字节和双字节指令一般为单机器周期和双机器周期;

3字节指令都是双机器周期;

乘、除指令占用4个机器周期。

复位操作和复位电路

单片机初始化操作,给复位脚RST加上大于2个机器周期(即24个时钟振荡周期)的高电平就使AT89S51复位。

复位操作

复位时,PC初始化为0000H,程序从0000H单元开始执行。

除系统正常初始化外,当程序出错(如程序跑飞)或操作错误使系统处于死锁状态时,需按复位键使RST脚为高电平,使AT89S51摆脱“跑飞”或“死锁”状态,而重新启动程序。

复位操作还对其他一些寄存器有影响,这些寄存器复位时的状态如表2-7。

由表2-7,复位时,SP=07H ,而P0~P3引脚均为高电平。

在某些控制应用中,要注意考虑P0~P3引脚的高电平对接在这些引脚上的外部电路的影响。

例如,当P1口某个引脚外接一个继电器绕组,当复位时,该引脚为高电平,继电器绕组就会有电流通过,就会吸合继电器开关,使开关接通,可能会引起意想不到的后果。

CPU

由运算器和控制器构成。

运算器

功能:对操作数进行算术、逻辑和位操作运算。

组成:算术逻辑运算单元ALU、累加器A、位处理器、程序状态字寄存器PSW及两个暂存器等。

1.算术逻辑运算单元ALU

可对8位变量逻辑运算(与、或、异或、循环、求补和清零),还可算术运算(加、减、乘、除)

ALU还有位操作功能,对位变量进行位处理,如置“1”、清“0”、求补、测试转移及逻辑“与”、“或”等。

2.累加器A

使用最频繁的寄存器,可写为Acc。“A”与“Acc”书写的差别,将在第3章介绍。

作用如下:

(1)ALU单元的输入数据源之一,又是运算结果存放单元。

(2)数据传送多通过A,数据中转站。为解决“瓶颈堵塞”问题,AT89S51增加了一部分可不经过累加器的传送指令。

A进位标志Cy是同时又是位处理机的位累加器

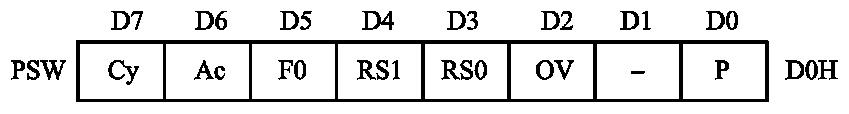

3.程序状态字寄存器PSW

PSW位于片内特殊功能寄存器区,字节地址为D0H。

包含程序运行的状态信息,其中4位保存当前指令执行后的状态,供查询和判断。

特殊功能寄存器在内存中的位置:80H~FFH

PSW格式:

特殊功能寄存器PSW各位功能:

(1)Cy(PSW.7)进位标志位

可写为C。在算术和逻辑运算时,若有进位/借位,Cy=1;否则,Cy=0。在位处理器中,它是位累加器。

(2)Ac(PSW.6)辅助进位标志位

在BCD码运算时,用作十进位调整。即当D3位向D4位产生进位或借位时,Ac=1;否则,Ac=0。

(3)F0(PSW.5)用户设定标志位

由用户使用的一个状态标志位,用指令使它置“1”或清“0,控制程序流向,应充分利用。

(4)RS1、RS0(PSW.4、PSW.3)4组工作寄存器区选择

选择片内RAM区中的4组工作寄存器区中的某一组为当前工作寄存区。

(5)OV(PSW.2)溢出标志位

当执行算术指令时,用来指示运算结果是否产生溢出。如溢出,OV=1;否则,OV=0。

(6)PSW.1位:保留位

(7)P(PSW.0):奇偶标志位

指令执行完,A中“1”的个数是奇数还是偶数。

P=1,A中“1”的个数为奇数。

P=0,A中“1”的个数为偶数。

此标志位对串行通信有重要意义,常用奇偶检验来检验数据串行传输的可靠性。

控制器

任务:识别指令,控制单片机各功能部件,保证各部分自动协调工作。

控制器包括:PC、指令寄存器、指令译码器、定时及控制逻辑电路等。

功能:控制指令的读入、译码和执行,对各功能部件进行定时和逻辑控制。

程序计数器PC 是一个独立的16位计数器,不可访问。单片机复位时,PC内容为0000H,从程序存储器0000H单元取指令,,执行程序。

PC工作过程:CPU取指令时,PC内容为所取指令的地址,程序存储器按此地址输出指令字节,同时PC自动加1。

存储器

存储器空间分为4类:

1. 程序存储器空间

- 片内和片外两部分。

- 片内4KB Flash ,编程和擦除完全是电气实现。可用通用编程器对其编程,也可在线编程。

- 当片内4KB Flash 存储器不够用时,可外扩,最多可扩展至64KB程序存储器。

- 51单片机中,当片内4k不够的时候可以外扩

存程序和表格的固定常数。

片内为4KB的Flash ,地址为0000H~0FFFH。16位地址线,外扩的程序存储器空间最大为64KB,地址为0000H~FFFFH。使用应注意:

- 片内和片外两部分,访问片内还是片外程序存储器,由EA*脚电平确定。

- EA*=1,CPU从片内0000H开始取指令,当PC值没有超出0FFFH时,只访问片内Flash ,当PC值超出0FFFH自动转向读片外程序存储器1000H~FFFFH 内的程序。

- EA*=0,不理会片内4KB Flash 存储器,只执行片外程序存储器(0000H~FFFFH)中的程序。

- 程序存储器5个固定单元为各中断源中断入口。

2.数据存储器空间

- 片内与片外两部分。

- 片内有128B RAM(52子系列为256B)。

- 片内RAM 不够用时,在片外可扩展至64KB RAM 。

- 片内和片外的空间地址一样,但是数据不会发生冲突, 因为访问片内和片外使用不同的指令

-

片内RAM

片内数据存储器(RAM)共128个单元,字节地址为00H~7FH。结构:

00H~1FH 4组通用工作寄存器区,每区包含8B,为R7~R0。可用指令改变RS1、RS0两位来选择。

20H~2FH的16个单元的128位可位寻址,也可字节寻址。

30H~7FH的单元只能字节寻址,用作存数据以及作为堆栈区。 -

片外数据存储器

当片内RAM不够用时,需外扩,最多可外扩64KB的RAM。

注意,片内RAM与片外RAM两个空间是相互独立的,片内RAM与片外RAM的低128B的地址是相同的,但由于使用的是不同的访问指令,所以不会发生冲突。

3.特殊功能寄存器SFR

各功能部件的控制寄存器及状态寄存器。

SFR综合反映了整个单片机基本系统内部实际的工作状态及工作方式。

映射在片内RAM的80H~FFH区域中,共26个,有些可位寻址。

与AT89C51相比,新增5个SFR:DP1L、DP1H、AUXR、AUXR1和WDTRST

凡是可位寻址的SFR,字节地址末位只能是0H或8H。

若读/写未定义单元,将得到一个随机数。

下面介绍部分SFR。

-

堆栈指针SP

指示栈顶在内部RAM中的位置。

堆栈向上生长。单片机复位后,SP为07H,堆栈从08H单元开始,由于08H~1FH单元分别是属于1~3组的工作寄存器区,最好在复位后把SP值改置为60H或更大的值,避免堆栈与工作寄存器冲突。

堆栈主要为子程序调用和中断操作而设。保护断点和现场

(1)保护断点。无论子程序调用还是中断服务子程序调用,最终都要返回主程序。应预先把主程序断点在堆栈中保护起来,为程序正确返回做准备。

(2)现场保护。执行子程序或中断服务子程序时,要用到一些寄存器单元,会破坏原有内容。要把有关寄存器单元的内容保存起来,送入堆栈,这就是所谓的“现场保护”。

两种操作:数据压入(PUSH)堆栈,数据弹出(POP)堆栈。 -

寄存器B

为执行乘和除而设。不执行乘、除的情况下,可把它当作一个普通寄存器来使用。

乘法,两乘数分别在A、B中,执行乘法指令后,乘积在BA中(高8位存到B里,低8位存到A里)

除法,被除数取自A,除数取自B,商存放在A中,余数存B中。 -

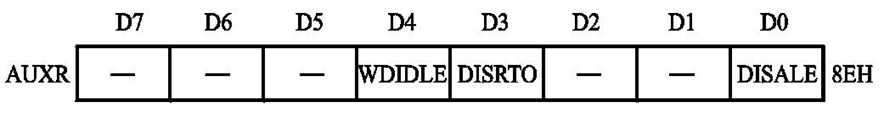

AUXR寄存器

AUXR是辅助寄存器

DISALE:ALE的禁止/允许位。

0:ALE有效,发出脉冲;

1:ALE仅在执行MOVC和MOVX类指令时有效,不访问外部存储器时,ALE不输出脉冲信号;

DISRTO:禁止/允许WDT溢出时的复位输出。

0:WDT溢出时,在RST引脚输出一个高电平脉冲;

1:RST引脚仅为输入脚。

WDIDLE:WDT在空闲模式下的禁止/允许位。

0: WDT在空闲模式继续计数;

1: WDT在空闲模式暂停计数。。 -

数据指针DPTR0和DPTR1

双数据指针寄存器,便于访问数据存储器。

DPTR0:AT89C51原有的数据指针,

DPTR1:新增加的数据指针。

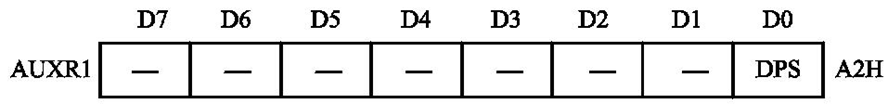

寄存器AUXR1的DPS位用于选择两个数据指针。

DPS=0,选用DPTR0;DPS=1,选用DPTR1。

可作为一个16位寄存器来用,也可作为两个独立的8位寄存器DP0H(或DP1H)和DP0L(或DP1L)来用。 -

AUXR1寄存器

为辅助寄存器,格式如图2-6:

DPS:数据指针寄存器选择位。

0:选择数据指针寄存器DPTR0;

1:选择数据指针寄存器DPTR1。

-

看门狗定时器WDT

WDT包含一个14位计数器和看门狗复位寄存器(WDTRST)。

WDT提供一种使程序恢复正常运行的有效手段。

有关WDT在抗干扰设计中的应用以及低功耗模式下运行的状态,将在相应章节具体介绍。

上面介绍的特殊功能寄存器,除SP和B以外,其余均为AT89S51在AT89C51基础上新增加的SFR。

4.位地址空间

211个寻址位的位地址,位地址范围为00H~FFH,其中00H~7FH,这128位处于片内RAM 字节地址20H~2FH 单元中。其余的83个可寻址位分布在特殊功能寄存器SFR中

可被位寻址的特殊寄存器有11个,共有位地址88个,5个位未用,其余83个位的位地址离散地分布于片内数据存储器区字节地址为80H~FFH的范围内,其最低位的位地址等于其字节地址,且其字节地址的末位都为0H或8H。

各类存储器的结构图