在计算机中,中断控制器是一种集成电路,可帮助微处理器或CPU处理来自多个不同源(如外部I / O设备)的中断请求(Interrupt Request,以下简称IRQ),这些中断请求可能同时发生。中断控制器有助于确定 IRQ 的优先级,以便CPU在得到 IRQ 的相对优先级评估结果后,切换到最合适的中断处理程序 (Interrupt?Service?Routine,以下简称ISR)。

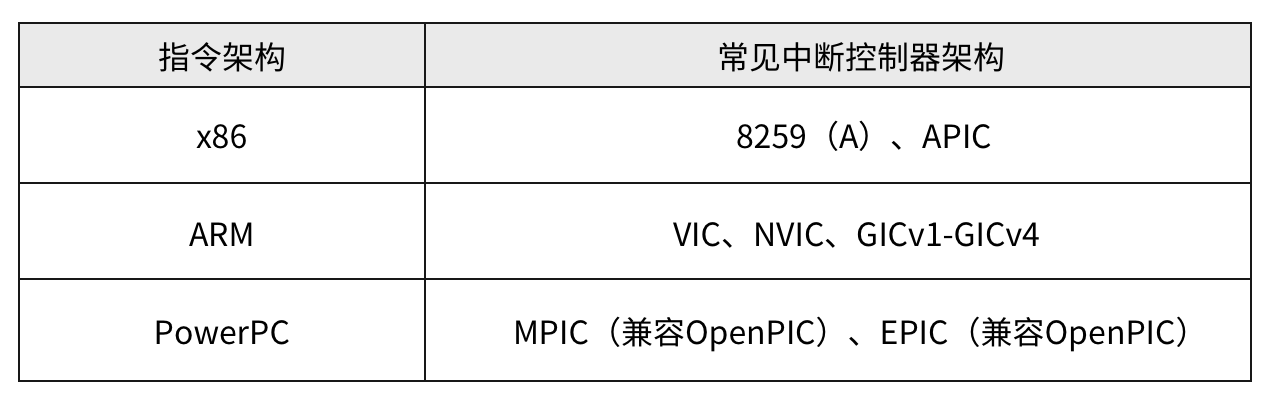

当前市面上主流的芯片架构通常采用不同的中断控制器:

▲表1?主流芯片架构及其中断控制器

01.早期的中断控制器

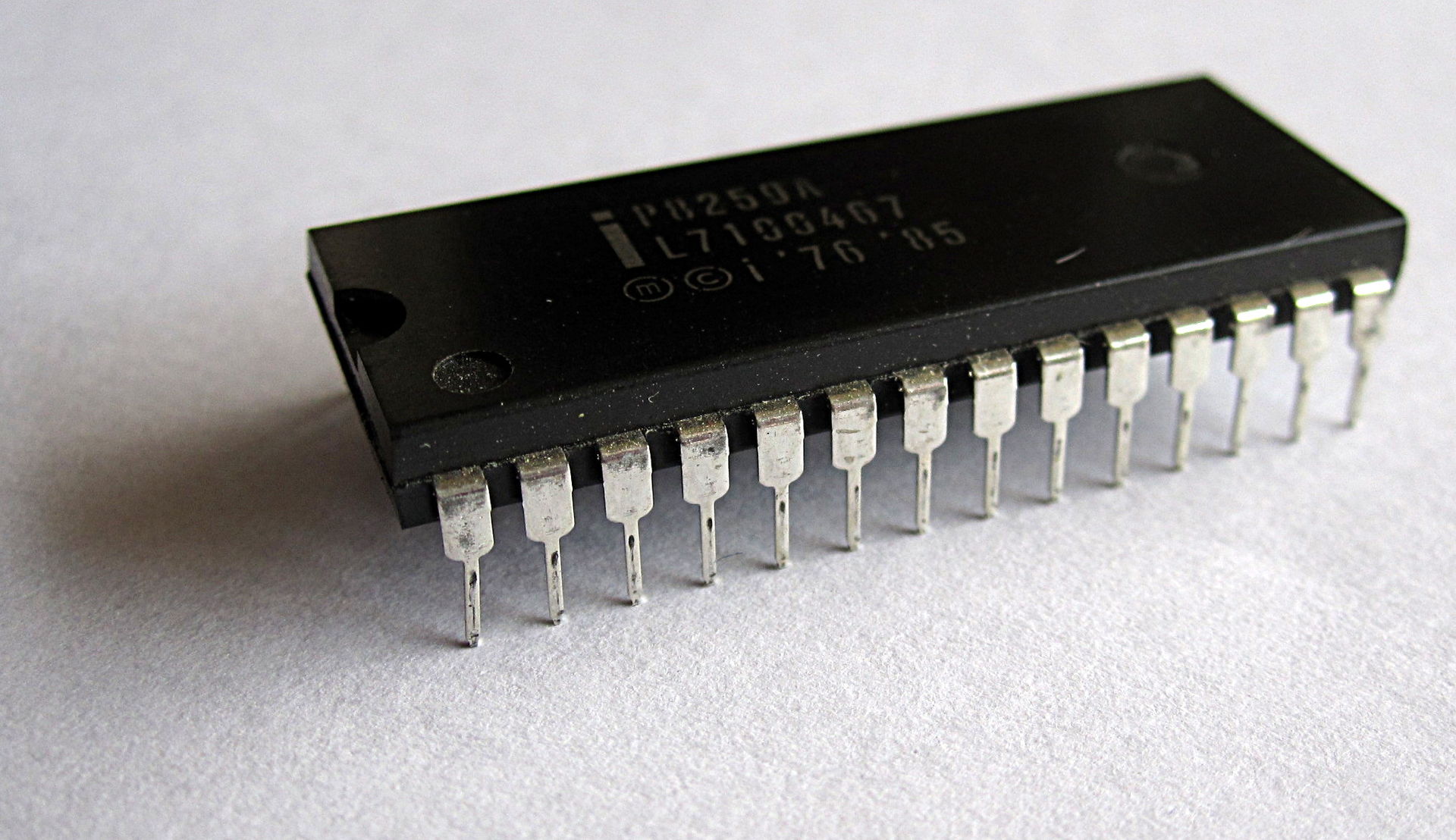

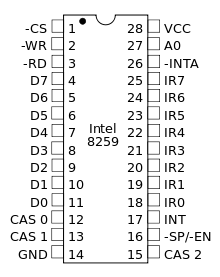

早期的中断控制器已拥有中断控制器的基本功能,即从I/O接受中断信号并传递给CPU,同时可以屏蔽中断,控制中断优先级等功能。Intel?8259是典型的早期可编程中断控制器 (Programmable Interrupt Controller,以下简称PIC),于 1976 年作为Intel?MCS 85 家族的成员推出,专为Intel?8085 和Intel?8086 微处理器而设计。后来的Intel 8259A(后简称8259A)版本向上兼容,可与8086或8088处理器一起使用。现代 PC 已开始逐步淘汰 8259A,转而采用Intel?高级可编程中断控制器 (Advanced Programmable Interrupt Controller,?以下简称APIC)架构。虽然不再是单独的芯片,但8259A接口仍存在于现代x86主板上的平台控制器集线器或南桥芯片组。

▲图1?Intel 8259 实物图

▲图2 Intel?8259引脚图

8259A提供了最基础的的中断控制功能:

- 中断引脚IRQ0-IRQ7,接收外部设备产生一个或多个中断;

- 中断请求寄存器IRR,置位中断请求寄存器位;

- 中断服务寄存器ISR,置位中断寄存器位,表示当前正在处理的中断;

- 优先级处理,当多个中断同时触发时,判断优先处理的中断;

- 中断掩码寄存器,用于屏蔽特定的中断;

- INT引脚与CPU的中断引脚连接,用于触发CPU中断;

- 数据通道D0-D7,发送中断向量给CPU。

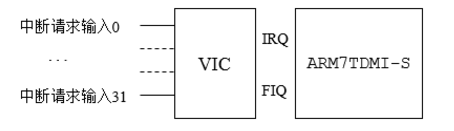

早期ARM核心,如ARM7TDMI-S,通常使用向量中断控制器(Vectored Interrupt Controller,以下简称?VIC)来管理中断,最多可处理32个中断请求,并且将中断通过IRQ和FIQ传递。

▲图3?ARM7TDMI-S?VIC示意图

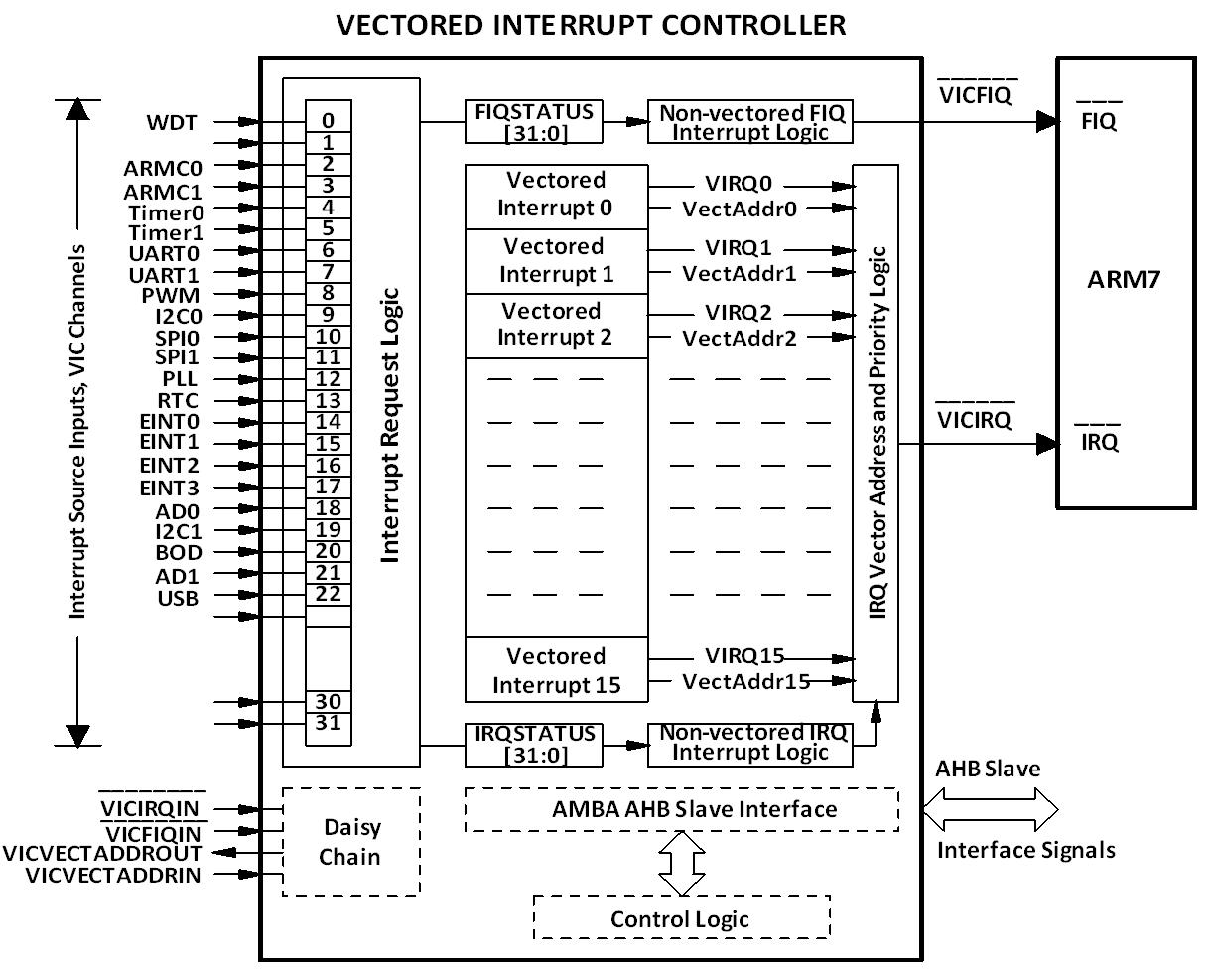

恩智浦基于ARM7TDMI-S架构,开发了32位RISC微控制器LPC2148。LPC2148使用ARM PrimeCell(PL190)向量中断控制器来管理中断,PL190通过AHB总线与ARM内核连接。

▲图4?PL190?VIC示意图

VIC通过中断选择寄存器(VIC?IntSelect)将中断请求分为三类:

- 快速中断请求(Fast Interrupt?Qequest,以下简称FIQ),具有最高优先级;

- 向量IRQ(Vectored IRQ,以下简称VIRQ),具有中等优先级;

- 非向量 IRQ(Nonvectored IRQ,以下简称NVIRQ),具有最低优先级;

对于FIQ,大多数情况下,只分配一个中断,VIC 提供 ISR 地址。如果将多个中断分配给 FIQ,VIC 将合并所有地址,生成 VICFIQ,为所有 FIQ(非向量 FIQ)仅提供一个 ISR 地址。

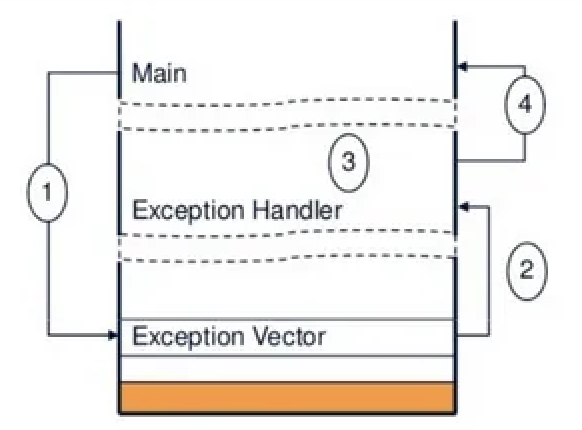

对于VIRQ和NVIRQ,任何中断源都可以设置为VIRQ和NVIRQ。NVIRQ与VIRQ的区别在于,NVIRQ不能为每个中断源设置服务程序地址,而是所有的NVIRQ中断都共用一个相同的服务程序入口地址。当有多个中断源被设置为NVIRQ中断时,需要在用户程序中识别中断源,并分别作出处理,所以非向量IRQ中断响应延时相对较长。中断向量异常处理流程如图所示:

▲图5 向量中断处理流程

阶段1:发生异常时,当前指令流将停止,处理器将访问异常向量表。

阶段2:该异常的向量地址是从向量表中加载的。

阶段3:异常处理程序开始在处理程序模式下执行。

阶段4:异常处理程序返回到 main(假设没有进一步的嵌套)。

02.现代MCU常用的向量中断控制器

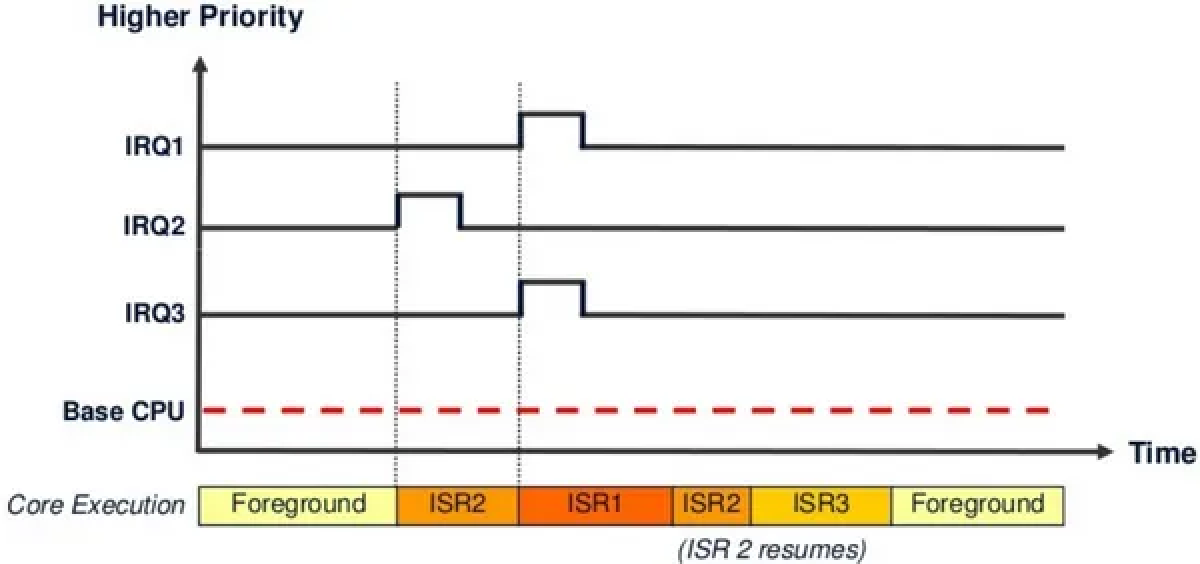

为了进一步提高重要中断响应的实时性,ARM采用了类似于实时操作系统基于任务优先级抢占的机制,使优先级更高的中断可以抢占当前中断。ARM CPU使用嵌套向量中断控制器(Nested Vectored Interrupt Controller,以下简称NVIC),设置每个中断的优先级,并且处理一个中断(具有更高的优先级)与另一个中断(具有较低的优先级)时,具有较高优先级的中断可以抢占优先级较低的中断,从而导致中断中的中断,这种中断的抢占称为中断嵌套。例如,如果发生低优先级中断并正在执行时,发生了更高优先级的中断,ARM CPU 将暂停低优先级中断并开始执行高优先级中断,并且在高优先级中断服务程序执行完成后继续执行低优先级的中断服务程序,如图所示:

▲图6 中断优先级抢占

图示以不同的优先级触发了3个异常/中断。IRQ1 抢占了IRQ2,并强制IRQ3 暂停,直到 IRQ1 完成。在 IRQ1 ISR 完成之后,ISR2 会继续从 IRQ1 抢占它时中断的地方继续。最后,在 ISR2 完成后,ISR3 开始执行。ISR3执行完成后,上下文将恢复到主程序。

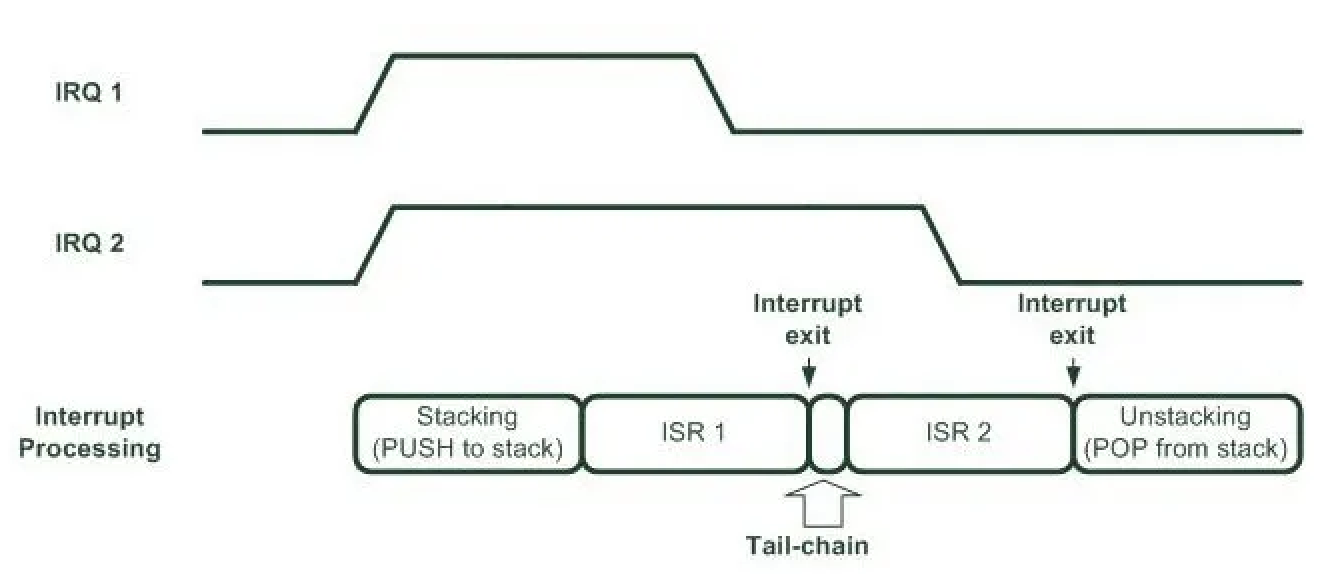

NVIC支持的另一个概念是中断的尾链。当触发中断(异常)时,主程序代码上下文被保存到堆栈,处理器分支到相应的中断向量以开始执行 ISR 处理程序。在 ISR 结束时将弹出保存在堆栈中的上下文,以便处理器可以恢复主程序代码指令。但是,当高优先级的ISR抢占低优先级ISR时,处理器会跳过上下文保存和恢复,直接处理第二个 ISR,没有任何额外的开销。这被称为"尾链",如下图所示:

▲图7?NVIC嵌套尾链中断示意图

NVIC提供了中断处理嵌套的支持,使得中断处理过程中当更高级中断来临时,不用关闭中断即可直接响应更高级别的中断信号,提高了重要中断的响应速度。

03.成熟的中断控制器

随着SMP(Symmetric Multiprocessing)架构的发展,外部中断源的数量持续增加。软中断(Software Interrupt,SWI)和核间中断(Interprocessor Interrupt,IPI),基于消息传递的中断(Message Signaled Interrupts,MSI),以及对虚拟化的支持,都需要中断控制器深度参与。传统的中断控制器已不能满足需求,各个架构也开始使用更成熟的的中断控制器。

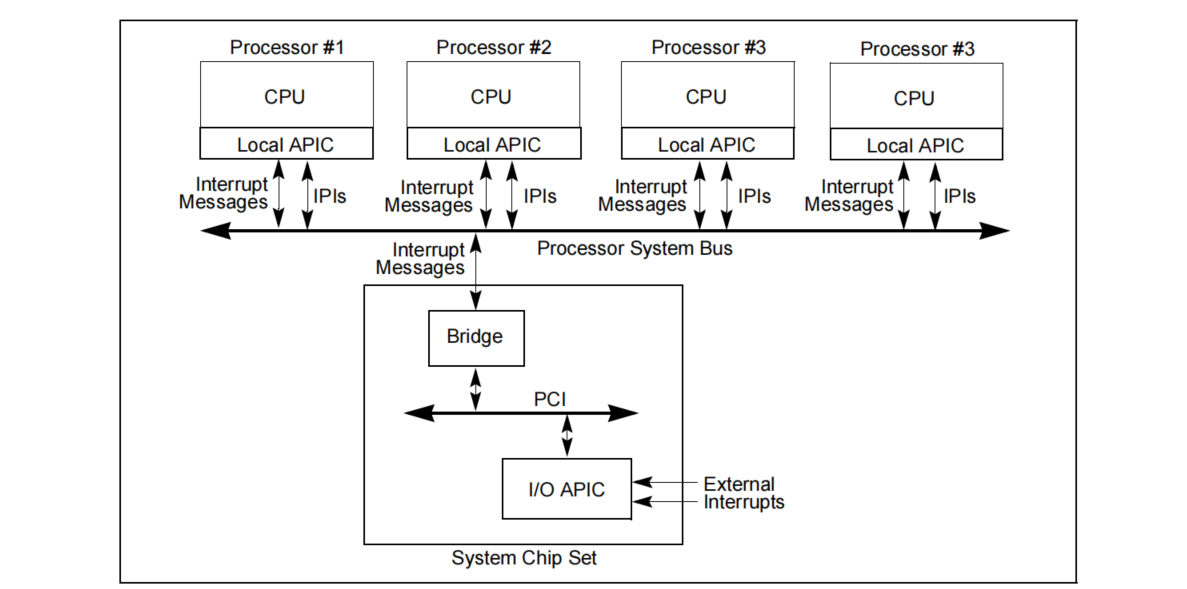

Intel在2000年左右的时候率先引入一种名为APIC的新组件,来替代老式的 8259A 可编程中断控制器。APIC包括两部分:一是本地APIC(Local APIC),主要负责传递中断信号到指定的处理器。二是I/O APIC,主要是收集来自 I/O 设备的 Interrupt 信号且将中断时发送信号到本地 APIC。

▲图8?本地APICs和I/O APIC被用于?Intel至强系列多核芯片系统

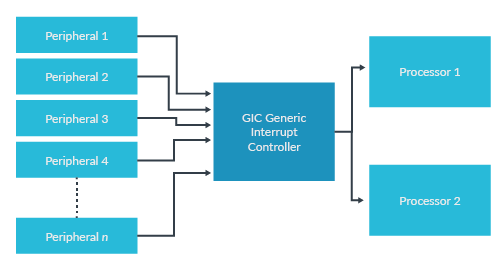

ARM使用通用中断控制器(Generic?Interrupt?Controller,以下简称GIC),从外设获取中断,对其进行优先级排序并传递到相应的处理器内核。

▲图9?GIC工作示意图

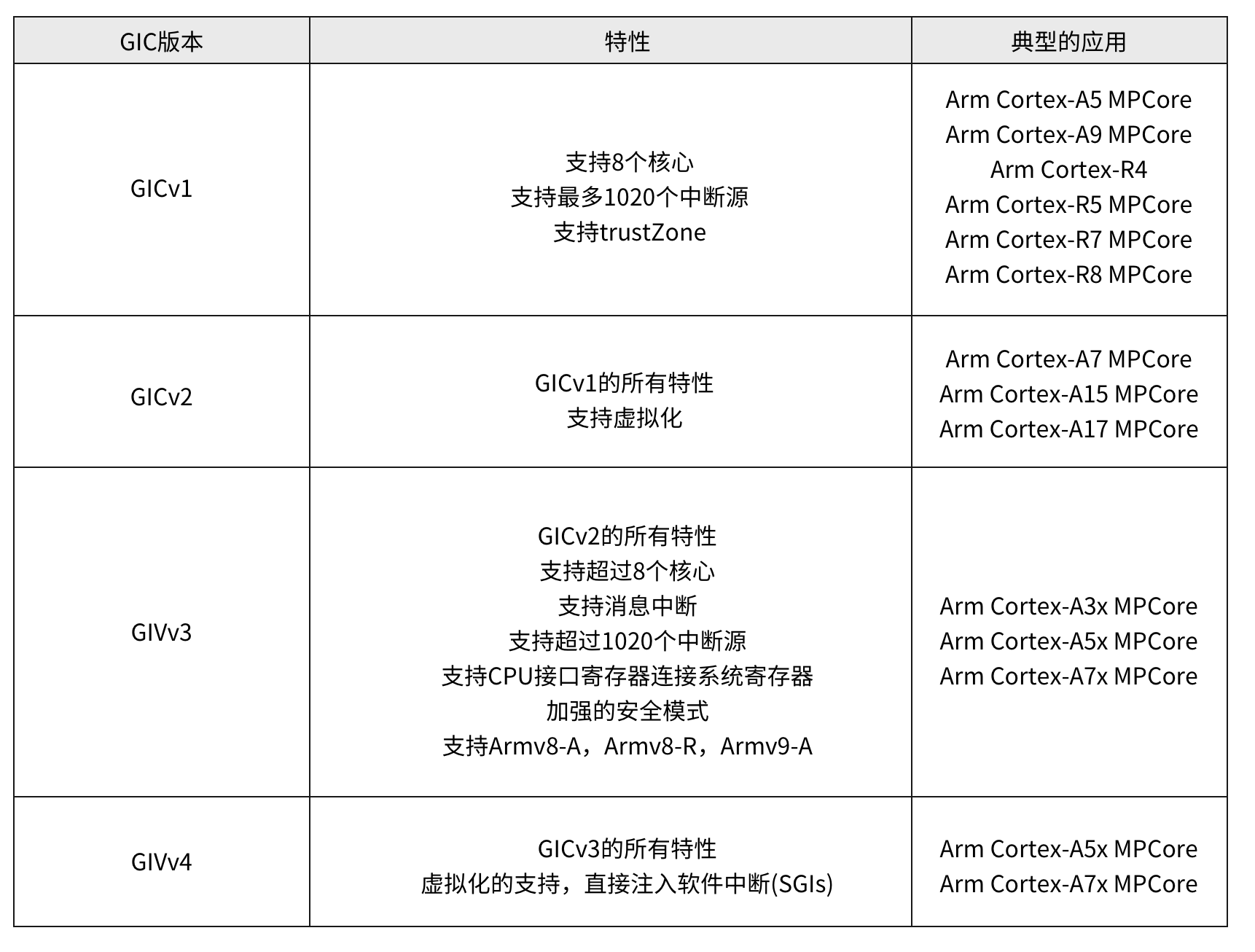

与 ARM?架构一样,GIC 架构也随着时间的推移而发展。下表总结了 GIC 规范的主要版本以及通常与它们一起使用的处理器:

▲表2 GIC版本之间的区别

以GICv3/v4为例,GIC可以处理四种中断源,分别是:

- 共享的外设中断(Shared Peripheral Interrupt,SPI),所有核心都可以接收到的中断;

- 私有的外设中断(Private Peripheral Interrupt,PPI),某一个核心独有的中断;

- 软中断(Software Generated Interrupt,SGI),通过写GIC中的SGI寄存器产生,常用与核间通信;

- 本地特定外设中断(Locality-specific Peripheral Interrupt,LPI),v3新增的中断类型,基于消息传递的中断。

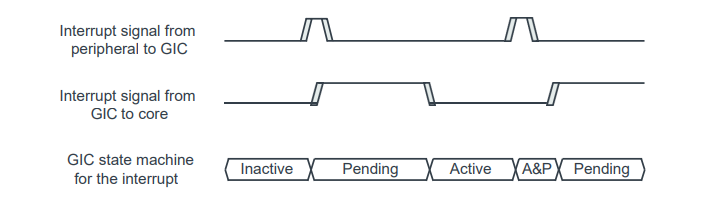

- 以GICv3/v4为例,GIC有四种中断状态,分别是:

- 未激活(Inactive),中断源还未激活;

- 挂起(Pending),中断源已激活,但无中断信号;

- 激活(Active),CPU已经响应中断;

- 激活并等待(Active and Pending),CPU已响应中断,同时新的中断挂起。

▲图10 ?GIC中的中断的4种状态

AMD和Cyrix在1995年初提出了OpenPIC中断控制器规范,支持多达32个处理器。OpenPIC架构在1995年左右至少得到了IBM和康柏的声明性支持,但没有x86主板与OpenPIC一起发布。在 OpenPIC在x86市场失败后,AMD 为其 AMD 速龙和更高版本的处理器授权了英特尔 APIC 架构,而IBM基于OpenPIC寄存器规范开发了他们的多处理器中断控制器(Multiprocessor Interrupt Controller,MPIC)。NXP基于的PowerPC架构的多核处理器,如PowerQUICC 和QorIQ 系列的处理器,依然采用MPIC作为中断控制器。

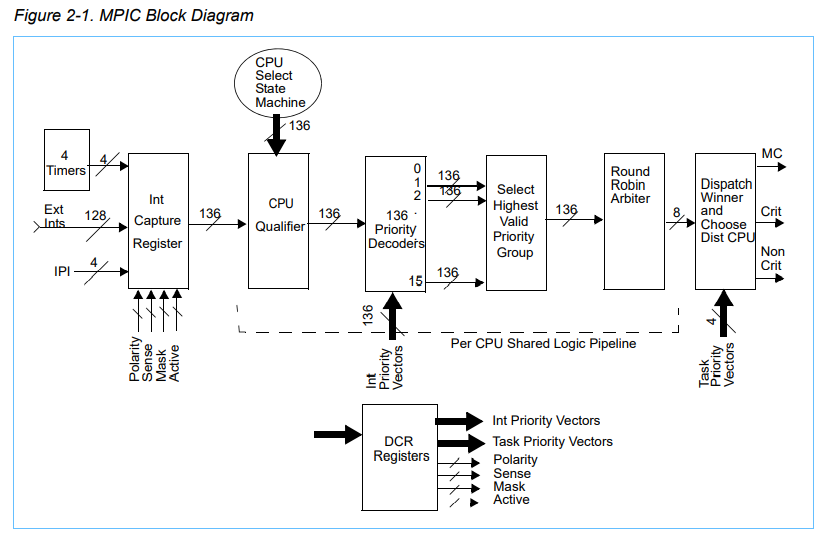

MPIC 兼容 OpenPIC 并有所增强,主要包括增加了 #cint 和 #mcp 中断信号输出,更灵活的多处理器中断路由算法等,MPIC的基本功能如下图所示:

▲图11?MPIC流程框图

- Int Capture Register可以获取到Timer中断,外部中断,IPI中断三种类型的中断;

- EPIC从Int Capture Register中获取非屏蔽的中断信号;

- 基于优先级和分配算法分配中断到某一CPU上;

- CPU读MPIC IAR寄存器获取中断源;

- 每个CPU通过MPIC EOI寄存器表示结束各自的中断。

NXP基于PowerPC架构的单核处理器,如 MPC8240和MPC8245,通常采用基于openPIC的嵌入式中断控制器(Embedded Programmable Interrupt Controller,EPIC)。EPIC或者MPIC通常都被统称为PIC。MPC8245的PIC功能框图如下图所示:

▲图12?MPC8245的PIC功能框图

MPC8245的PIC有以下特性:

- 中断优先级的值由0-15,共16个优先级,以15为最高优先级;

- 接收5个外部中断和16个串行中断源;

- 接收4个可产生中断的定时器;

- 支持PIC Pass-Through模式;

- 支持PIC Direct Interrupt模式;

- 接收DUART, DMA, I2C, MU, WP接口连接的设备的中断;

- 支持嵌套中断。

04.全数字实时仿真软件SkyEye

SkyEye,中文全称天目全数字实时仿真软件,是基于可视化建模的硬件行为级仿真平台,现在已支持x86/ARM/DSP/PowePC/Sparc/MPIS等多种主流芯片架构的仿真,同时支持数十款主流芯片及其中断控制器。

更多?SkyEye?相关内容,欢迎关注公众号迪捷软件或访问?www.digiproto.com?进行了解!

参考文献

《8259A PROGRAMMABLE INTERRUPT CONTROLLER (8259A/8259A-2)》

《Intel? 64 and IA-32 Architectures Software Developer’s Manual Volume 3A: System Programming Guide, Part 1》

《PrimeCell? Vectored Interrupt Controller (PL190) Technical Reference Manual Revision: r1p2》

《Arm Generic Interrupt Controller v3 and v4 Overview Version 3.2》

《Multiprocessor Interrupt Controller Data Book》

《MPC8245 Integrated Processor Reference Manual》