ЭЈаХавщећРэжЎ SPI ЭЈаХ

МђНщ

SPIЪЧДЎааЭтЩшНгПк(Serial Peripheral Interface)ЕФЫѕаД,ЪЧвЛжжИпЫйЕФ,ШЋЫЋЙЄЭЌВНЭЈаХзмЯп,ВЂЧвдкаОЦЌЕФЙмНХЩЯжЛеМгУЫФИљЯп,НкдМСЫаОЦЌЕФЙмНХ,ЭЌЪБЮЊPCBЕФВМОжЩЯНкЪЁПеМф,ЬсЙЉЗНБуЁЃSPIНгПкжївЊгІгУдк EEPROM ,FLASH ,ЪЕЪБЪБжг,AD зЊЛЛЦї,ЛЙгаЪ§зжаХКХДІРэЦїКЭЪ§зжаХКХНтТыЦїЕШЭтЩшжЎМфЁЃ

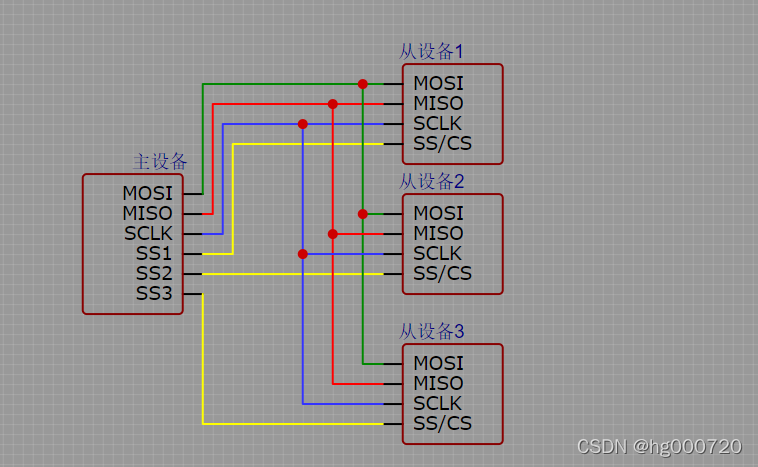

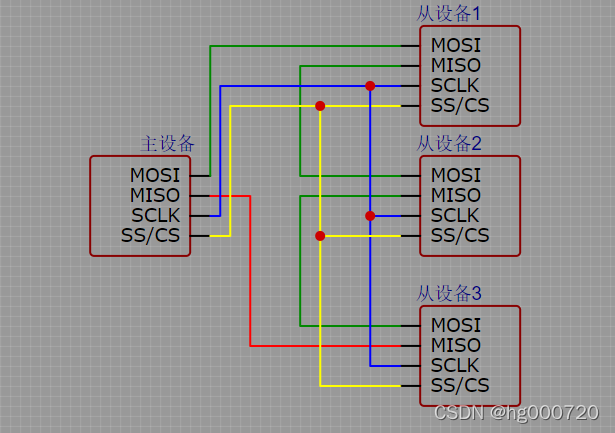

SPI ЭЈаХЕФвЛИіЖРЬигХЪЦЪЧЪ§ОнПЩвдВЛМфЖЯЕиДЋЪфЁЃПЩвддкСЌајСїжаЗЂЫЭЛђНгЪеШЮвтЪ§СПЕФЮЛЁЃдкЪЙгУ IIC КЭ UART авщЪБ,Ъ§ОнЪЧвдЪ§ОнАќЕФаЮЪНЗЂЫЭЕФ,Ъ§ОнАќжаЖЈвхСЫПЊЪМКЭНсЪјЕФЮЛ,вђДЫЪ§ОндкДЋЪфЙ§ГЬжаЛсжаЖЯЁЃ

ЭЈЙ§ SPI НјааЭЈаХЕФЩшБИЪєгкжїДгЙиЯЕЁЃвђДЫ,SPI авщжїЩшБИ( жїеО )ЭЌбљПЩвдПижЦЖрИіДгЩшБИ( ДгеО )ЁЃ

SPI в§НХЖЈвх:

- MOSI(жїЪфГі/ДгЪфШы):жїеОНЋЪ§ОнЗЂЫЭЕНДгеОЕФЯпТЗЁЃ

- MOSI(жїЪфГі/ДгЪфШы):жїеОНЋЪ§ОнЗЂЫЭЕНДгеОЕФЯпТЗЁЃ

- SCLK(ЪБжг):ЪБжгаХКХЕФЯпТЗЁЃ

- SS/CS(ДгЛњбЁдё):жїеОбЁдёЯп,гУгкбЁдёвЊНЋЪ§ОнЗЂЫЭЕНФФИіДгЛњЁЃ

SPI ЪЧДЎааЭЈбЖавщ,Ъ§ОнЪЧвЛЮЛвЛЮЛДЋЪфЕФ,гЩ SCLK ЬсЙЉЪБжгТіГх, MOSI , MISO дђЛљгкДЫТіГхЭъГЩЪ§ОнДЋЪфМАЭЌВНЕФЁЃР§ШчЪ§ОнЪфГіЭЈЙ§ MOSI в§НХ,Ъ§ОндкЪБжгЩЯЩ§биЛђЯТНЕбиЪБИФБф,дкНєНгзХЕФЯТНЕбиЛђЩЯЩ§биБЛЖСШЁ,вдДЫЭъГЩвЛЮЛЪ§ОнДЋЪф,ЪфШывВЭЌРэЁЃ

жЕЕУзЂвтЕФЪЧ, SCLK аХКХЯпНігЩжїЩшБИПижЦ,ДгЩшБИВЛФмПижЦаХКХЯпЁЃвђДЫ,дквЛИіЛљгк SPI авщЕФЭЈаХЯЕЭГжа,жСЩйЕУгавЛИіжїЩшБИЁЃ

етбљЕФДЋЪфЗНЪНгавЛИігХЕу,гыЦеЭЈЕФДЎааЭЈбЖВЛЭЌ,SPIдЪаэЪ§ОнвЛЮЛвЛЮЛЕФДЋЫЭ,ЖјВЛашвЊвЛДЮДЋЪфжСЩйАЫЮЛЪ§Он(вЛИізжНк),SPI ЩѕжСдЪаэднЭЃ,вђЮЊ SCLK ЪБжгЯпНігЩжїПиЩшБИПижЦ,жїЩшБИЭЈЙ§Жд SCLK ЪБжгЯпЕФПижЦПЩвдЭъГЩЖдЭЈбЖЕФПижЦ,БШШчЕБУЛгаЪБжгЬјБфЪБ,ДгЩшБИВЛВЩМЏЛђДЋЫЭЪ§Он,ЗДжЎдђВЩМЏЪ§ОнЁЃSPI ЛЙЪЧвЛИіЪ§ОнНЛЛЛавщ:вђЮЊSPIЕФЪ§ОнЪфШыКЭЪфГіЯпЖРСЂ,ЫљвддЪаэЭЌЪБЭъГЩЪ§ОнЕФЪфШыКЭЪфГіЁЃ

ЙЄзїдРэ

ДгЩЯЪіПЩжЊ,SPI авщЕФЭЈаХЪЧгЩЪБжгаХКХПижЦЕФ,ЪБжгаХКХИКд№НЋжїЩшБИЕФЪ§ОнЮЛЪфГігыДгЩшБИЕФЮЛВЩбљЭЌВНЁЃУПИіЪБжгжмЦкДЋЪфвЛЮЛЪ§Он,вђДЫЪ§ОнДЋЪфЕФЫйЖШШЁОігкаХКХЕФЦЕТЪЁЃ

SPI жаЕФЪБжгаХКХПЩвдЪЙгУЪБжгМЋадКЭЪБжгЯрЮЛЪєадНјаааоИФЁЃетСНИіЪєадаЭЌЙЄзї,вдЖЈвхКЮЪБЪфГівдМАКЮЪБНјааВЩбљЁЃетОЭЩцМА SPI ЭЈаХЕФЪБађ,ЯъНтШчЯТ:

- CPOL :ЪБжгМЋадбЁдё,ЮЊ 0 ЪБ SPI змЯпПеЯаЮЊЕЭЕчЦН;ЮЊ 1 ЪБ SPI змЯпПеЯаЮЊИпЕчЦНЁЃ

- CPHA :ЪБжгЯрЮЛбЁдё,ЮЊ 0 ЪБдк SCLK ЕквЛИіЬјБфбиВЩбљ;ЮЊ 1 ЪБдк SCLK ЕкЖўИіЬјБфбиВЩбљЁЃ

гЩДЫзщКЯ,ПЩвдЕУЕН SPI ЕФЫФжжЙЄзїФЃЪН:

| SPI ФЃЪН | CPOL | CPHA | ПеЯазДЬЌЯТЕФЪБжгМЋад | гУгкВЩбљКЭ/ЛђвЦЮЛЪ§ОнЕФЪБжгЯрЮЛ |

|---|---|---|---|---|

| 1 | 0 | 0 | ТпМЕЭЕчЦН | Ъ§ОндкЩЯЩ§биВЩбљ,дкЯТНЕбивЦГі |

| 2 | 0 | 1 | ТпМЕЭЕчЦН | Ъ§ОндкЯТНЕбиВЩбљ,дкЩЯЩ§бивЦГі |

| 3 | 1 | 0 | ТпМИпЕчЦН | Ъ§ОндкЩЯЩ§биВЩбљ,дкЯТНЕбивЦГі |

| 4 | 1 | 1 | ТпМИпЕчЦН | Ъ§ОндкЯТНЕбиВЩбљ,дкЩЯЩ§бивЦГі |

ЭЈаХСЌНгЗНЪН

SPI жїЩшБИвЊгыФГИіДгЩшБИЭЈаХЪБ,ПЩвдНЋДгЩшБИЕФ CS/SS ЯпТЗЩшжУЮЊЕЭЕчЦНЁЃЗДжЎ,дкПеЯаЯТ,ДгЩшБИбЁдёЯпБЃГждкИпЕчЦНЁЃжїЩшБИПЩвдгаЖрИіДгЩшБИбЁдёв§НХ,МД CS/SS в§НХ,ЧвдЪаэЖрИіДгЩшБИВЂСЊНгЯпЁЃШчЙћжїЩшБИжЛгавЛИі CS/SS в§НХ,дђПЩвдЭЈЙ§ОеЛЈСДЕФаЮЪННЋЖрИіДгЩшБИСЌНгЕНжїеОЁЃ

ОпЬхЗНЗЈШчЯТ:

ВЙГф

гВМў SPI КЭФЃФт SPI

гы IIC ЭЈаХРрЫЦ, SPI ЭЈаХвВПЩгУ IO ПкФЃФт SPI авщЪБађРДЪЕЯжЭЈаХЁЃ

гВМў SPI ЫйЖШПь,ЧвПЩвдЪЙгУ DMA РДНјааМгЫйЁЃ

ШэМў SPI НгПкЯрЖдСщЛю,ЕЋЪБађНЯИДдг,ДњТыСПНЯЖрЁЃ