前言

写这篇博客的目的是记录自己的学习过程

PLL介绍

PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPGA系统往往需要多个不同频率,相位的时钟信号。所以,一个FPGA芯片中PLL的数量是衡量FPGA芯片能力的重要指标。FPGA的设计中,时钟系统的FPGA高速设计机器重要,一个低抖动,低延迟的系统时钟会增加FPGA设计的成功率。

锁相环(PLL )主要用于频率综合。使用一个 PLL 可以从一个输入时钟信号生成多个时钟信号。

实验目的

本次实验将利用PLL锁相环产生200MHZ、100MHZ、50MHZ以及25MHZ的时钟信号

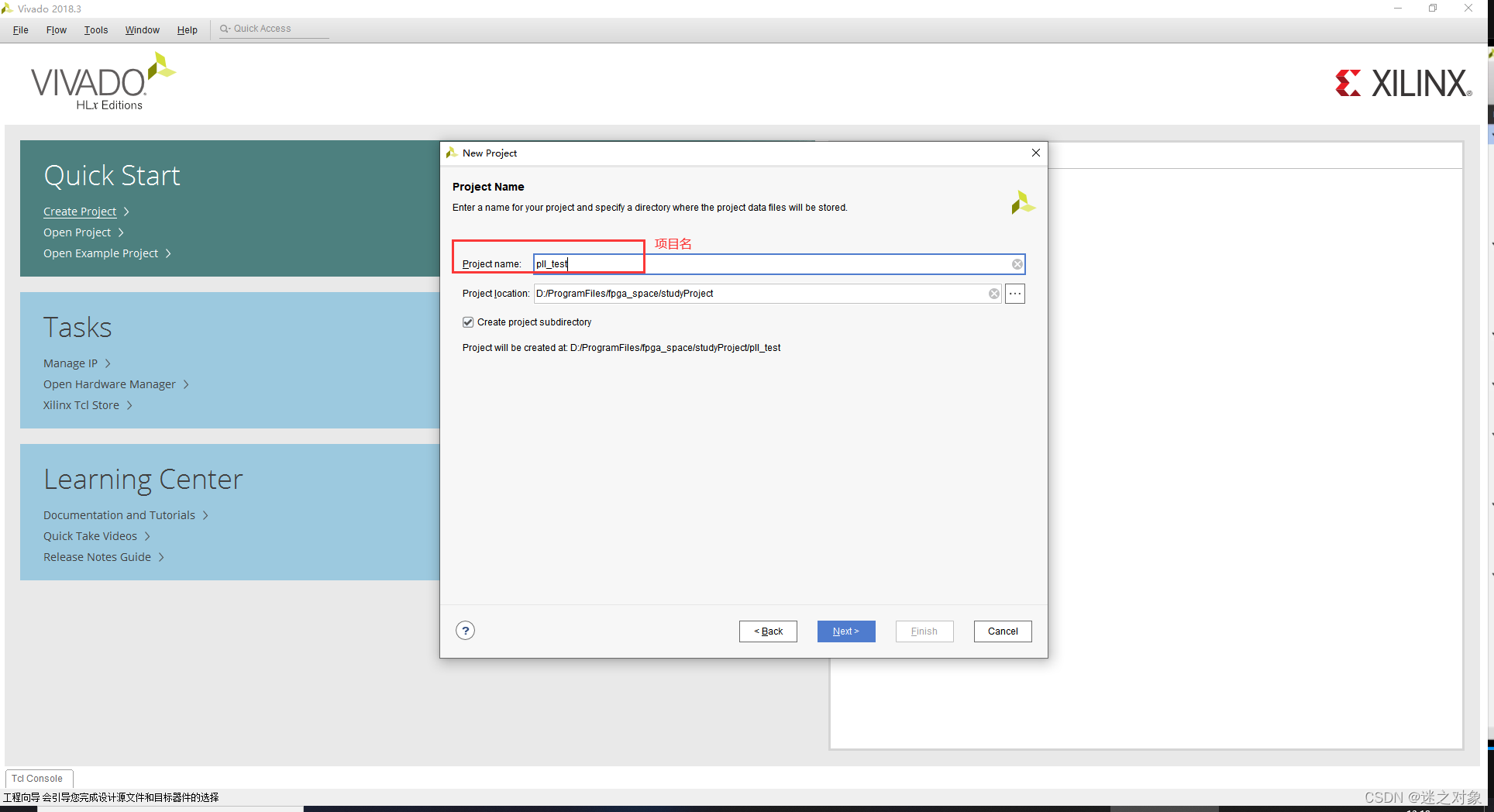

一、创建一个Vivado工程

1.创建一个项目

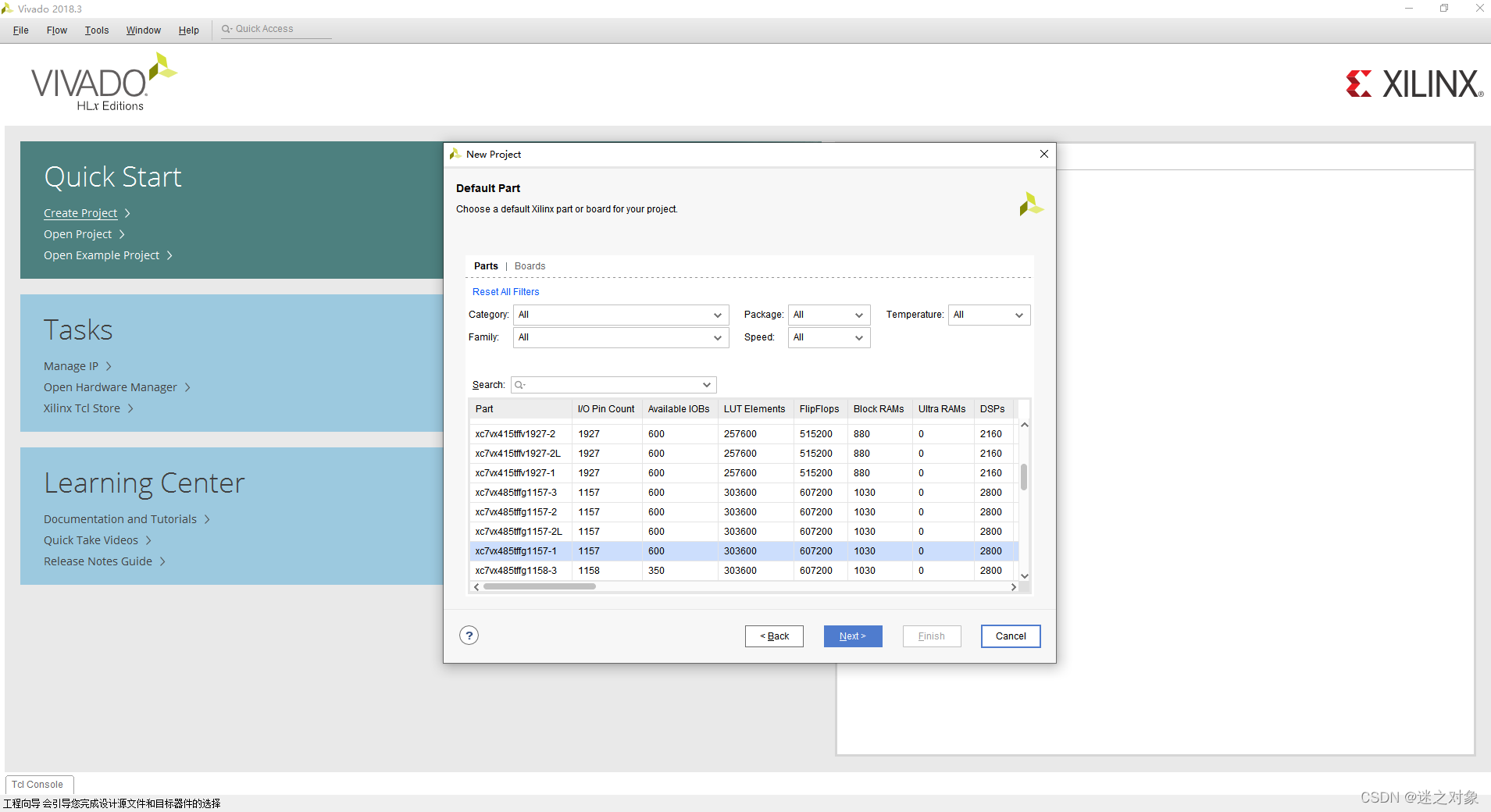

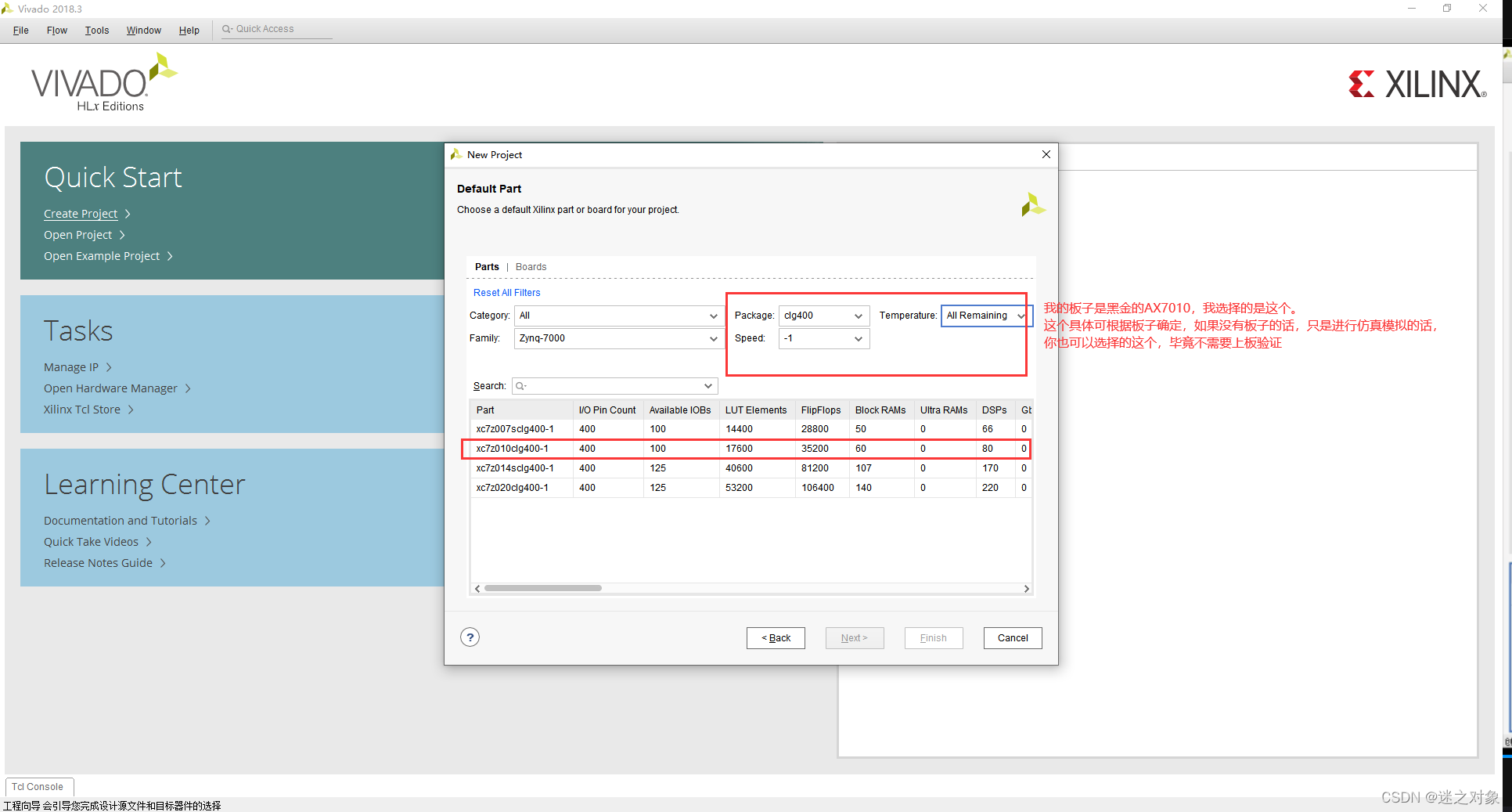

2.一直next到这里

选择之后点击下一步,直到完成。

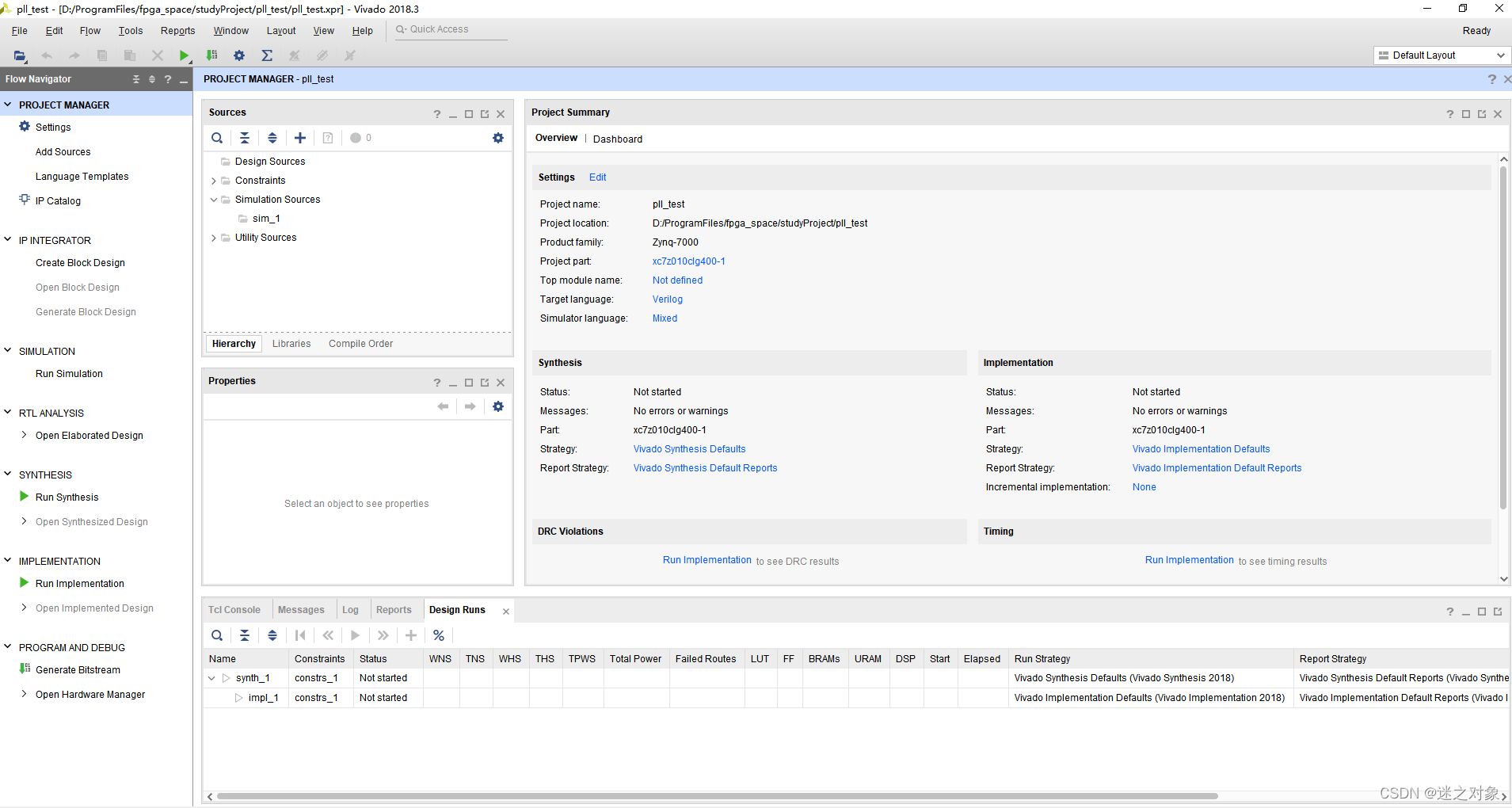

此时项目已经创建完毕

二、使用PLL的IP核

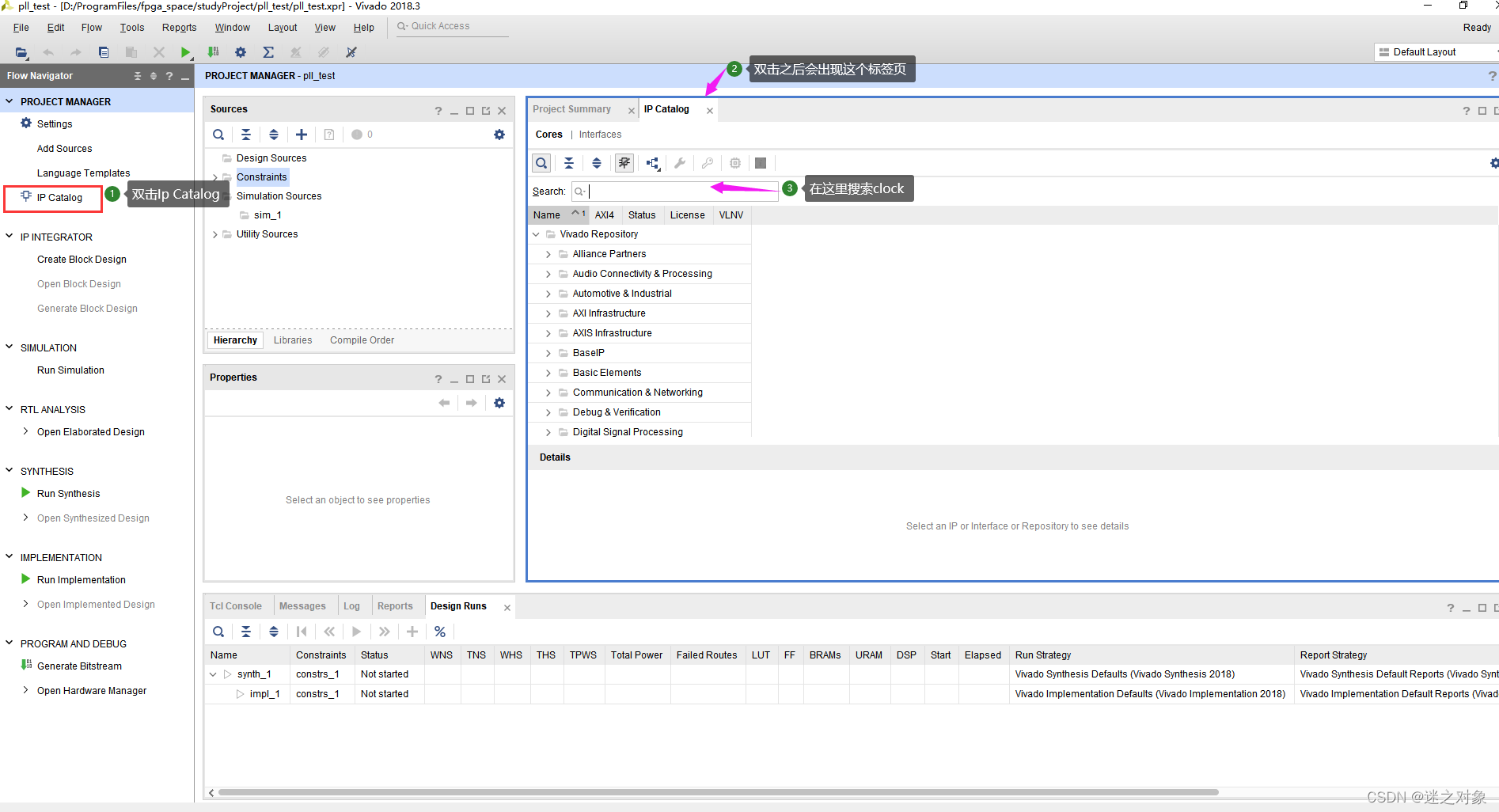

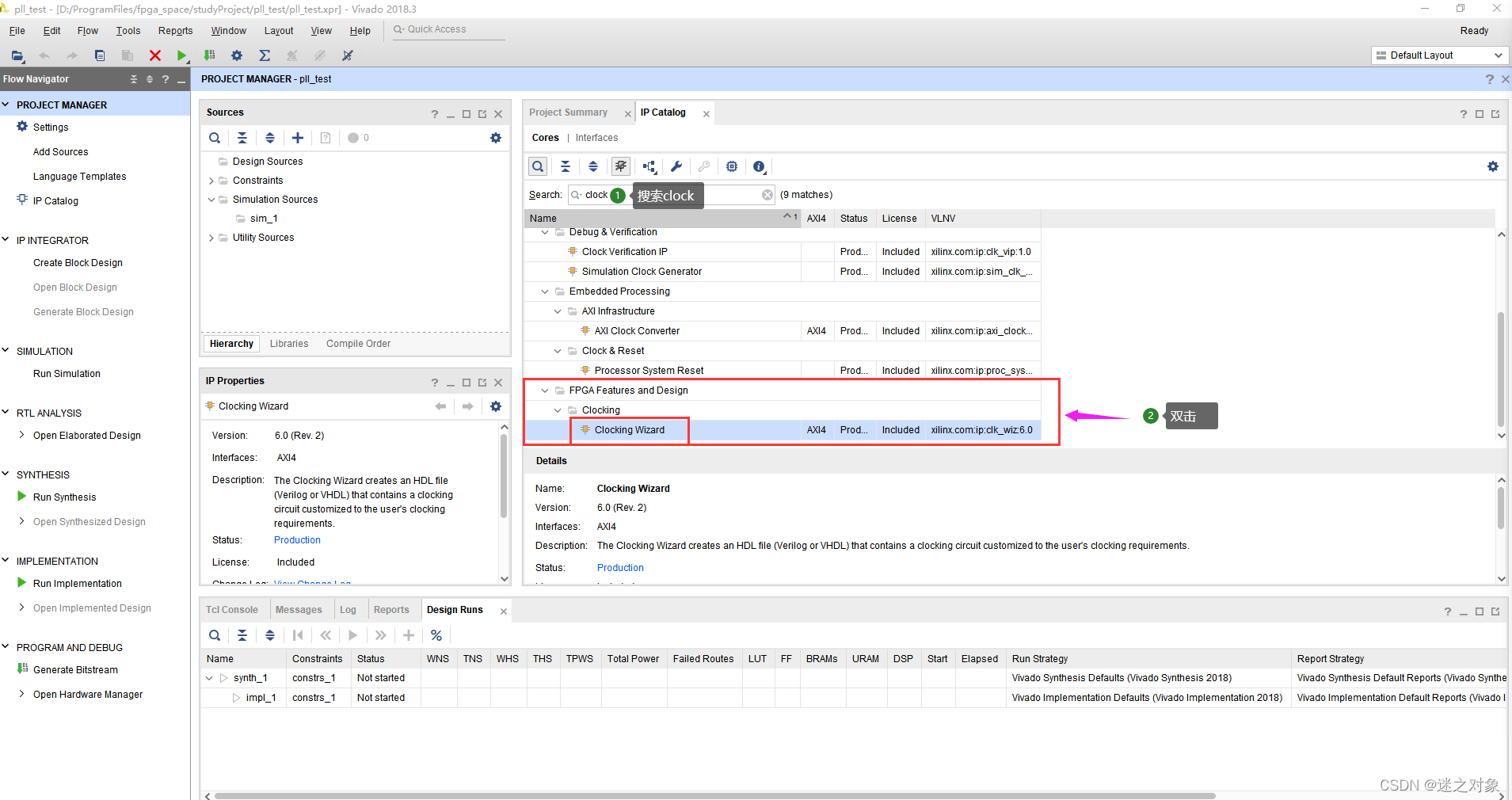

1、使用步骤

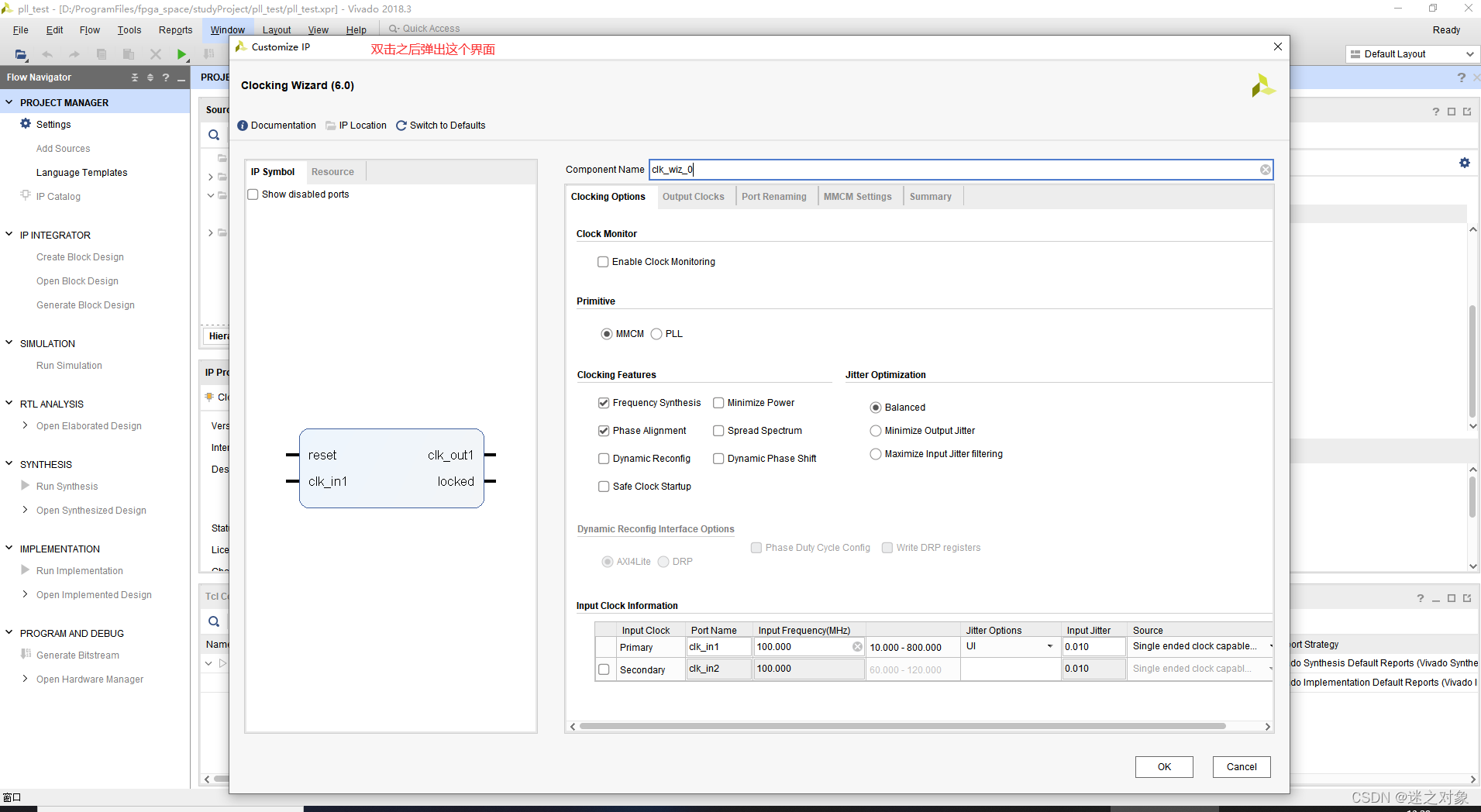

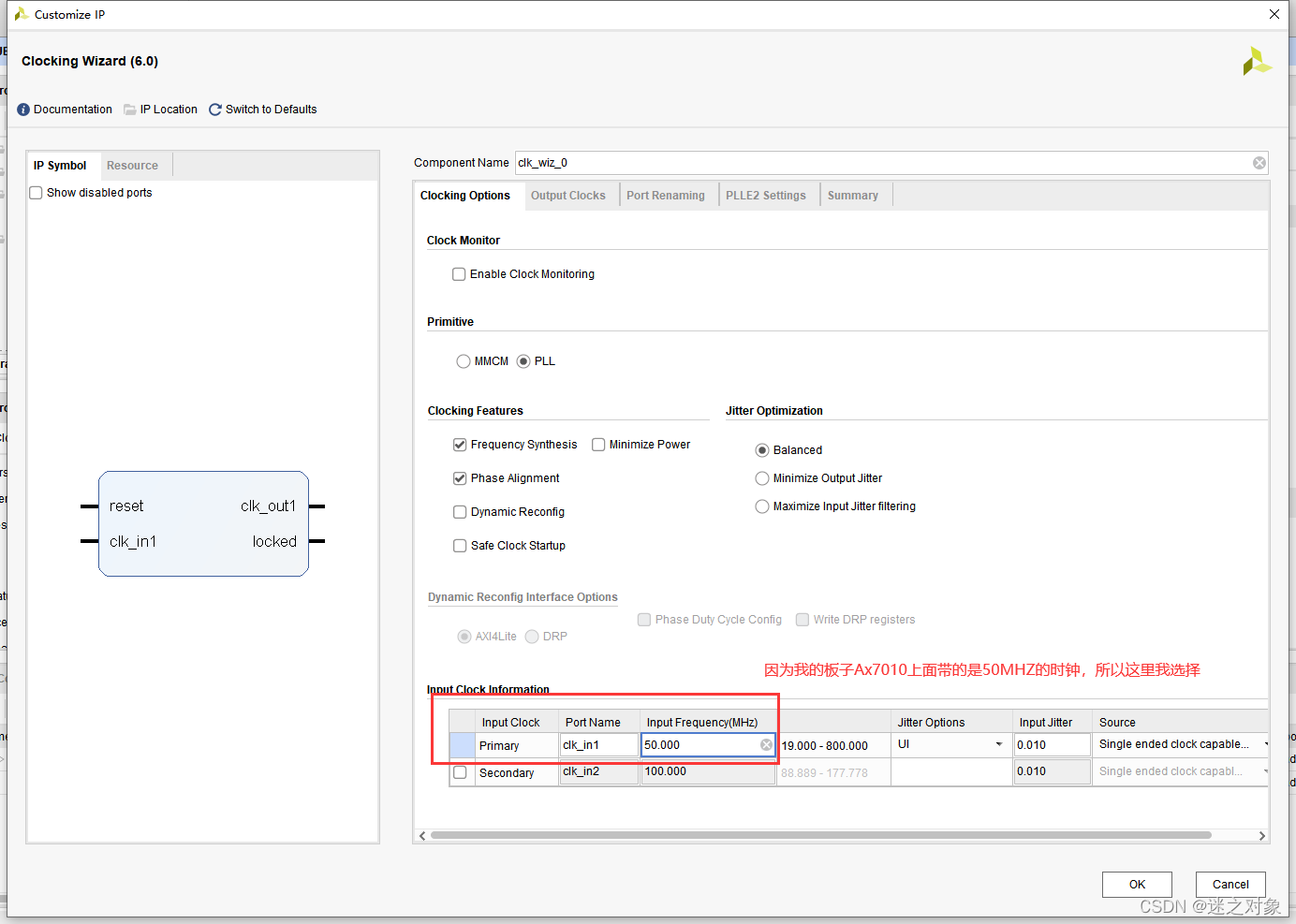

默认这个 Clocking Wizard 的名字为 clk_wiz_0, 这里我们不做修改。在第一个界面 Clocking

Options 里, 我们选择 PLL 资源,输入的时钟频率为 50Mhz

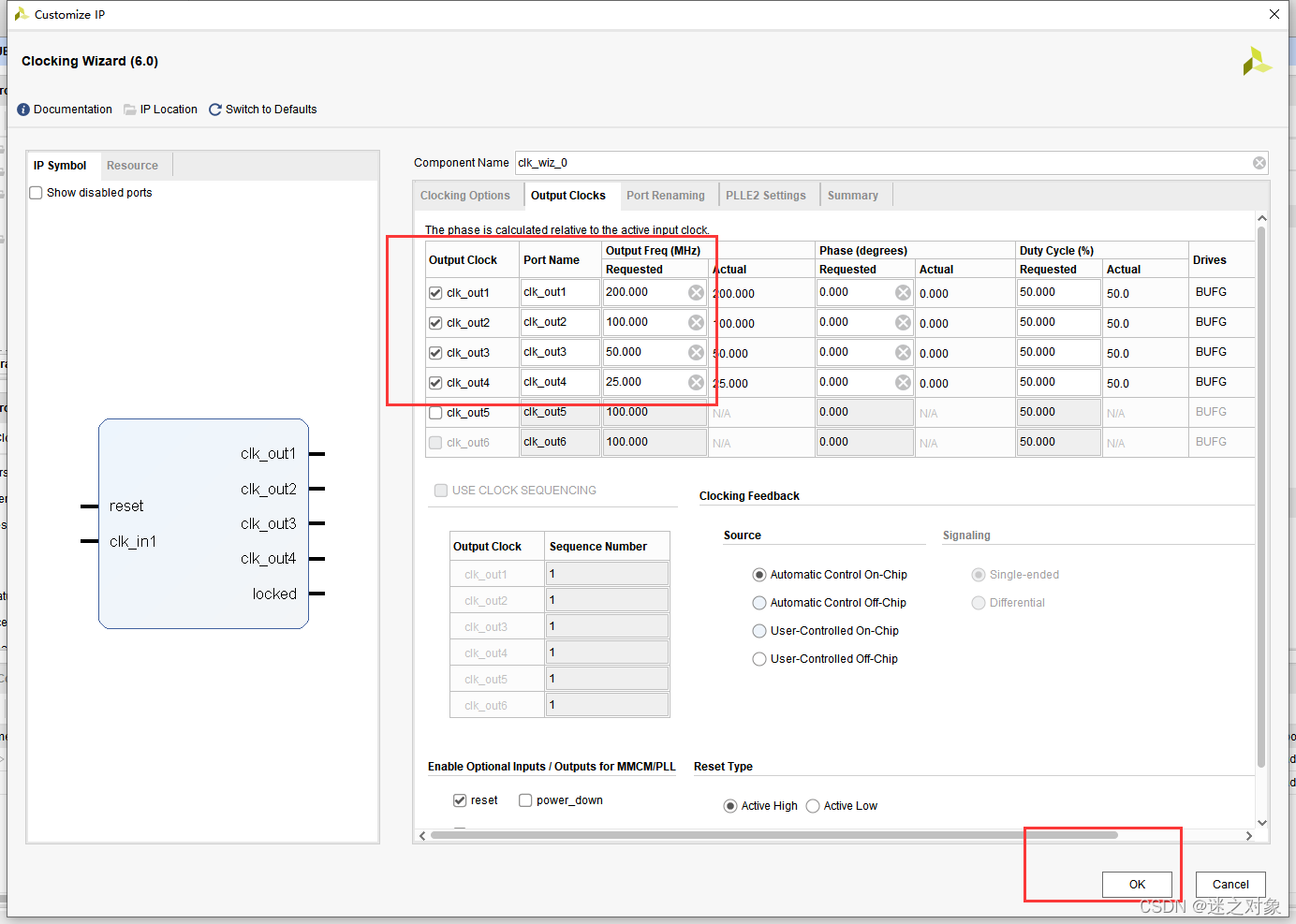

在 Output Clocks 界面里选择 clk_out1~clk_out4 四个时钟的输出,频率分别为 200Mhz,

100Mhz, 50Mhz, 25Mhz 。这里还可以设置时钟输出的相位,我们不做设置,保留默认相位

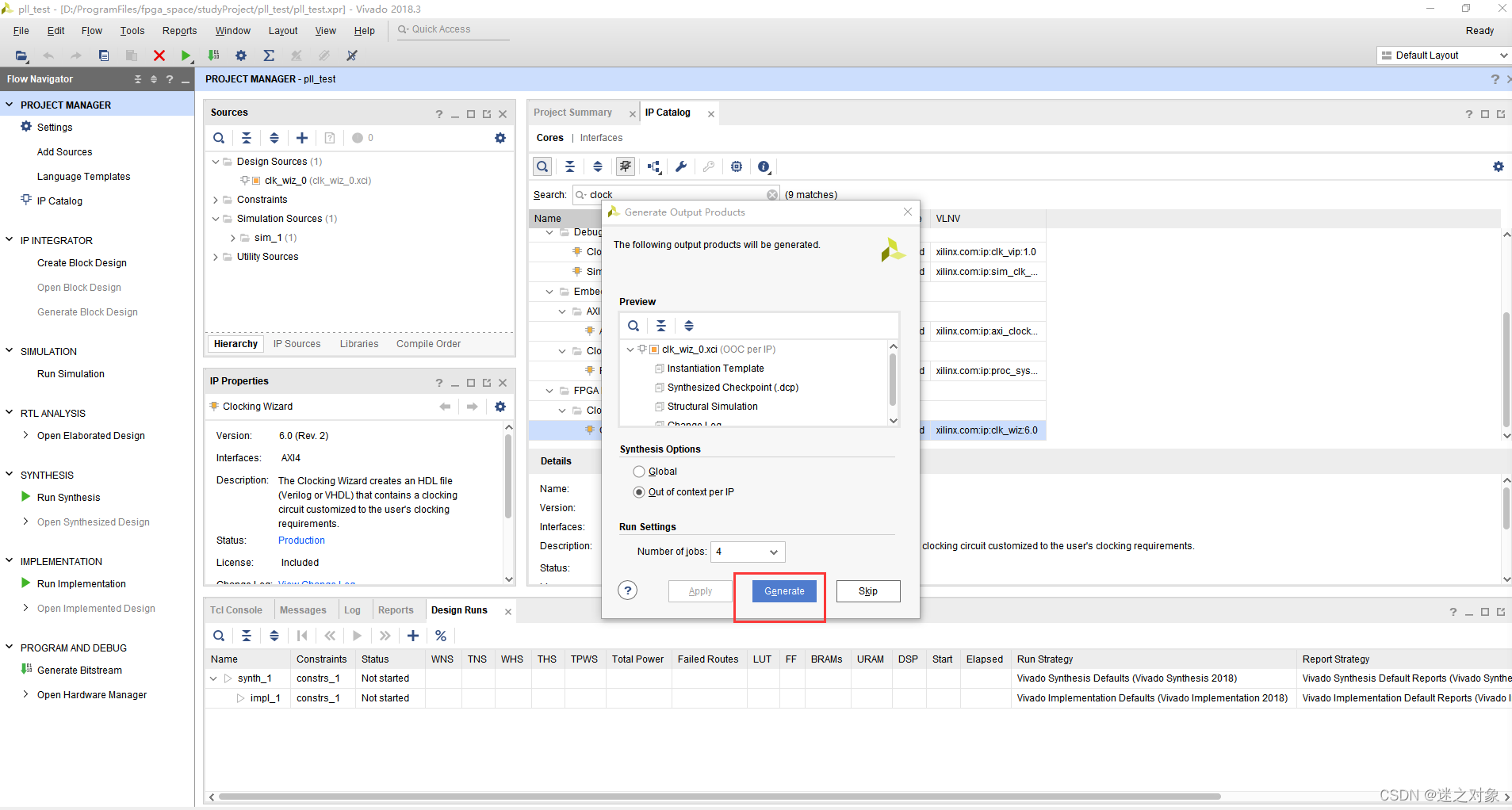

点击 OK 完成,默认的是高电平有效(reset),即高电平的时候输出是无效的

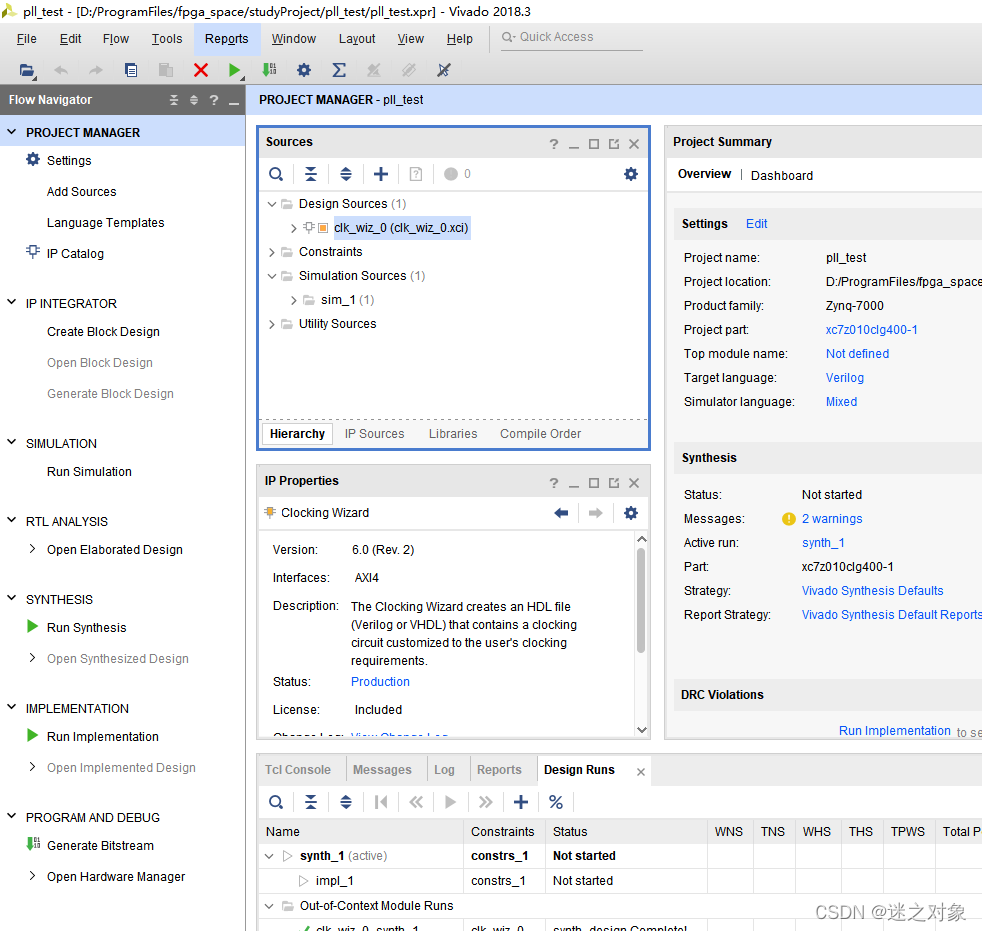

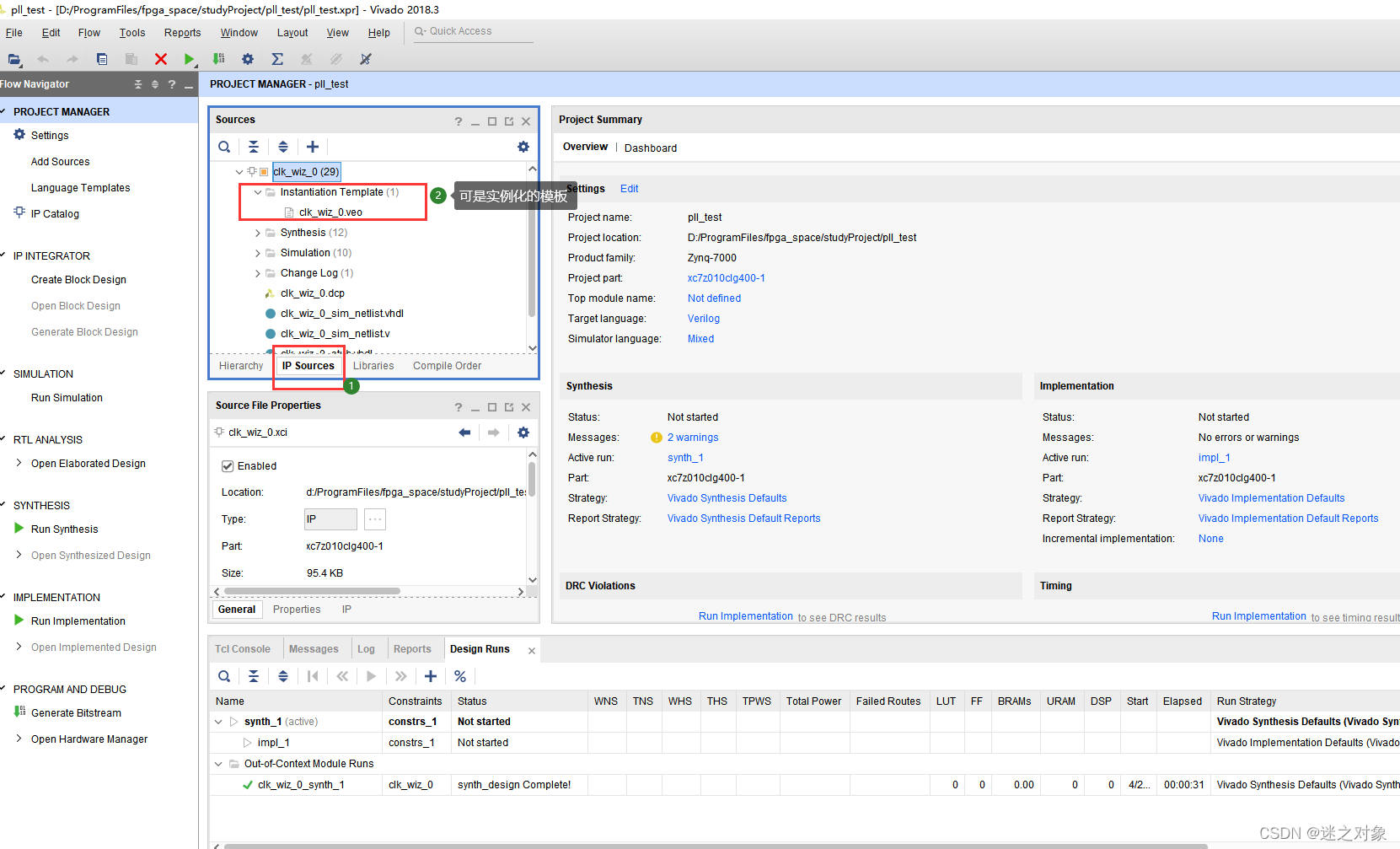

这时一个 clk_wiz_0.xci 的 IP 会自动添加到我们的 pll_test 项目中 , 用户可以双击它来修改

这个 IP 的配置。

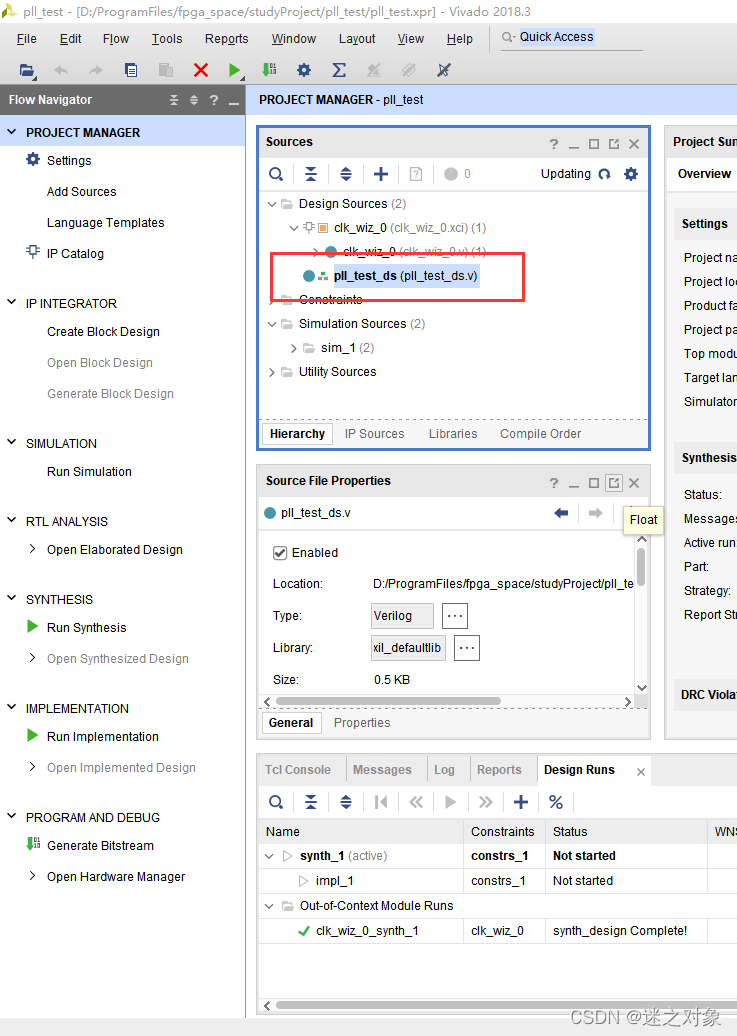

2、创建一个Design Source文件调用PLL的IP核

接下来我们编写一个Design Source来实例化这个PLL IP

3、编辑代码如下:

`timescale 1ns / 1ps

module pll_test_ds(

input sys_clk, // 板子上的系统时钟

input res_n, // 复位信号是高电平有效的,但是我们会将这个res_n绑定到板子上的按键上,而按键是按下时属于低电平,所以我们需要反向连接到PLL的复位

output clk_out_200,

output clk_out_100,

output clk_out_50,

output clk_out_25

);

wire locked;

// 实例化pll的ip核

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

clk_wiz_0 clk_wiz_0_init

(

// Clock in ports

.clk_in1(sys_clk), // input clk_in1

// Clock out ports

.clk_out1(clk_out_200), // output clk_out1

.clk_out2(clk_out_100), // output clk_out2

.clk_out3(clk_out_50), // output clk_out3

.clk_out4(clk_out_25), // output clk_out4 我们只测试了一个25MHZ的频率

// Status and control signals

.reset(~res_n), // input reset

.locked(locked) // output locked

);

// INST_TAG_END ------ End INSTANTIATION Template ---------

endmodule

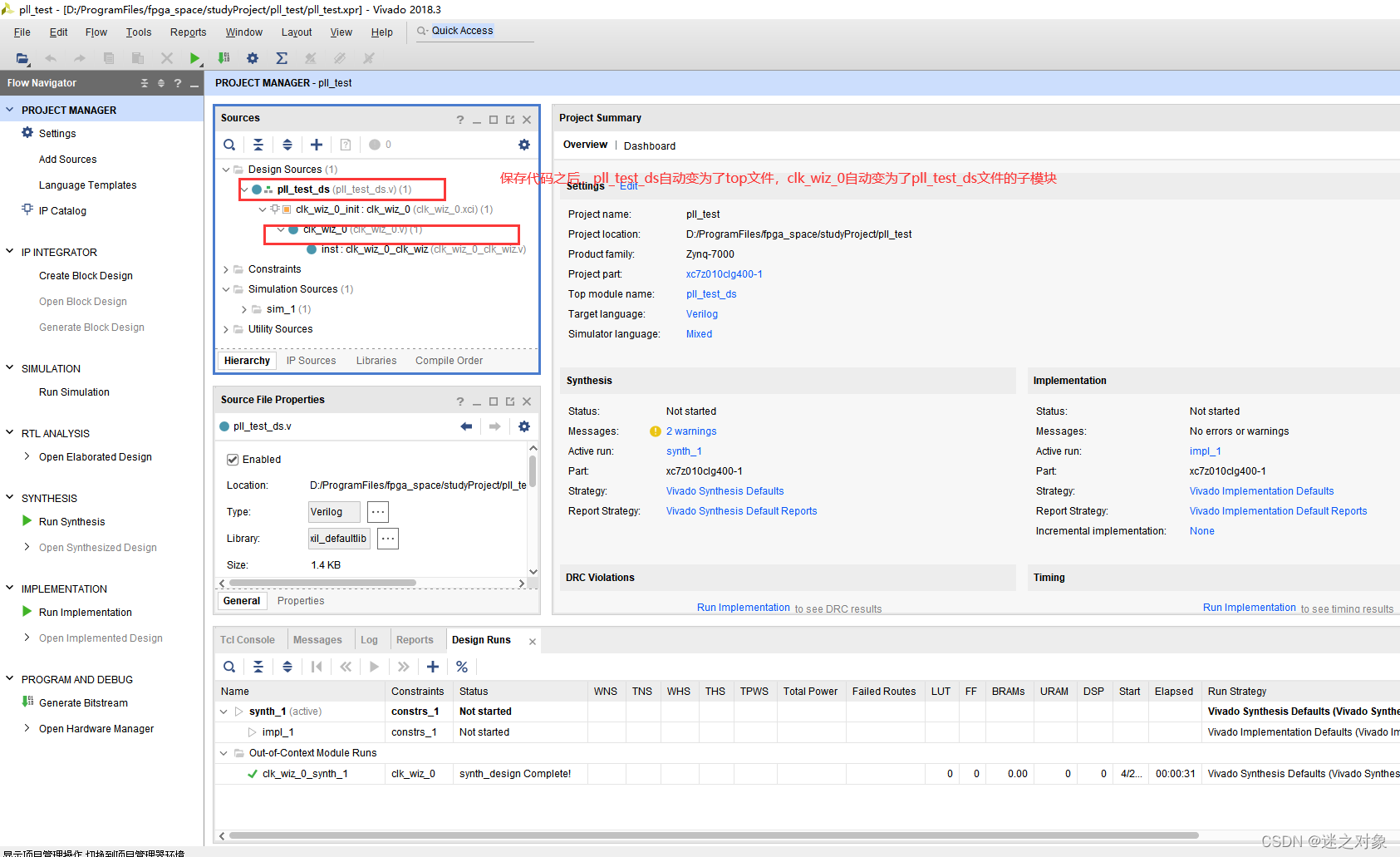

程序中先用实例化

clk_wiz_0 , 把单端 50Mhz 时钟信号输入到 clk_wiz_0 的 clk in 1 ,把clk_out4 的输出赋 给 clk _out

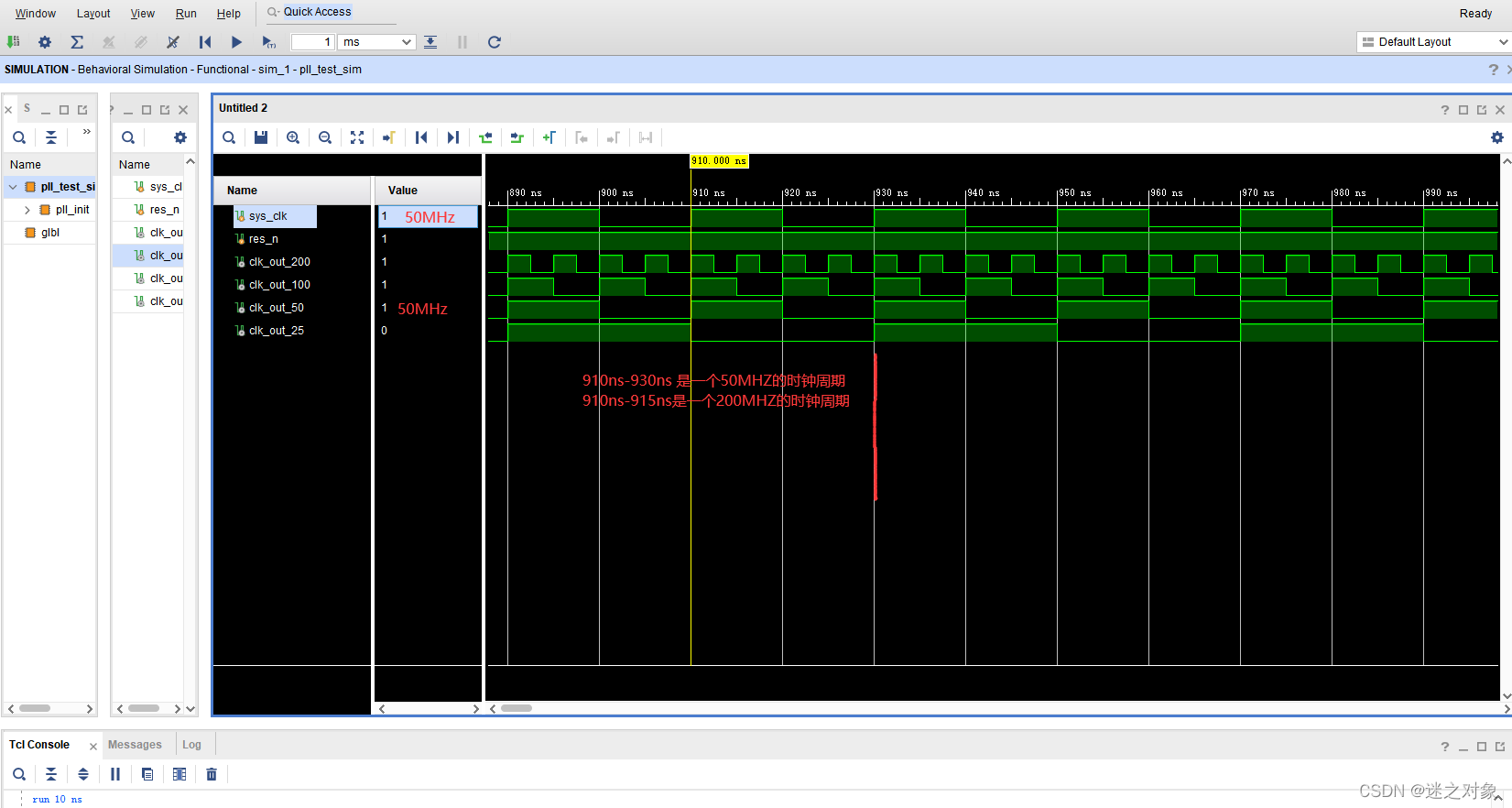

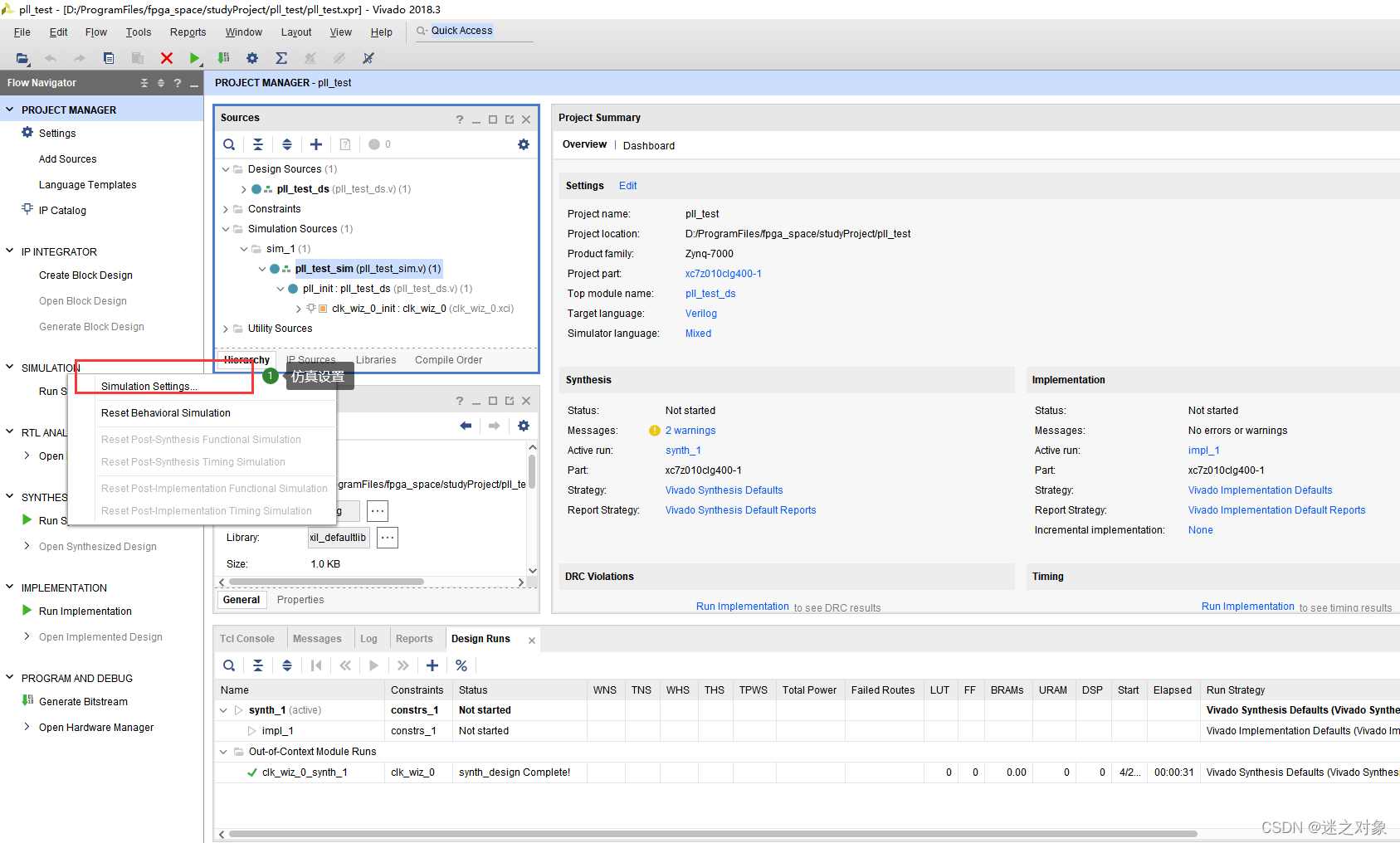

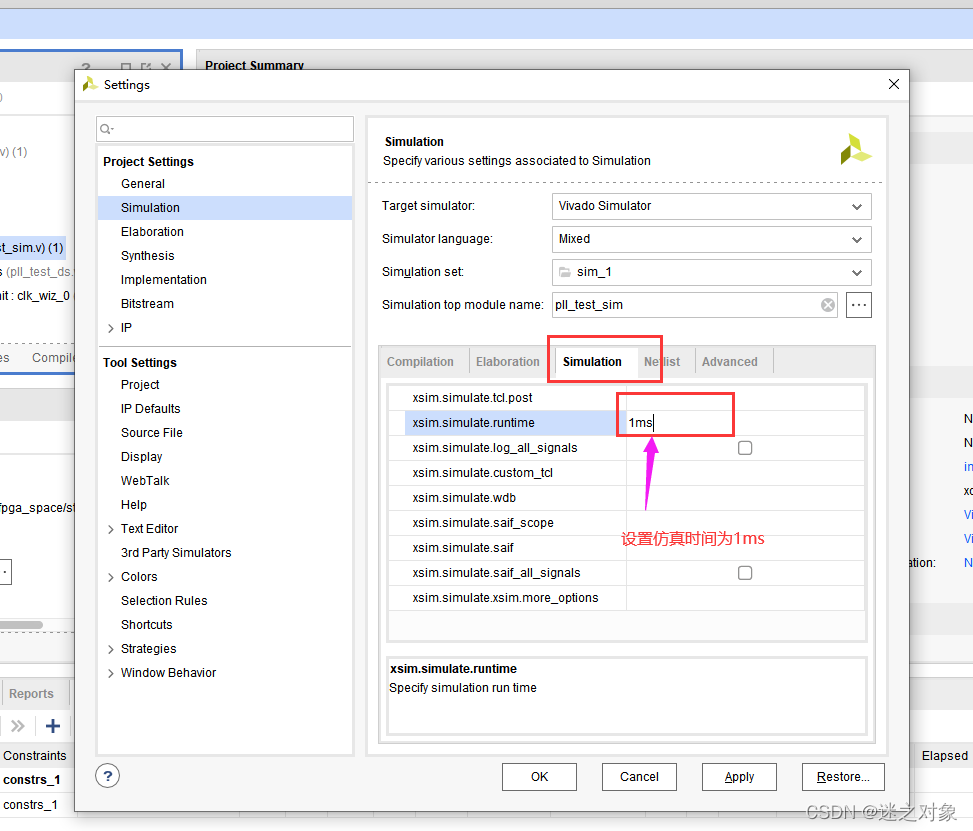

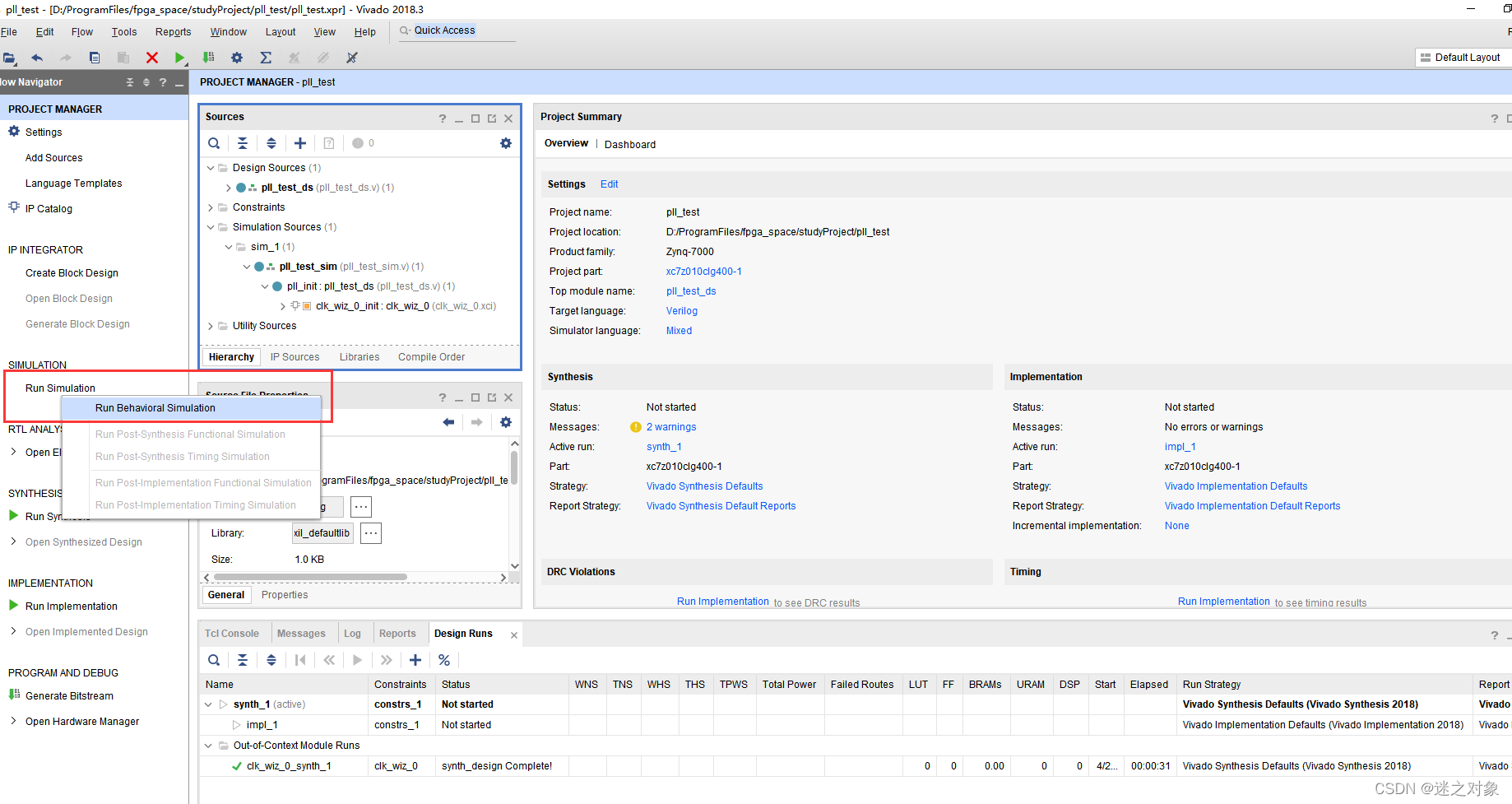

三、仿真

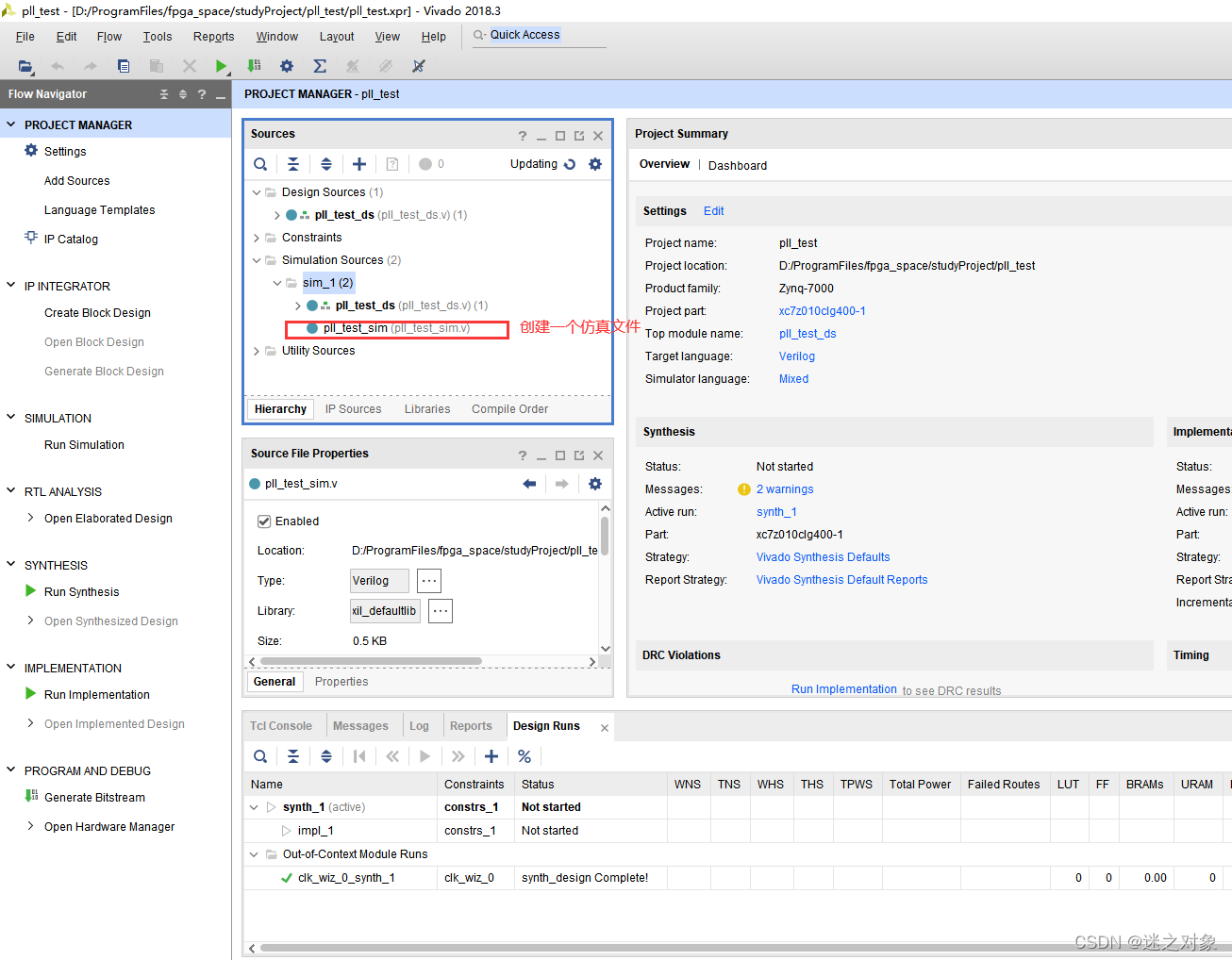

1、创建仿真文件

添加一个 vtf_pll_test 仿 真文件,运行后 PLL 的 lock 信号会变高,说明 PLL IP 锁相环已经初始

化完成。 clk_out 有时钟信号输出,输出的频率为输入时钟频率的 1/2, 为 25Mhz 。 仿真方法可

以参考 PL 的 ”Hello World”LED 实验 。

2、编写仿真代码

仿真代码如下

`timescale 1ns / 1ps

module pll_test_sim();

reg sys_clk;

reg res_n;

wire clk_out_200;

wire clk_out_100;

wire clk_out_50;

wire clk_out_25;

// 对pll_test_ds进行例化操作

pll_test_ds pll_init(

.sys_clk(sys_clk), // 模拟50MHZ

.res_n(res_n), // 模拟复位信号

.clk_out_200(clk_out_200), // 模拟输出200MHZ

.clk_out_100(clk_out_100), // 模拟输出100MHZ

.clk_out_50(clk_out_50), // 模拟输出50MHZ

.clk_out_25(clk_out_25) // 模拟输出25MHZ

);

initial begin

sys_clk = 1'b0; // 初始化

res_n = 1'b0; // 当为0的时候,模拟的是按键按下的时候,是处于复位状态的

#100 res_n = 1'b1; //过100ns把res_n给拉高,即相当于按键松开了,

end

always #10 sys_clk = ~sys_clk;//10ns之后将时钟进行翻转(即说明20ns为一个周期) 1/20ns = 1/2*10^(-8) = 5*10^7 = 50MHz 产生50MHz的时钟

endmodule

仿真结果