前言

《数字电子技术基础》第5.3、5.4、5.5节学习笔记

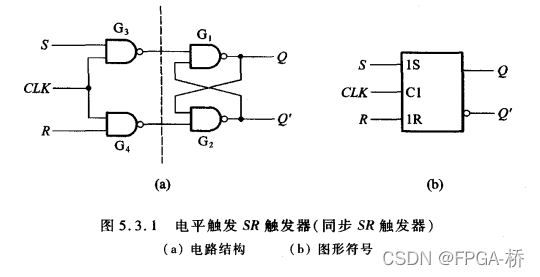

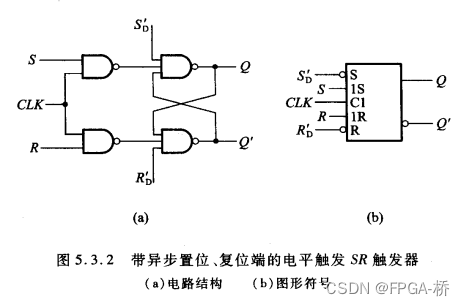

5.3 电平触发的触发器

一、电路结构和工作原理

在电平触发的触发器电路中,除了置位与复位输入端又增加了一个触发信号的输入端,来控制触发器是否有效,通常触发信号称为时钟信号(CLOCK),记作CLK。因此可以用于同步电路中。如将SR锁存器加入控制端CLF,变为SR触发器。

在某些应用场合,有时需要在CLK的有效电平到达前预先将触发器设置成指点状态,因此加入了两个提前控制端。在正常工作时控制端均处于高电平。

?二、电平触发方式的动作特点

- 只有当CLK变成有效电平时,触发器的控制端才有效,并按照输入信号将触发器的输出置成相应状态。

- CLK=1时,SR触发器实现的是SR锁存器功能;CLK=0时,则保存回到0以前瞬间的状态。当CLK=1器件SR的状态多次发生变化,那么SR触发器也随之改变,如果出现干扰时并不能进行屏蔽,故抗干扰能力差。

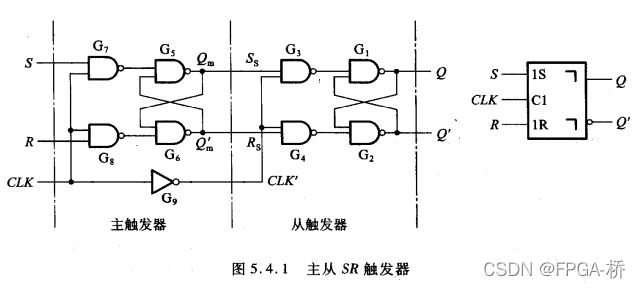

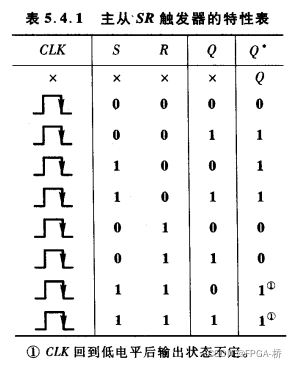

5.4 脉冲触发的触发器

一、电路结构和工作原理

为了解决电平触发器的问题,提高触发器的工作的可靠性,希望在每个CLK周期里输出端的状态只能改变一次,为此出现了脉冲触发的触发器。

当CLK为高电平时,主触发器有效对SR端进行存储,从触发器无效;只有当CLK为低电平时,主触发器无效,从触发器对主触发器存储的值进行判断输出。(下降沿触发)

?整体对外状态克服了在CLK=1期间触发器输出状态可能发生多次翻转问题。但由于主触发器本身是电平触发CLK=1期间主触发器的状态也会随着SR状态变化而变化。

二、脉冲触发方式的动作特点

- 触发器的翻转分为两步动作。第一步CLK=1,主触发器接受输入端的信号,从触发器不发生变化;第二步,CLK下降沿到来时从触发器按照主触发器的状态翻转,因此最后输出状态发正在CLK的下降沿(当CLK为低电平有效时,输出发生在上升沿)。

- 因为主触发器是电平触发的,所以在CLK=1时,主触发器一直处于运行状态。

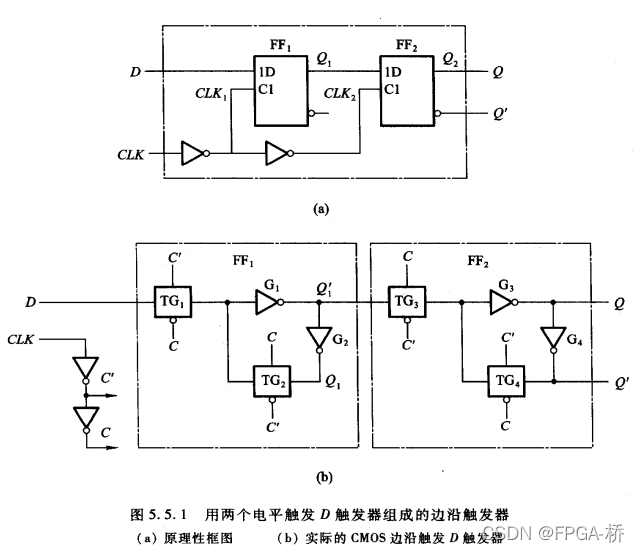

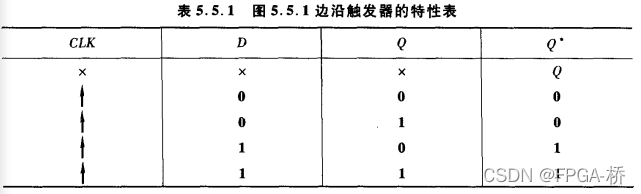

5.5 边沿触发的触发器

一、电路结构和工作原理

为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于CLK信号的下降沿(上升沿)到达时刻输入信号的状态。而在次之前和之后输入状态变化对触发器的次态没有影响。

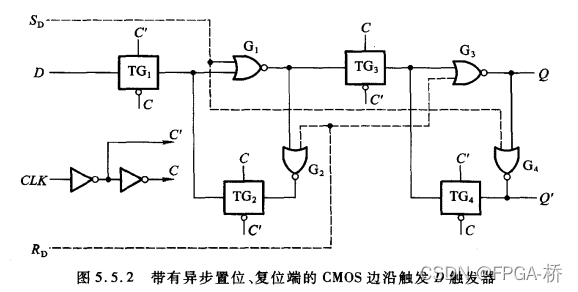

1、用两个电平触发D触发器组成的边沿触发器

?当CLK=0时,C'=1,C=0,此时TG1导通TG2截止,主触发器输出跟随输入状态,TG3截止TG4导通,从触发器输出处于自锁状态。

当CLK=1时,相反。而在CLK=0 -> CLK=1时,发生了从主触发器想从触发器传输状态。

?为实现异步置位’复位功能,引进SD和RD信号。

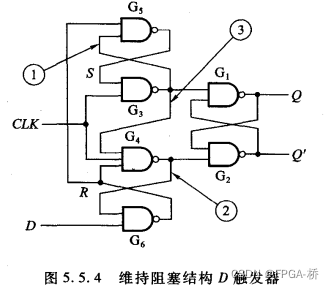

?2、维持阻塞触发器

边沿触发器的另一种电路结构形式是维持阻塞结构,TTL中较多。

?

?

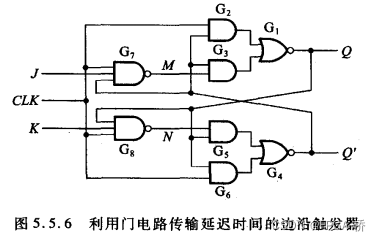

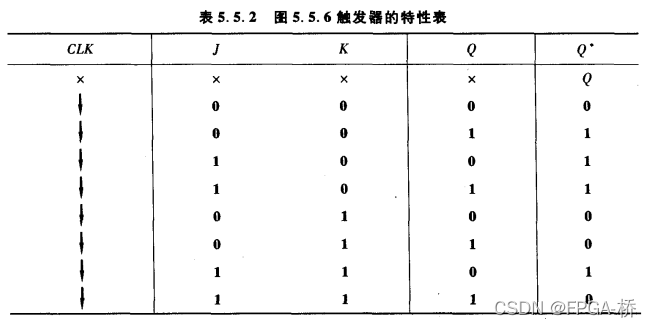

?3、利用门电路传输延迟时间的边沿触发器