同步复位与异步复位:

复位的目的有两个:

??一是仿真的时候使电路进入初始状态或者其他预知的状态;

??二是对于综合实现的真实电路,通过复位使电路进入初始状态或者其他预知状态。

复位逻辑可以保证电路能够从错误状态中恢复,可靠的工作。

同步复位:

??同步指的是与时钟同步。同步复位是指,当复位信号有效时,并不立即生效,只有当时钟上升沿采样到有效的复位信号后,才对触发器复位。(使用同步复位会增加更多的逻辑资源。

优点:

??1、使用同步复位可以设计 100%的同步时序电路,利于时序分析,其综合结果的频率往往较高

?? 2、同步复位仅在时钟的有效沿生效,可以有效的避免因复位电路毛刺造成的亚稳态和错误

缺点:

??1、很多目标器件(如 FPGA 和 CPLD)和 ASIC 库的触发器本身并不包含同步复位端口,使用同步复位会增加更多的逻辑资源

??2、同步复位的最大问题在于必须保证复位信号的有效时间足够长,才能保证所有触发器都有效的复位。要考虑时钟周期、同步复位信号树通过所有相关组合逻辑路径的延时以及由于时钟布线产生的时钟偏差(skew),只有同步复位的有效时间大于时钟的最大周期加上同步信号穿过的组合逻辑路径延迟加上时钟偏差时,才能保证同步复位可靠,彻底。

??3、使用同步复位可能使综合工具无法分辨复位信号和其他控制信号,导致进行复位的控制逻辑远离触发器。

异步复位:

??当复位信号有效时,无论时钟沿是否有效,立即对寄存器进行复位。

??大多数目标器件(如 FPGA 和 CPLD)和 ASIC 库的触发器都包含异步复位端口,异步复位会被直接接到触发器的异步复位端口。

优点:

??1、大多数目标器件(如 FPGA 和 CPLD)和 ASIC 库的触发器都包含异步复位端口,异步复位会节约逻辑资源。

??2、异步复位设计简单,没有复位路径上的组合逻辑延迟

??3、对于大多数 FPGA,都会有专用的全局异步复位/置位资源(GSR,Global Set Reset),使用 GSR 资源,异步复位到达所有寄存器的偏差(skew)最小。

??4、综合工具能自动推断出异步复位而不必加入任何综合指令

缺点:

??1、当异步复位释放时,如果异步复位信号的释放时间和时钟的有效沿到达时间几乎一致,则容易造成触发器输出为亚稳态,造成逻辑错误

??2、如果异步复位逻辑树的组合逻辑产生了毛刺,则毛刺的有效沿会使触发器误复位,造成逻辑错误

异步复位同步释放:

??由于异步复位释放时会产生亚稳态,导致逻辑错误,所以需要异步复位同步释放

??是指在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。这种方式,可以有效地继承异步复位设计简单的优势,并克服异步复位的上述风险与缺陷。

优点:可以节约器件资源,并获得稳定可靠地复位效果,是推荐的复位设计。

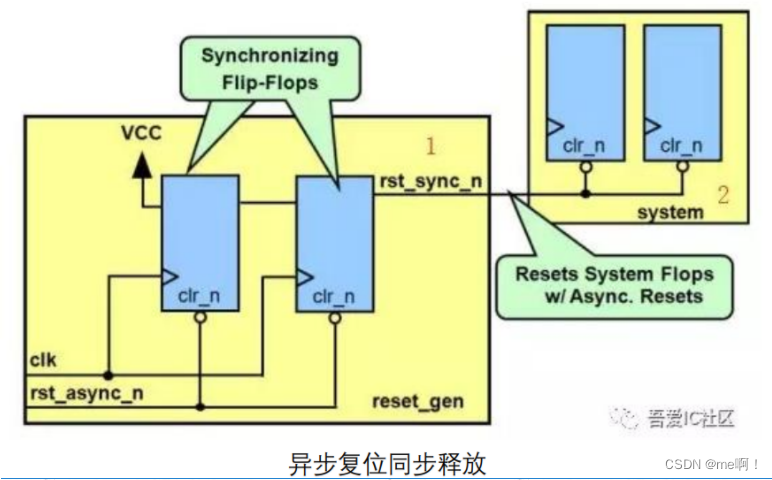

方框 2 是异步复位电路,方框 1 中的电路是实现异步复位同步释放的关键。

异步复位:

??当 rst_async_n 有效时,第一级 D 触发器的输出是低电平,第二个 D 触发器的输出 rst_sync_n 也是低电平,方框 2 中的异步复位端口有效,输出被复位。

同步释放:

??假设 rst_async_n 撤销时发生在 clk 上升沿,则第一级 D 触发器会产生亚稳态,可能输出高电平,也可能输出亚稳态,也可能输出低电平。

??此时,第二级触发器的输出值为第一级触发器上一周期的输出值。第一级触发器之前为低电平,故第二级触发器输出保持低电平。下一个时钟有效沿到来之后,第一级触发器的输出恢复稳定状态,可能是 0 也能是 1(是 0 的话,第二级触发器输出 rst_sync_n 保持低电平,电路还是处于复位状态,如果是 1 的话,第二级触发器输出 rst_sync_n 为高电平,电路处于正常工作的状态),同时第一级触发器采样到撤销的 rst_async_n,下一周期会输出高电平,即实现同步释放。

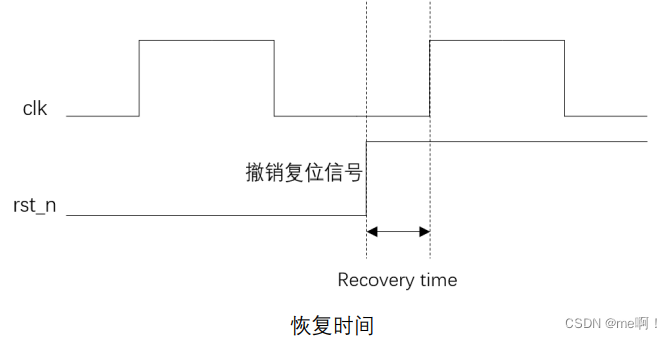

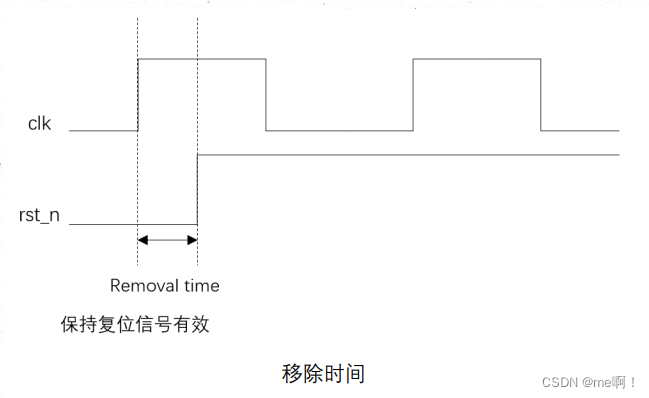

异步复位信号的恢复时间(Recovery time)与移除时间(Removal time)

恢复时间:是指在触发器的时钟上升沿到来之前,异步复位信号需要保持无效的时间。

恢复时间是对异步复位信号复位撤销的时间要求;

移除时间:是指在触发器的时钟上升沿到来之后,异步复位信号需要继续保持有效的时间。

移除时间是对异步复位信号复位有效的时间要求。

亚稳态产生的原因:

??异步时钟域的转换的核心就是要保证下级时钟对上级数据采样的建立时间和保持时间。

亚稳态:

??1、触发器恢复能力较强时,在一个时钟周期内恢复稳定的输出,随机稳定在0或1。

??2、触发器恢复能力较弱时,会在下一个有效时钟沿仍处于振荡状态,亚稳态传播。

危害:破坏系统的稳定性。

减少亚稳态传播的概率的方法:

??使用两级以上寄存器采样(可降低亚稳态概率,但不能确保第二级输出的稳态电平是正确电平);理论上如果再添加一级寄存器,使同步采样达到 3 级,则末级输出为亚稳态的概率几乎为 0。

??可以用纠错编码手段完成错误地纠正:MTBF

亚稳态解决办法::https://www.pianshen.com/article/1219302885/

??1、降低系统时钟频率

??2、用反应更快的 FF

??3、引入同步机制,防止亚稳态传播

??4、改善时钟质量,用边沿变化快速的时钟信号

??5、关键是器件使用比较好的工艺和时钟周期的裕量要大