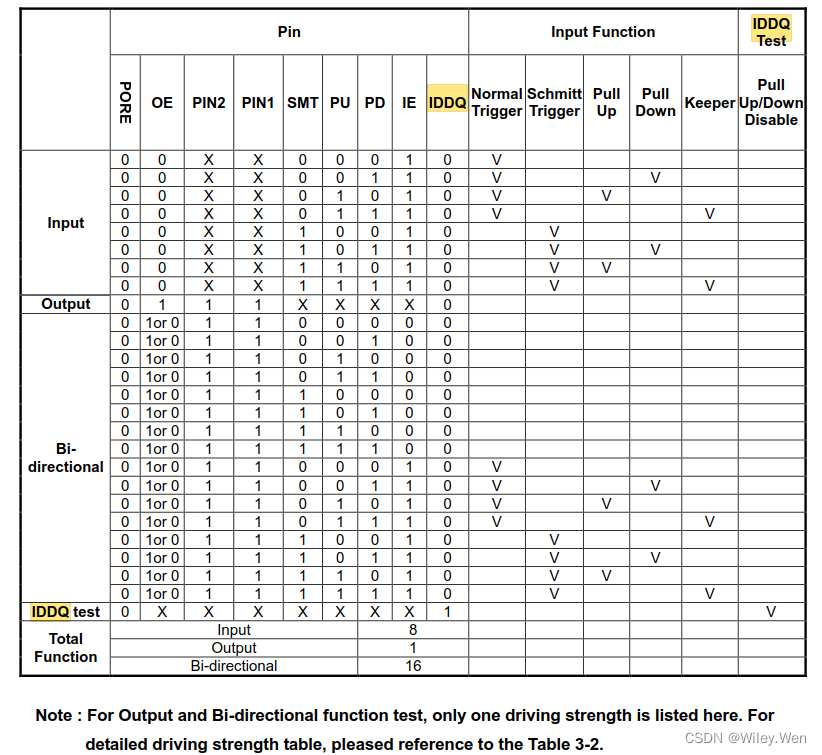

GPIO PIN

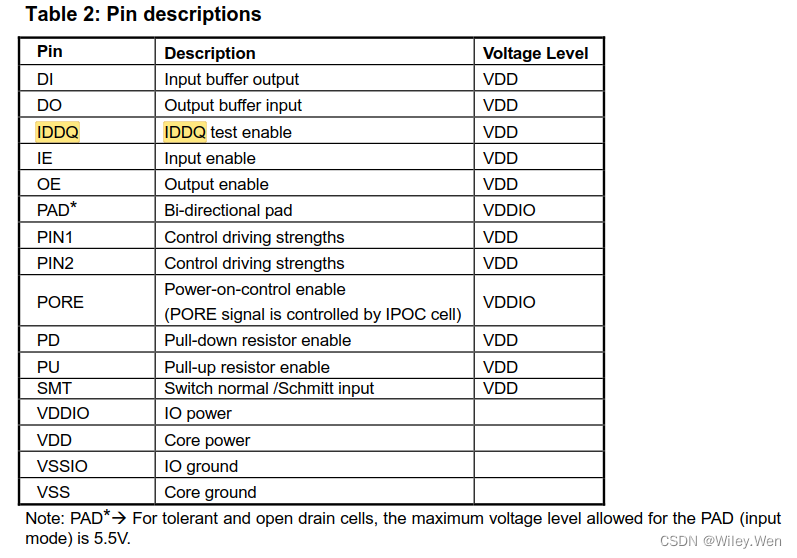

Function Table

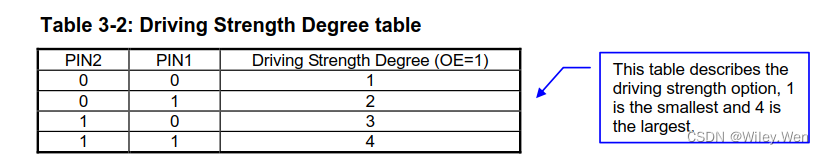

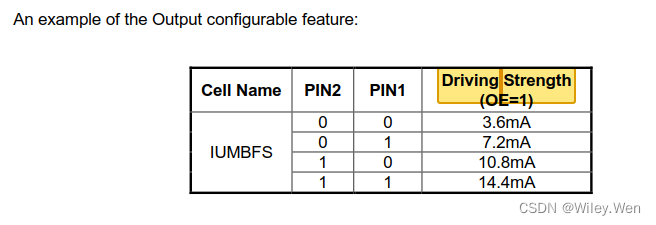

Driving Strength Degree table

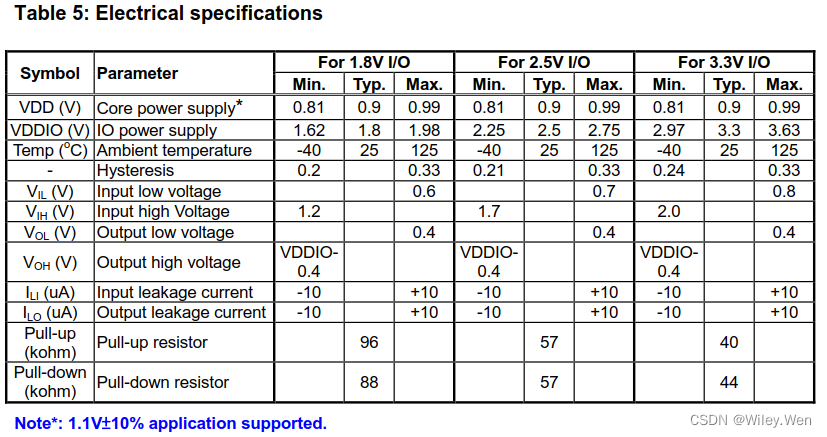

Electrical Specifications

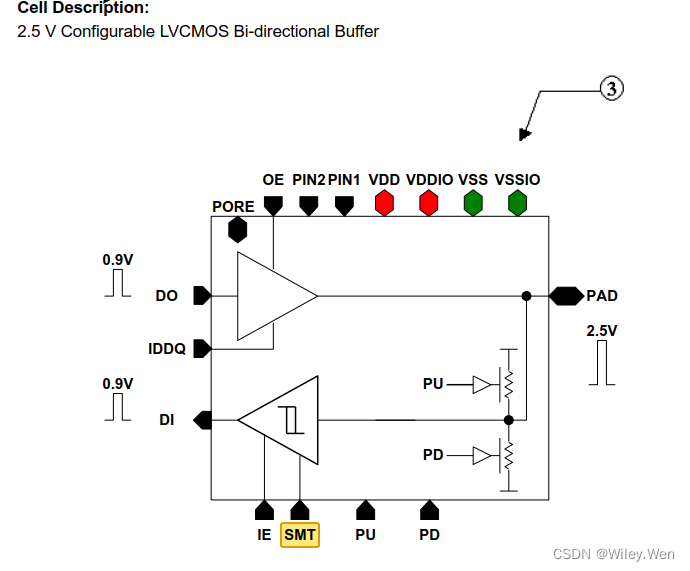

GPIO�Ľṹ

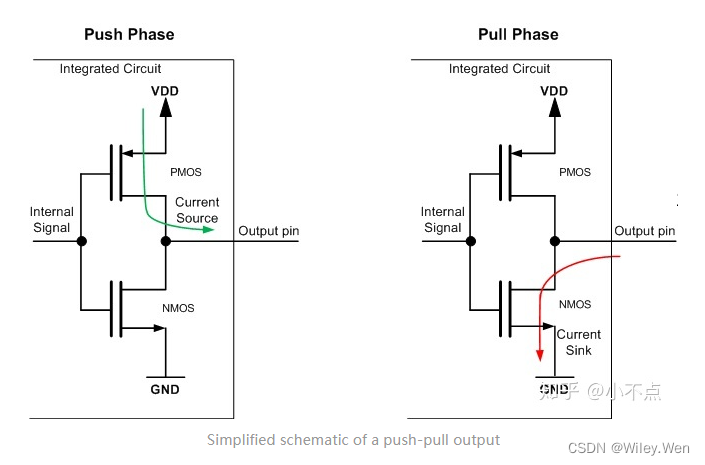

Push-Pull�ṹ(����)

����˼��,PUSH-PULL����νPUSHָ���ǰ�����Ƶ���·��VDD��ѹ,��νPullָ���ǽ��������Ground��ѹ��

����ͼ��ʾ,���Կ�������һ��PMOS��NMOS�����һ����Push-Pull�ṹ,�����ԭ������:

Push phase �C ��������Mos��դ����internal�ź�����Ϊ�͵�ƽ(Logic 0)��ʱ��,PMOS�ܵ�ͨ,������VDD����PMOS��������˿ڡ�

Pull phase �C ��������Mos��դ����internal�ź�����Ϊ�ߵ�ƽ(Logic 1)��ʱ��,NMOS�ܵ�ͨ,������Output������PMOS����GND��

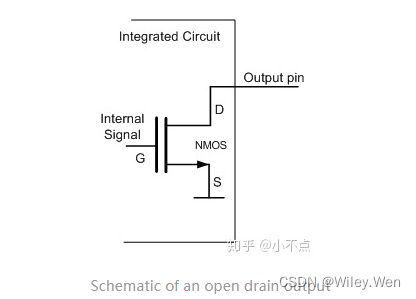

Open-Drain�ṹ(��©)

��ͼ��ʾ,���Կ�����©�����·����һ��N����MOS����ɵ�,��NMO�ܵ�ͨʱ,��·ͨ��NMOS�ܽ����������GND;��NMOS�ܹر�ʱ,��·����ܽŸ��ա�

��©�����·һ������ͨ�Žӿ�,��ͨ�Žӿ���ͬʱ����n���devices(����I2C�ṹ),����ͼ��ʾ,��Internal signal�ź�����ߵ�ƽ�������,NMOS�ܵ�ͨ,��������͵��͵�ƽ״̬;��Internal signal�ź�����͵�ƽ�������,NMOS�ܽ���,�������̬(����̬����̬�����ն���ʾһ����˼),��ʱ��·����û��չʾ���κ���������,��ʱ�������ⲿ��һ������������ʵ������ߵ�ƽ��

- ��©�������һ����һ�����Ե����ƾ��ǿ��Ժܷ���ĵ�������ĵ�ƽ,��Ϊ�����ƽ��ȫ�������������ӵĵ�Դ��ƽ��������������Ҫ���е�ƽת���ĵط�,�dz��ʺ�ʹ�ÿ�©�����

- ��©�������һ������һ���ô����ڿ���ʵ��"����"����,��ν��"����"ָ���Ƕ���ź���ֱ��������һ��,ֻ�е������ź�ȫ��Ϊ�ߵ�ƽʱ,����һ�������Ϊ�ߵ�ƽ;ֻҪ������һ�����߶���ź�Ϊ�͵�ƽ,������Ϊ�͵�ƽ������������Ͳ���,����ߵ�ƽ�͵͵�ƽ����һ��,����ֵ�������,��������

��open-drain��push-pull���ܽ

����GPIO��ģʽ������,�ڲ������Ƿ���Ҫ�������������������,������Ϊopen-drain����push-pull,˵����,���Ǹ�Ȩ�������:

�������Ҫ��ƽת���ٶȿ�Ļ�,��ô��ѡpush-pull,����ȱ���ǹ�����Ի��Щ��

�������Ҫ���ĵ�,��ͬʱ���С����롱�Ĺ���,��ô����open-drain��ģʽ��(ͬʱע��GPIOӲ��ģ���ڲ��Ƿ�����������,���û��,��ҪӲ����·�����Ӷ������������)[1]

IDDQ

IDDQ��ָ��CMOS���ɵ�·�е����й��Ӷ����ھ�ֹ״̬ʱ�ĵ�Դ�ܵ�����IDDQ����Ŀ���Dz�����״̬��֤ʱ�ľ�ֹ(�ȶ�����)�ĵ���,�������̬������Ƚ����������Ը����ʡ�

IDDQ��������һ�龲̬IDD���ԵĹ�������,�ڹ��������ڲ��ĸ��������Ķϵ�,����6-12�ζ����ĵ����������������е�Ŀ����,��ÿ���ϵ���֤��֤�ܵ�IDD����ʱ,�����ܶ�ؽ��ڲ����Ž��п�-�ص��л���

IDDQ������ֱ�ӷ���������·�����Ƿ�������������������Ľ�С�����ˡ�

SMT

ʩ���ش�����(Schmitt trigger ):�źž���ʩ���ش�����֮��,ģ���ź�ת��Ϊ�����ź�0��1��