FPGAʵ���¼��:״̬��ר����ϰ

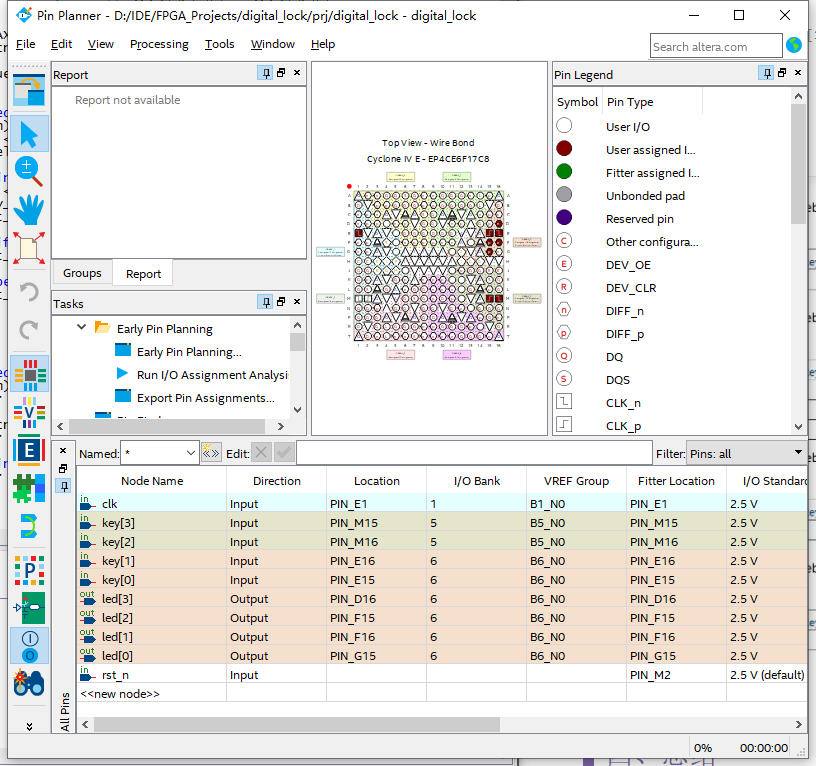

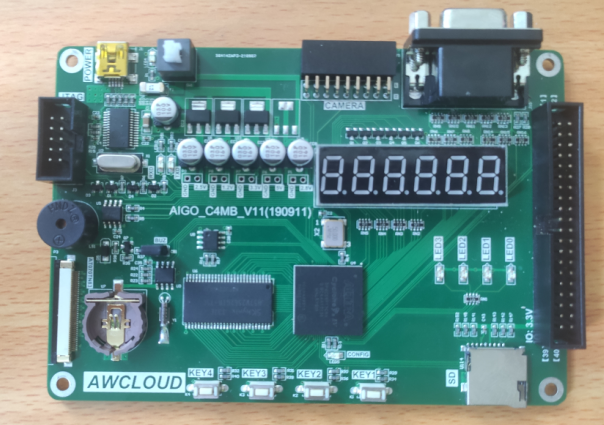

����:AWcloudC4 ������

IDE:QuartusII 18.1(Lite)

��������:Modelsim-Alterl

оƬϵ��:Cydone IV E

оƬ����:EP4CE6F17C8

оƬ����:EP4CE6

����Ŀ¼

ʵ��Ҫ��:

1��������������������verilog��дһ�δ���,����״̬����ʵ�ָù��ܡ�

(1)״̬��:ʵ��һ�����Թ���,�ù��̰���������״̬���������ԡ�ֹͣ���ԡ���ѯ���Խ������ʾ���Խ�������Խ������س�ʼ��6��״̬;��ʱ�������Ƹù���,90������ɸù���;

(2)����״̬��תʱ��;

(3)����ʵ�֡�

2. �������Լ��10010����״̬ͼ, ����verilog���ʵ��֮��

����״̬��

״̬��������״̬�Զ����ļ��,����ʵ�������й��������ɵ�һ����ѧģ�͡�

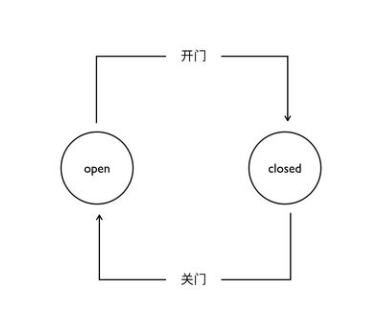

��������ʲô�ǡ�״̬��( State )����ʵ�������в�ͬ״̬��,����һ���Զ���,���� open �� closed ����״̬������ͨ����˵��״̬��������״̬��,Ҳ���DZ������������״̬������������,�����Զ��ŵ�״̬�������� open �� closed ��

״̬��,Ҳ���� State Machine ,����ָһ̨ʵ�ʻ���,����ָһ����ѧģ�͡�˵����,һ�����ָһ��״̬ת��ͼ������,�����Զ��ŵ����й���,���ǿ��Գ����������ôһ��ͼ��

�Զ���������״̬,open �� closed ,closed ״̬��,�����ȡ�����ź�,��ô״̬�ͻ��л�Ϊ open ��open ״̬�������ȡ�����ź�,״̬�ͻ��л�Ϊ closed ��

״̬����ȫ��������״̬�Զ���,�Զ�������Ҳ�ǰ�����Ҫ����ġ�����һ��״̬��,ͬʱ�������ĵ�ǰ״̬�Լ�����,��ô���״̬ʱ������ȷ����������ġ���������Զ���,������ʼ״̬ closed ,�������롰���š�,��ô��һ��״̬ʱ������������ġ�

����״̬���Ļ����������Ǿͽ�������ˡ��ظ�һ��:״̬��������״̬�Զ����ļ��,����ʵ�������й��������ɵ�һ����ѧģ�͡�

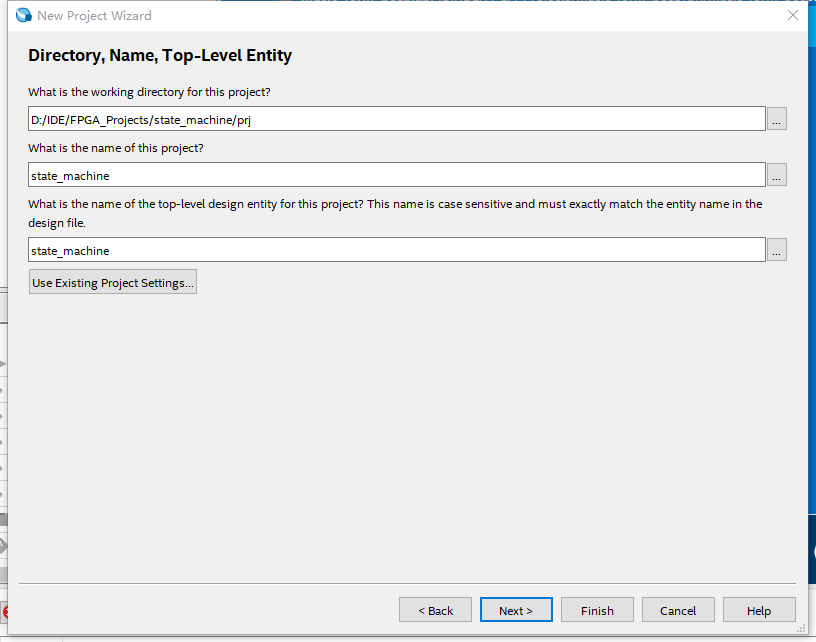

һ���½�����

�������: ������Թ��̰���������״̬���������ԡ�ֹͣ���ԡ���ѯ���Խ������ʾ���Խ�������Խ������س�ʼ��6��״̬;��ʱ�������Ƹù���,90s����ɸù���;

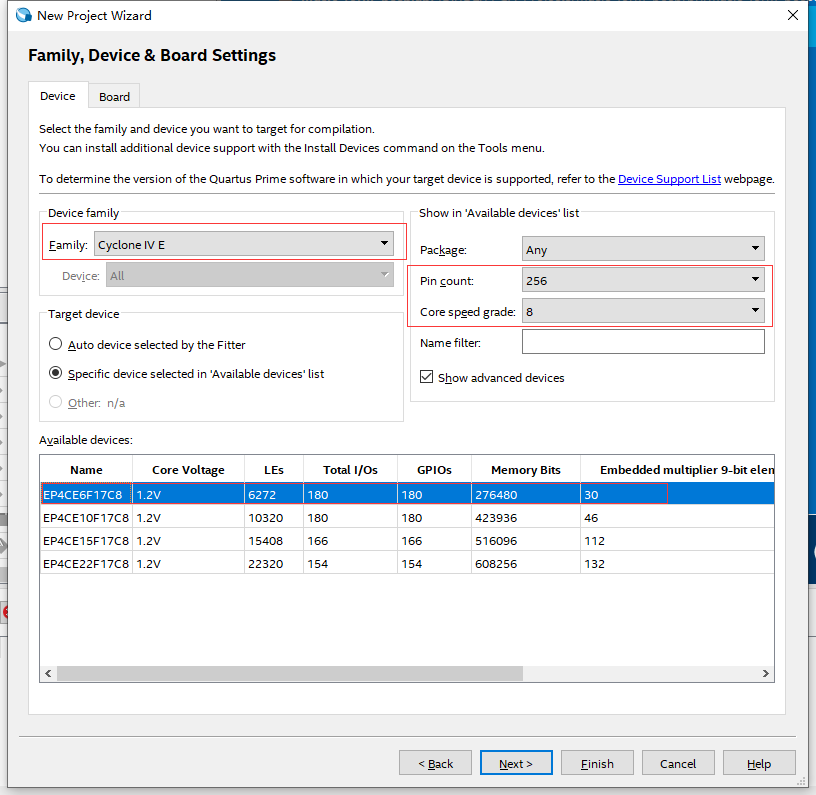

1. �½���Ŀ

- �½�һ����Ϊstate_machine����Ŀ

- ѡ��Cyclong IV Eϵ�е�оƬ,��������ѡ��256,

Core speed gradeѡ��8,оƬ����EP4CE6F17C8��оƬ,���next,����ѡ��ModelSim-Altera,Ȼ��finish��

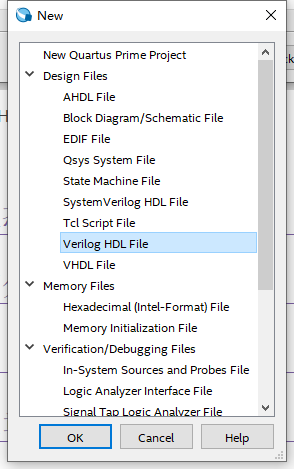

- �½�һ��Verilog HDL�ļ�

�������״̬��

1. ��Ƽ�ʱ��ģ��

AWcloudC4�������ʱ��Ƶ����50M/s,Ҫ����90s��ɰ���6��״̬������,����ƽ��ÿ��״̬��ʱ90/6=15s,��һ��״̬ʱ�ӻ���50M*15=750_000_000��

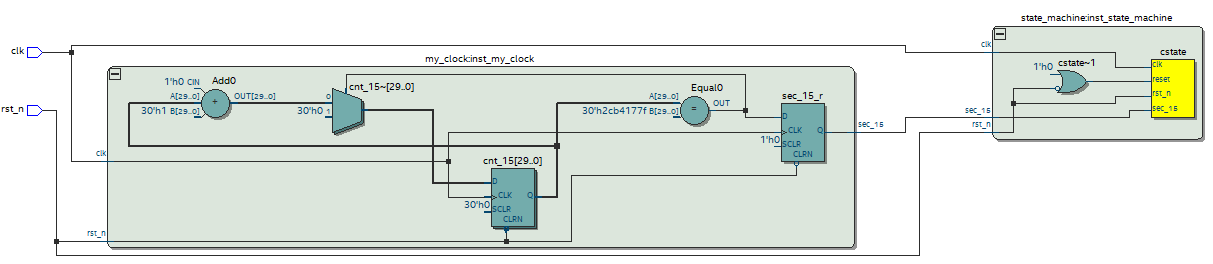

my_clock.v

//15s�����ź�

module my_clock(

input wire clk, //ʱ��,50MHZ

input wire rst_n, //��λ�ź�,�½�����Ч,negative

output wire sec_15//15s���һ�������ź�

);

parameter MAX_NUM = 30'd749_999_999;//�������15s,750_000_000��,Ϊ�˽�ʡ�ռ���ǰ-1

reg [29:0] cnt_15;//�����Ĵ���

reg sec_15_r;

//0.5s��ʱ��

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_15 <= 25'd0;

end

else if(cnt_15 == MAX_NUM)begin

cnt_15 <= 25'd0;

end

else begin

cnt_15 <= cnt_15 + 1'd1;

end

end

//0.5s�����ź�

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

sec_15_r <= 1'b0;

end

else if(cnt_15 == MAX_NUM)begin

sec_15_r <= 1'b1;

end

else begin

sec_15_r <= 1'b0;

end

end

assign sec_15 = sec_15_r;//���ұ߸ı�,������ֵ����� assign��always����

endmodule

2. ״̬���л�ģ��

module state_machine(

input clk,

input rst_n,

input wire sec_15

);

reg [2:0] cstate; //��̬

reg [2:0] nstate; //��̬

//״̬����

localparam state_ready = 0; //������״̬

localparam state_start = 1; //��������

localparam state_stop = 2; //ֹͣ����

localparam state_query = 3; //��ѯ���Խ��

localparam state_display = 4; //��ʾ���Խ��

localparam state_initialize = 5; //��ʼ��

//��һ��:��̬�����̬,ʱ����,��������ֵ

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cstate <= state_initialize;//��λ��������,��ǰ״̬����Ϊ��ʼ��

else

cstate <= nstate; //��һ��״̬��ֵ����ǰ״̬

end

//�ڶ���:�����,������ֵ

always@(*)begin

if(!rst_n)

begin

nstate = state_initialize;

end

else

case(cstate)

state_initialize: begin

if(sec_15 == 1'b1) //��״̬����ʱ��Ϊ1s,1s��,��һ��״̬����Ϊled1��

nstate = state_ready;

else

nstate = state_initialize;

end

state_ready: begin

if(sec_15 == 1'b1)

nstate = state_start;

else

nstate = state_ready;

end

state_start: begin

if(sec_15 == 1'b1)

nstate = state_stop;

else

nstate = state_start;

end

state_stop: begin

if(sec_15 == 1'b1)

nstate = state_query;

else

nstate = state_stop;

end

state_query: begin

if(sec_15 == 1'b1)

nstate = state_display;

else

nstate = state_query;

end

state_display: begin

if(sec_15 == 1'b1)

nstate = state_initialize;

else

nstate = state_display;

end

default: ;

endcase

end

endmodule

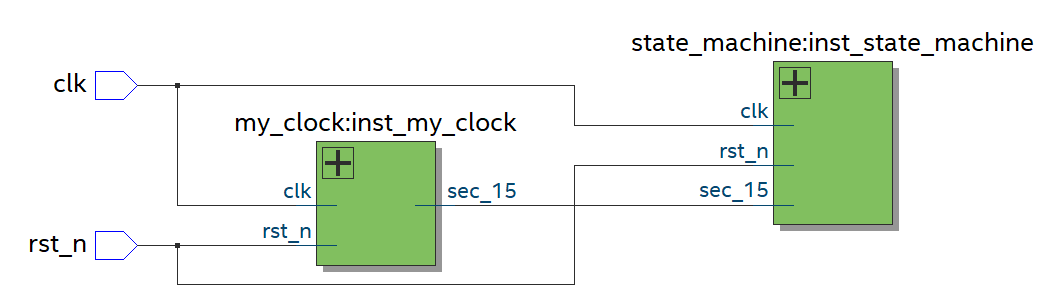

3. �����ļ�

module state_machine_top(

input wire clk,

input wire rst_n

);

wire sec_15;//������ģ����ź���������

//������ʱ��ģ��

my_clock inst_my_clock(

.clk (clk ),//ʱ��,50MHZ

.rst_n (rst_n ),//��λ�ź�,�½�����Ч,negative

.sec_15 (sec_15) //15s���һ�������ź�

);

//����״̬��ģ��

state_machine inst_state_machine(

.clk (clk ),//ʱ��,50MHZ

.rst_n (rst_n ),//��λ�ź�,�½�����Ч,negative

.sec_15 (sec_15) //15s�����ź�

);

endmodule

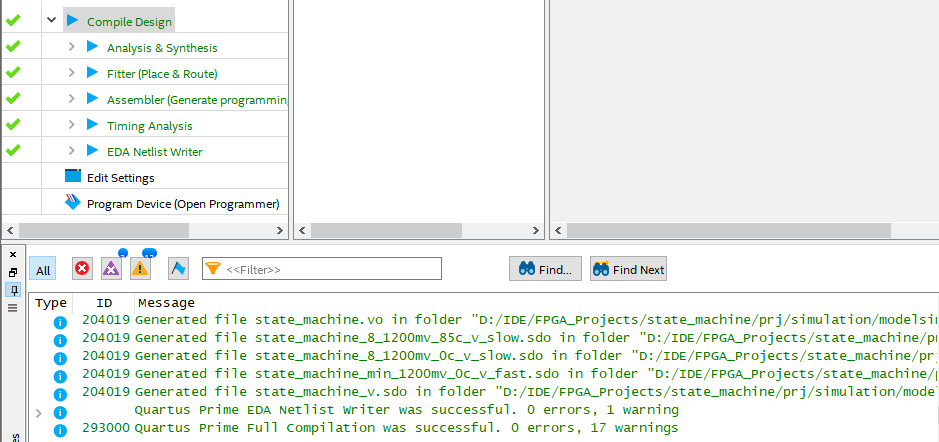

4. ������RTLview

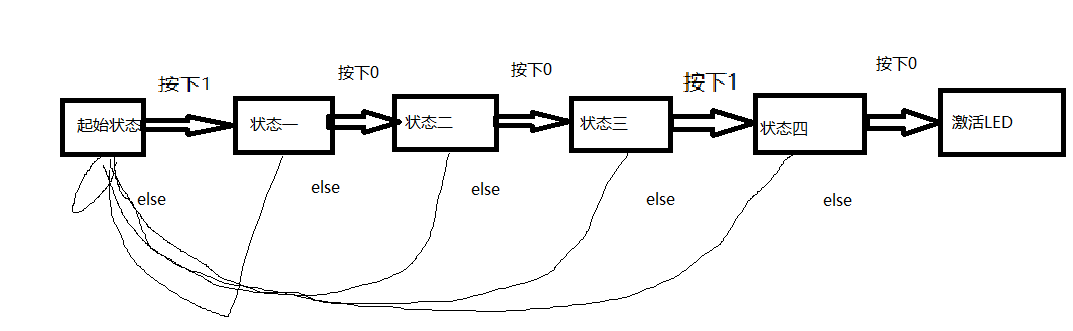

�����ܼ��10010��״̬��

���˼·������һ����������,ʹ��KEY1,KEY2�ֱ����0��1,����˳����10010ʱ,����һ��LED��ˮ�Ʊ�ʾ���ɹ�

1. �½�����

��ǰ��һ��,���ﲻ����

2. ��ư�������ģ��

module key_debounce(

input wire clk,

input wire rst_n,

input wire key,

output reg flag, //�ж϶����Ƿ������ı�־�ź�,0Ϊ����,1Ϊ��������

output reg key_value //�������ȶ��İ���ֵ����������ģ���LEDģ��

);

//����20ms�ӳټ�����,0.2s,1_000_000��

reg [19:0] delay_cnt;

//�Ĵ�����key��ֵ�����жϰ����Ƿ������ɹ�

reg key_reg;

//���°���20ms��ʱ������

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

begin

key_reg <= 1'b1; //��λ�ź�,���ð�����Ч

delay_cnt <= 1'b0; //����������Ϊ0

end

else

begin

key_reg <= key;

if(key_reg ^ key) //����һ��keyֵ����һ��keyֵ��һ��,֤�����ڶ���

delay_cnt <= 20'd1_000_000; //�ӳ�ʱ��20ms

else if(delay_cnt > 0)

delay_cnt <= delay_cnt - 1; //û�ж���,��ʼ20ms����ʱ

else

delay_cnt <= 1'b0;

end

end

//������ʱ��������ȡ����״̬�Լ�����ֵ

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

begin

flag <= 1'b0; //��λ�ź�,�����źű�־Ϊ����

key_value <= 1'b1; //���ó���ֵΪ1

end

else

begin

if(delay_cnt == 20'd1) //����ʱ1_000_000��1

begin

flag <= 1'b1;

key_value <= key; //�ȶ�20ms��keyֵ����key_value

end

else

begin

flag <= 1'b0;

key_value <= key_value; //20ms���Ȳ�ȡ��

end

end

end

endmodule

2. ��Ƶ�������ģ��

module state_machine_10010(

input clk,

input rst_n,

input [1:0] key,

output wire [3:0] led

);

parameter MAX_NUM = 24'd9_999_999;//0.2s��ʱ��

parameter T = 4'd10;//2s,100_000_000��

reg [2:0] cstate; //��̬

//״̬����

localparam state_0 = 0; //��ʼ״̬

localparam state_1 = 1; //����1

localparam state_10 = 2; //����10

localparam state_100 = 3; //����100

localparam state_1001 = 4; //����1001

localparam state_10010 = 5; //����10010

reg [3:0] cnt = 0; //��ʱ������ֵΪ0

reg [23:0] cnt_02 = 0;

reg time_flag;//��ʱ��־,1:��ʼ��ʱ,0:������ʱ

reg [3:0] led_r;

//0.2������ģ��

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt_02 <= 1'b0; //���¸�λ��,����

else if(cnt_02 == MAX_NUM)

cnt_02 <= 1'b0;

else

cnt_02 <= cnt_02 + 1'b1;

end

//2s������ģ��

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt <= 1'b0;//���¸�λ��,����

else if(time_flag == 1'b1)begin//��ʼ��ʱ

if(cnt_02 == MAX_NUM)begin

if(cnt < T)begin

cnt <= cnt + 1'b1;

end

else begin

cnt <= 1'b0;//cnt�����ﵽ�������

end

end

else begin

cnt <= cnt;//����ʱ�䱣��

end

end

else begin

cnt <= 1'b0;//����ʱ,cnt���

end

end

//״̬�л�ģ��

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

begin

cstate <= state_0;

end

else

case(cstate)

state_0: begin

if(key[1] == 1'b1) //��״̬����ʱ��Ϊ1s,1s��,��һ��״̬����Ϊled1��

cstate <= state_1;

else if(key[0] == 1'b1)

cstate <= state_0;

else

cstate <= state_0;

end

state_1: begin

if(key[0] == 1'b1)

cstate <= state_10;

else if(key[1] == 1'b1)

cstate <= state_0;

else

cstate <= state_1;

end

state_10: begin

if(key[0] == 1'b1)

cstate <= state_100;

else if(key[1] == 1'b1)

cstate <= state_0;

else

cstate <= state_10;

end

state_100: begin

if(key[1] == 1'b1)

cstate <= state_1001;

else if(key[0] == 1'b1)

cstate <= state_0;

else

cstate <= state_100;

end

state_1001: begin

if(key[0] == 1'b1)begin

cstate <= state_10010;

time_flag <= 1'b1;//��ʼ��ʱ

end

else if(key[1] == 1'b1)

cstate <= state_0;

else

cstate <= state_1001;

end

state_10010: begin

if(cnt == T)begin

cstate <= state_0;

time_flag <= 1'b0;//������ʱ

end

else

cstate <= state_10010;

end

default: ;

endcase

end

//������:����״̬���

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

led_r <= 4'b0001;

else

case(cstate)

state_10010:if(cnt_02 == 24'd4_999_999)

led_r <= 4'b1111;

else if(cnt_02 == MAX_NUM)

led_r <= 4'b0000;

else

led_r <= led_r;

default : led_r <= 4'b0001;

endcase

end

assign led = led_r;

endmodule

if(key[1] == 1'b1)

nstate = state_1001;

else if(key[0] == 1'b1)

nstate = state_0;

else

nstate = state_100;

end

state_1001: begin

if(key[0] == 1'b1)begin

nstate = state_10010;

time_flag = 1'b1;//��ʼ��ʱ

end

else if(key[1] == 1'b1)

nstate = state_0;

else

nstate = state_1001;

end

state_10010: begin

if(cnt == T)begin

nstate = state_0;

time_flag = 1'b0;//������ʱ

end

else

nstate = state_10010;

end

default: ;

endcase

end

//������:����״̬���

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

led_r <= 4'b0001;

else

case(cstate)

state_10010:if(cnt_02 == 24'd4_999_999)

led_r <= 4'b1111;

else if(cnt_02 == MAX_NUM)

led_r <= 4'b0000;

else

led_r <= led_r;

default : led_r <= 4'b0001;

endcase

end

assign led = led_r;

endmodule

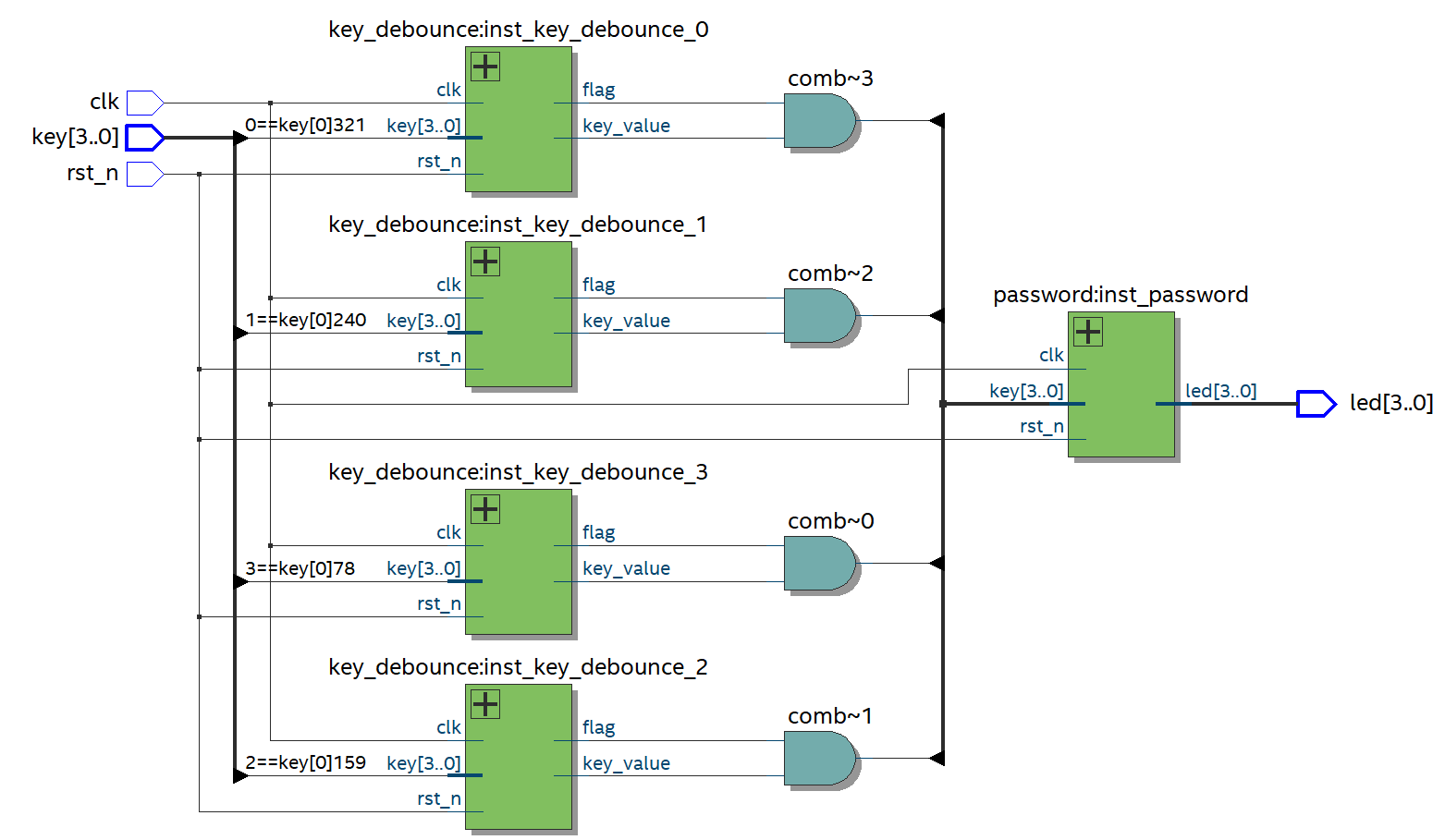

4. ��ƶ���ģ��

module state_machine_10010_top(

input wire clk,

input wire rst_n,

input wire [1:0] key,

output wire [3:0] led

);

wire [1:0] flag;

wire [1:0] key_value;

//��������KEY1

key_debounce inst_key_debounce(

.clk (clk ),

.rst_n (rst_n ),

.key (key[0] ),

.flag (flag[0] ), //�ж϶����Ƿ������ı�־�ź�,0Ϊ����,1Ϊ��������

.key_value(key_value[0]) //�������ȶ��İ���ֵ����������ģ���LEDģ��

);

//��������KEY2

key_debounce inst_key_debounce1(

.clk (clk ),

.rst_n (rst_n ),

.key (key[1] ),

.flag (flag[1] ), //�ж϶����Ƿ������ı�־�ź�,0Ϊ����,1Ϊ��������

.key_value(key_value[1]) //�������ȶ��İ���ֵ����������ģ���LEDģ��

);

//����״̬��

state_machine_10010(

.clk (clk ),

.rst_n(rst_n ),

.key ({~key_value[1]&&flag[1],~key_value[0]&&flag[0]}),

.led (led)

);

endmodule

5. RTLview

6. ����