ARM相关概念

1.ARM的发展史

1. 1978年,CPU公司

Cambridge processing Unit

2. 1979年

Acorn

3. 1985年, 32位,8MHz,

使用的精简指令集RISC

芯片的名字ARM ----> Acorn RISC machine

4.1990年,

iphone 150万英镑 VLSI: 25万英镑

ARM公司12工程师+技术专利:150万英镑

ARM公司-> Advanced RISC Machine

注:

ARM公司不生产芯片,做技术的授权,

提供解决方案。芯片厂家拿到技术授权之后,

根据需求设计生产自己的SOC。

5. 2016年

日本软银收购

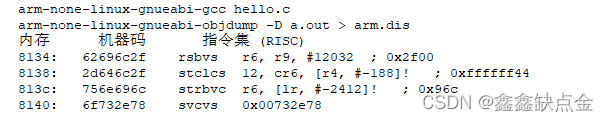

2.ARM精简指令集和复杂指令集的区别

精简指令集:RISC

在赋值指令集中提取一些比较简单的指令,

并且使用频率较高的指令,作为简单指令集,

精简指令集的宽度和周期固定。

宽度:一条指令在内存中所占空间的大小

周期:一条指令执行所需要的时间

处理器的工作频率:2.7GHz 1.8GHz 1.0GHz

处理器的主频就是处理器工作的时钟。

复杂指令集:CISC

复杂指令集,注重的是指令的功能性和运算能力,

复杂指令集,指令的周期和宽度都是不固定的。

3.ARM产品的分布

ARM内核:

早期ARM内核命令规范:

ARM7,ARM9,ARM10,ARM11

从ARM11之后,ARM公司对ARM内核命名规范为:Cortex

Cortex-A系列:

针对于高端,高性能处理器,

可以运行linux系统或者Android系统。

高通:

海思:

联发科:

NXP:

瑞星微:

Cortex-R系列:

主要针对于实时处理,摄像机,照相机

Cortex-M系列:(二线城市)

低端处理器,主要用于消费类电子产品,

一般不跑操作系统都是裸机开发。

ucosII LiteOS FreeRTOS AliOS

意法半导体(ST) : STM32 STM8

4.ARM中的数据宽度的约定

arm-v7架构:

char : 8bits

half world : 16bits

word : 32bits

double word : 64bits (cortex-A)

arm-v8架构:

char : 8bits

half world : 16bits

word : 32bits

double word : 64bits (cortex-A)

quad word : 128bits (arm-v8架构支持)

5.架构指令集的支持

1.ARM-v7架构指令集的支持

A32:ARM32位指令集

一条指令占32位宽度,

一条指令可以完成32位数据的运算

T16:Thumb16位指令集

一条指令占16位宽度,

一条指令可以完成32位数据的运算

2.ARM-v8架构指令集的支持

ARM-v8架构向下兼容ARM-v7架构。

Aarch32:

A32:ARM32位指令集

一条指令占32位宽度,

一条指令可以完成32位数据的运算 ---> ?寄存器的位数

T16:Thumb16位指令集

一条指令占16位宽度,

一条指令可以完成32位数据的运算

Aarch64:

A64:ARM64位指令集

一条指令占32位宽度,

一条指令可以完成64位数据的运算 ---> ?寄存器的位数

T32:Thumb32位指令集

一条指令占16位宽度,

一条指令可以完成64位数据的运算

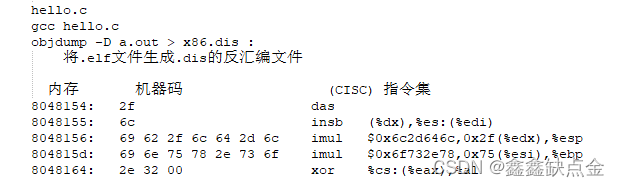

6.ARM处理器的工作模式

目的:为了提高ARM处理器的工作效率,

ARM处理器有很多中工作模式,

在不同的工作模式下,执行不同的代码,完成特定的功能。

ARM 有7个基本工作模式:

User : 非特权模式,大部分任务执行在这种模式

FIQ : 当一个高优先级(fast) 中断产生时将会进入这种模式

IRQ : 当一个低优先级(normal) 中断产生时将会进入这种模式

Supervisor(SVC) :当复位或软中断指令执行时将会进入这种模式

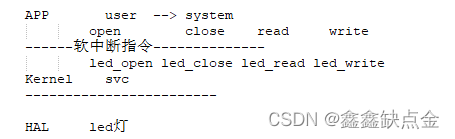

Abort : 当存取异常时将会进入这种模式

Undef : 当执行未定义指令时会进入这种模式

System : 使用和User模式相同寄存器集的特权模式

Cortex-A特有模式:

Monitor : 是为了安全而扩展出的用于执行安全监控代码的模式;

也是一种特权模式

异常模式参考图:

|----特权模式--|--异常模式-|-->fiq(快速中断)

| | |-->irq(普通中断)

| | |-->svc(特权模式/管理模式)

工作模式--| | |-->abort(中止异常模式)

| | |-->undef(未定义异常模式)

| |

| |

| |--非异常模式-->system

|

|----非特权模式--->user

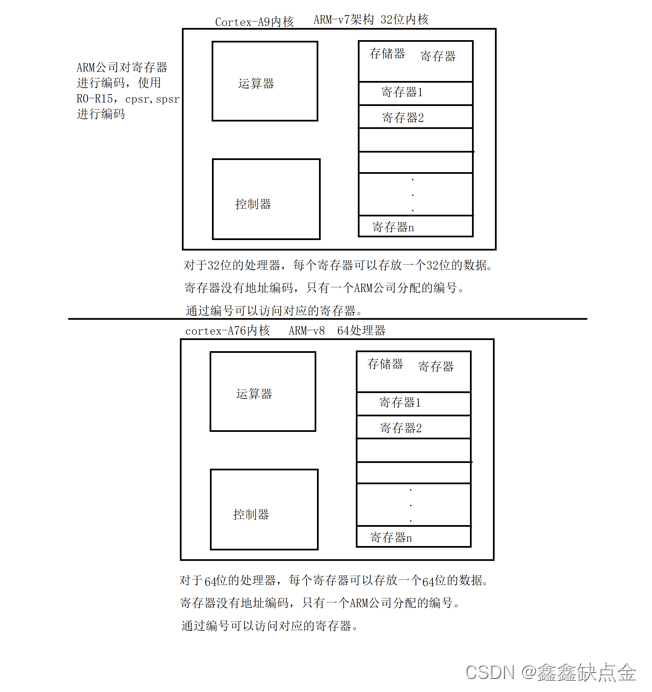

7.ARM内核中的寄存器组织

Cortex-A9内核 = 运算器 + 处理器 + 存储器。

存储器:指寄存器(Register/REG/reg)

寄存器理解参考图:

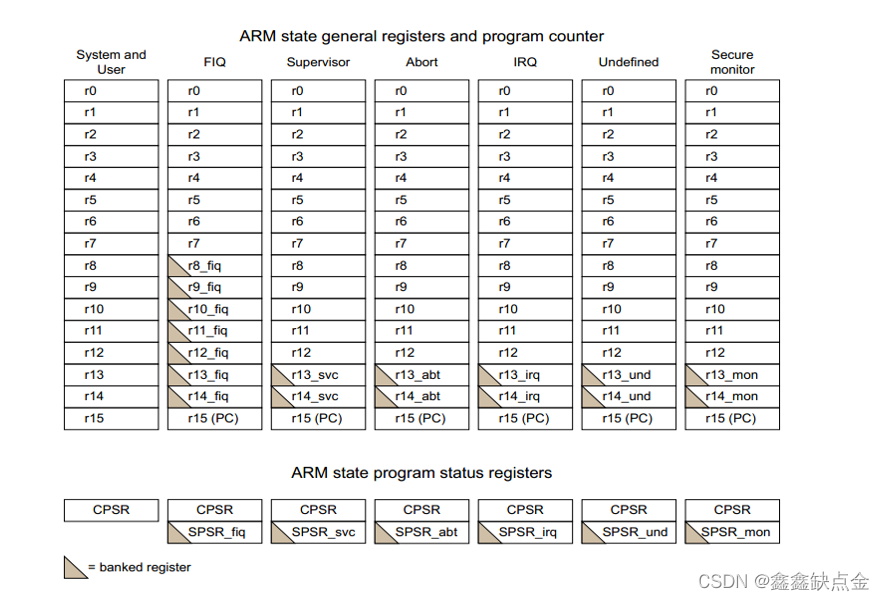

寄存器组织参考图:

不带三角的表示公有的,带三角的表示私有的。

在不同的工作模式下访问公有的寄存器,访问的是同一块空间。

在自己的工作模式下,如果说有私有的寄存器,

只能访问私有的寄存器,编号相同的公有的不能访问。

在ARM7, 9 , 11内核中有37个寄存器。

在cortex-A9内核中有40个寄存器。

在不同的工作模式下,只能使用自己本模式下的所有的寄存器,

不能使用其他模式下的寄存器。

ARM 有37个32-Bits长的寄存器.

1 个用作PC( program counter)

1个用作CPSR(current program status register)

5个用作SPSR(saved program status registers)

30 个通用寄存器

Cortex体系结构下有40个32-Bits长的寄存器

Cortex-A多出3个寄存器,Monitor 模式 r13_mon , r14_mon, spsr_mon

8.特殊的寄存器

r13 别名 sp (the stack pointor)

: 栈指针寄存器

用于存放栈顶的地址

r14 别名 lr (the Linking Register)

: 链接寄存器

用于存放返回地址

r15 别名 pc (the program counter)

: 程序计数寄存器

存放当前取指指令的地址

cpsr (current program status register)

: 当前程序状态寄存器

保存当前程序的运行状态

比如:程序的工作模式

spsr (saved program status register)

: 保存程序状态寄存器

模式切换是保存当前程序运行状态的寄存器

用于记录CPSR

9.cpsr详解

N[31] : 运算结果为负数,

N位被自动置1,否则为0

Z[30] : 运算结果为0,

Z位被自动置1,否则为0

C[29]:

加法 :

产生进位,C为被置1,否则为0

进位: 低32位向高32位进位。

减法 :

产生借位,C为被清0,否则为1

借位: 低32位向高32位借位。

比如: add R0, R1, R2 // R0 = R1 + R2

V[28]: 符号位发生变化,V位被自动置1,否则为0

I[7]:IRQ中断禁止位 全局中断禁止位

I = 0 使能IRQ中断

I = 1 禁止IRQ中断

F[6]:FIQ中断禁止位 全局中断禁止位

F = 0 使能FIQ中断

F = 1 禁止FIQ中断

T[5]:状态位

T = 0 ARM状态,执行ARM指令集

T = 1 Thumb状态,执行Thumb指令集

M[4:0]:模式位

0b10000 User mode;

0b10001 FIQ mode;

0b10011 SVC mode;

0b10111 Abort mode;

0b11011 Undfined mode;

0b11111 System mode;

0b10110 Monitor mode;

0b10010 IRQ mode;

其他没有使用的就是保留

10.大小端问题

大端对齐:

小端对齐:

编写代码测试大小端?

1> 强制类型转换

2> 联合体/共用体(union)

11.指令流水线(三级流水线)

ARM7内核 三级流水线

ARM9内核 五级流水线

ARM11内核 八级流水线

Cortex-A9 十三级流水线 arm公司未开源哪13级

流水线好处:提高代码的执行效率。

三级:取指器,译码器,执行器

以上三个器件是独立运行,互不干扰,每个都是单周期的器件。

取指器:从内存中根据PC中的值,一条一条的取出指令,给到译码器。

译码器:对指令进行翻译,给打对应的执行器。

执行器:执行对应的指令,将结果写到对应的寄存器中。

指令1 指令2 指令3 指令4 指令5 指令6

1T 取指

2T 译码 取指

3T 执行 译码 取指

4T 执行 译码 取指

5T 执行 译码 取指

6T 执行 译码 取指

7T 执行 译码 取指

8T 执行 译码 取指

8 / 6 约等于 1

以上流水线是理想情况,实际不可能达到这种理想的情况,

会有很多情况会打断流水,比喻函数的调用,中断。

PC寄存器取指完成之后,PC寄存器中地址值会自动加4指向下一条指令。