1?Ϊʲô��Ҫ��������

????��ңԶ�ĵ�Ƭ��ʱ��,Ƕ��ʽ�豸���ܱȽϵ�һ,ÿ���豸ֻ��Ҫִ��һ��������,�����ϵͳ��ʼ����ɺ�,�����������һ����ѭ����,��ʱ,ϵͳ�������̺��ܴ��벢û�к��ϸ�����֡�

????����CPU����������оƬ���칤�յIJ�������,������оƬ���ݽ�����SOC,����оƬ�ϳ���CPU��Ἧ�ɴ�����ͬ���ܵ�IP��,���жϿ�������DSP��GPU�����߿���������Ƶ�����ͱ���ģ�顢�Լ���Դ����ģ��ȡ�Ϊ�˸��õع�����Щ��Ӳ����Դ,�Լ�Ϊ�ϲ��û��ṩͳһ�ķ���ͽӿ�,SOC��һ�㶼��Ҫ���в���ϵͳ��ϵͳ����������Ҫ���ܾ��dz�ʼ��ϵͳ����Ӳ��״̬,Ϊ����ϵͳ�ṩһ�����ʵ���Ӳ������,�Լ����غ���������ϵͳӳ��

2?��Ӳ���ٶ�

????Ϊ�˸��õ������������̵�ϸ��,������½����ǽ�ѡȡһ��������Ӳ��ƽ̨��������������ۡ�Ӳ��ƽ̨ѡ��qemu��virt machineƽ̨,����ҪӲ����������:

(1)cpuΪarmv8�ܹ���cortex-a53��

(2)�жϿ�����Ϊgicv3

(3)ROM�ռ�128k

(4)SRAM�ռ�384k

(5)DDR�ڴ�ռ�3G

(6)֧��semihosting������ģʽ

????ѡ��qemu����Ϊ����һ��Ӳ��ģ����,����ͨ������ģ��ķ�ʽʵ�ֲ�ͬӲ��ƽ̨�Ĺ���,�������X86������ģ��armv8�ܹ���Ӳ��,�Ӷ������ڲ���ҪtargetӲ��������½�����ع��ܵĵ��ԡ�qemu���Ի����Ĵ�ɲο����µ�����:

��0��ʼ�qemu���Ի���

�������ܹ�����:

(1)��ʼ��������ʹ��arm ATF

(2)�ں���������ʹ��uboot

(3)�ں�Ϊlinux

3?������

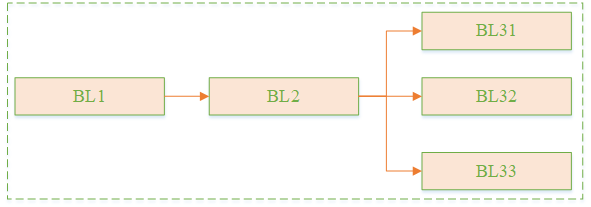

????Armv8���������̰��������,���͵���BL1��BL2��BL31��BL32��BL33,��������IJ�ͬ,��Щ�ο����ʵ��زü������ӡ�Ϊ�˷�������,�������ǵ����۽�����������Щ�ٷ�����ı���,���ǵ�Դ��ᱻ����ɶ�������������,�������浽�ض��Ĵ洢�����С�����һ��Ĵ洢����(��spi flash��nand flash��emmc��ssd��)����֧�ִ����ֱ��ִ��,�����Ҫ������ʱ�Ƚ�������ص���ֱ��ִ�д���Ĵ洢����,��SRAM��DDR��,Ȼ��������ش��롣����͵ļ�����������:

- BL1�������ĵ�һ��,�þ������Ҫ�洢�ڿ�ֱ��ִ�еĽ����С���оƬ֧��XIP������ʽ,��ɱ��洢��Ƭ���ֱ��ִ�еĽ�����(��norflash)������֧��XIP,����Ҫ�洢��оƬ��Ƭ��ROM��,��ʱ��оƬ������ò��ִ���ͽ����̻�,������Ҳ���ܱ��ĺ���������оƬҪ֧�ְ�ȫ����,����Ҫ��bootrom��Ϊ����ʱ�����θ�,��ʱ�����Խ���,SOC�������XIP�����ڰ�ȫ�������ǽ��ں���ר�Ž���

- BL2������BL1����,��ʱDDR��û�б���ʼ��,�������Ҫ�����ص�Ƭ�ڵ�SRAM��ִ��,һ��������λ����DDR�ij�ʼ��,��˺���ľ����Ա����ص�DDR�С�����ͼ��֪,BL31��BL32��BL33������BL2���ص�,����BL31��BL32�ǿ�ѡ��,��ϵͳ��֧��TRUST OS,���ȥ��BL32,����֧��EL3�쳣�ȼ���secure monitor,���ȥ��BL31

- BL33һ��ָuboot,һ��ͨ����������������ϵͳ�ں�

Armv8�ܹ����͵�������������:

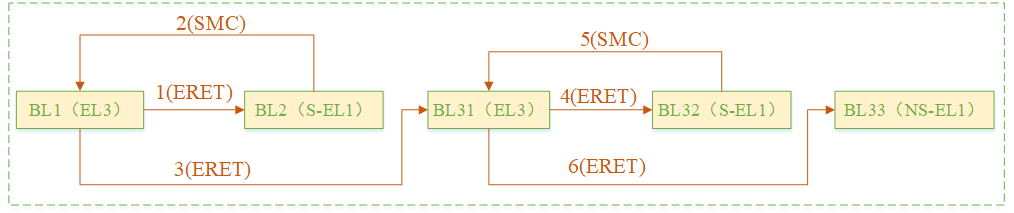

????�������������Ǽٶ�ϵͳ֧�ֵ�����쳣�ȼ�ΪEL3,��֧��secure monitor��TRUST OS,ͬʱBL2������secure EL1,BL33������non secure EL1״̬

(1)����armv8�ܹ��涨,arm�˸�λ��Ĭ�ϻ���뵱ǰϵͳ֧�ֵ�����쳣�ȼ�,���BL1������EL3,��ִ����ɺ��ͨ���쳣����ERET�ķ�ʽ��ת��BL2

(2 - 3)BL2ִ����ɺ���Ҫ��ת��BL31,����BL31������EL3�쳣�ȼ�,��BL2��������ͬ����������secure EL1��EL3����BL2������EL3ʱ��ֱ��ͨ��ERET��ʽ��ת��BL31��,������������secure EL1ʱ,��ֻ��ͨ��smc�쳣��������EL3�쳣�ȼ�����Ȼ,��ʱBL31������δ������������smc�쳣�����������ֱ�Ӵ������쳣,���,Ϊ�������ת����,BL1��Ҫ�ȴ������쳣�Ĵ��������BL1���˳�֮ǰ������smc�쳣��������,BL2����smc����BL31ʱ,BL1������쳣������BL2����IJ�������BL31����ڵ�ַ��ϵͳ��ʼ״̬,��ͨ��ERET��ת��BL31����ڵ�ַ��ִ��

(4)BL32�λ�����TRUST OS,��������secure EL1�쳣�ȼ�,BL31�ɸ����侵�������Ϣ������ڵ�ַ�Լ�����״̬,�������ת

(5 - 6)BL32������ɺ�ͨ��SMC���ص�BL31,Ȼ����BL31��ת��non secure EL1��ִ��BL33

4?��Ҫ�Ĵ�������

????����Ӳ��Ĭ�����õļĴ���ֵ֮��,�����Ĵ�������Ҫ��ϵͳ����ʱ��ʼ��,��Щ��Ҫ�ļĴ�����ϵͳ���������л�Ӱ��ϵͳ��������Ϊ,��������������һ���ܡ�����armv8�ܶ�Ĵ�����Ϊ��ͬ�쳣�ȼ��ṩ�˶�Ӧ��bank����,���京��Ƚ�����,Ϊ�˷������,������������Ƕ���EL3�ȼ��µĶ���Ϊ��

4.1?SCTLR_EL3�Ĵ���

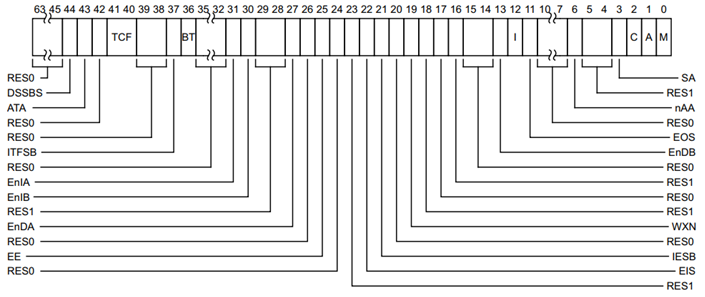

????�üĴ�����ϵͳ���ƼĴ���,�����ṩϵͳ������״̬������Ϣ,�䶨������ͼ:

��ÿ��bit�ĺ���ɲο�armv8�ο��ֲ�,�������һЩ�üĴ�������Ҫ����λ:

(1)M[0]:��������ϵͳ�Ƿ�ʹ��EL3�µ�MMU,����Ϊ1ʹ��MMU,�����ֹMMU

(2)A[1]:���������Ƿ�ʹ��El3�µĶ�����,����Ϊ1ʹ�ܶ�����,������ƶ�����

(3)C[2]:��������EL3�µ�����cache,����Ϊ1ʹ������cache,�����ֹ����cache

(4)I[12]:��������EL3�µ�ָ��cache,����Ϊ1ʹ��ָ��cache,�����ָֹ��cache

(5)WXN[19]:��������EL3��дȨ���ڴ��Ƿ�ִ��,����Ϊ1����дȨ���ڴ治����ִ��Ȩ��,����û�и�����

(6)EE[25]:��������EL3�Ĵ�С��,����Ϊ0����ΪС�˸�ʽ,����Ϊ��˸�ʽ

4.2?SCR_EL3�Ĵ���

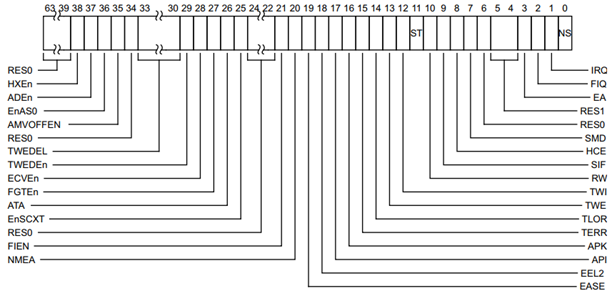

????�üĴ�����������secure��ص�����,���������쳣�ȼ��²�����bankֵ,�������ڿ���ȫ��״̬�ġ�����ڲ�ͬ�쳣�ȼ��л�֮ǰ,��Ҫ�Ƚ��üĴ�����ֵ����ΪĿ���쳣�ȼ������ֵ,���EL3�л���non secure EL1,����Ҫ��������Ϊnon secure EL1��ص����á��Ĵ����Ķ�������:

����Ҫ��bitλ����:

(1)NS[0]:����EL0- EL2��secure״̬,����Ϊ0��ʾsecure״̬,Ϊ1��ʾnonsecure״̬

(2)IRQ[1]:��������irq�ж�·��,����Ϊ1ʱ,irq�ж϶���·�ɵ�EL3����,����Ϊ0ʱ,����ǰ������EL3��irq�жϲ�����,����irq�ж�·�ɵ���ǰ���е��쳣�ȼ�,����·�ɵ�EL3

(3)FIQ[2]:��������fiq�ж�·��,����Ϊ1ʱ,fiq�ж϶���·�ɵ�EL3����,����Ϊ0ʱ,����ǰ������EL3��fiq�жϲ�����,����fiq�ж�·�ɵ���ǰ���е��쳣�ȼ�,����·�ɵ�EL3

(4)EA[3]:���������ⲿabort��serror·��,����Ϊ1ʱ,�ⲿabort��serror����·�ɵ�EL3����,����Ϊ0ʱ,����ǰ������EL3��serror������,�ⲿabort·�ɵ�EL3,�����ⲿabort��seeror��·�ɵ���ǰ���е��쳣�ȼ�,����·�ɵ�EL3

(5)SMD[7]:���������Ƿ����smc�쳣,����Ϊ1����smc,����ʹ��smc

(6)HCE[8]:���������Ƿ����hvc�쳣,����Ϊ1ʹ��hvc,�������hvc

(7)ST[11]:��������secureEL1�Ƿ�counter��securetimer�Ĵ�������·�ɵ�EL3������Ϊ1,secureEL1����counter��securetimer�Ĵ�������·�ɵ�EL3,�����bit������

(8)TWI[12]:��������EL0 �C EL2ִ��WFIʱ�Ƿ�����EL3������Ϊ1���κ�WFI������������EL3,�����bit������

(9)TWE[13]:��������EL0 �C EL2ִ��WFEʱ�Ƿ�����EL3������Ϊ1���κ�WFE������������EL3,�����bit������

4.3?SP_EL0��SP_EL3�Ĵ���

????Armv8����SP_EL0��SP_ELx����ջָ��Ĵ���,����SP_ELx����SP_EL1 �C SP_EL3����bank�Ĵ�����SP_ELx�Ĵ���Ϊ�쳣ջָ��Ĵ���,��cpu�����쳣���е�������쳣��ӦEL��SP_ELx�Ĵ���,������smc�쳣ʱջָ��Ĵ��������л���SP_ELx��SP_EL0���Ա��κ��쳣�ȼ�ʹ��,�����EL1 �C EL3�г����쳣����������,ִ������������ʱһ�㶼���л�ΪSP_EL0ջָ�롣

4.4?SPSR_EL3��ELR_EL3�Ĵ���

????ͨ���жϻ��쳣����EL3ʱ,�����쳣֮ǰ��PSTATE�Ĵ������ᱻ���浽SPSR_EL3�Ĵ�����,���쳣������ɺ�ͨ��ERETָ��ضϵ㴦����ִ��֮ǰ,���øüĴ�����ֵ�ָ�PSTATE��ֵ��ELR_EL3��SPSR_EL3����,ָʾ���쳣����֮ǰ�üĴ��������ڱ��淵�ص�ַ,�쳣������ɺ��÷��ص�ַ�ָ���PC�С�

5?������ת��ʽ

????ǰ�������ĵ�������תʱ������Ҫʹ�õ�ERET��SMCָ��,���������ٿ�����תʱ��ϸ��

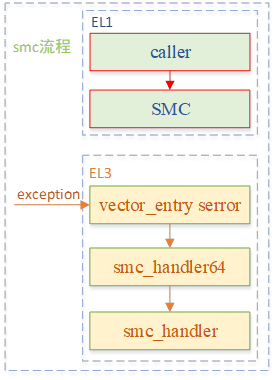

5.1?Smc�쳣��������

????smc��armv8֧�ֵ��쳣��תָ��,�����ڳ����EL1��EL2��ת��EL3�쳣�ȼ�������ת��������:

????��atf��BL1 smc��������Ϊ��,EL1������ͨ��smcָ�����뵽EL3�쳣,�˺�CPU����ת��EL3�쳣��������vector_entry SynchronousExceptionA64��ڴ�,�ú�������esr_el3�Ĵ������쳣ԭ��,����Ϊsmc�쳣,����ת��smc��������smc_handler64�С�smc_handler64����ͨ��x0 �C x7�Ĵ�������IJ�����ȡsmc��������,ִ���ض������������,��ͨ���Ĵ���x0 �C x4���ش�������������쳣��������ת���ѡ��ԭ��ɲο����²���:

Armv8�ж�·�ɻ���

5.2?ERET��ת����

????ERETָ�����ڴ��쳣���������з���,�ڽ����쳣��������֮ǰ,�����ȿ�һ��armv8�쳣��ת�����̡�Armv8�����쳣���жϺ�Ӳ������ִ�����²���:

(1)��PSTATE�Ĵ��������ݱ��浽SPSR_ELx��,����x��ʾ�쳣������쳣�ȼ�,��smc�쳣��������EL3,�����Ӧ�ļĴ�����ΪSPSR_EL3

(2)���쳣������ɺ���Ҫ���صĵ�ַ������ELR_ELx��

(3)�����жϺ��쳣����DAIF,�Թر������жϺ��쳣

(4)���쳣��ͬ���쳣��SError�ж�,�쳣״̬��Ϣ����������ESR_ELx��,����Ϣ�����ڷ����쳣������ԭ��

(5)���쳣Ϊָ���쳣�������쳣���������,���쳣��Ӧ���ڴ��ַ�������浽FAR_ELx�Ĵ�����

(6)ջָ���л�ΪĿ���쳣�ȼ���ջָ��Ĵ���SP_ELx

(7)������ת����Ӧ���쳣�������,ִ���쳣��������

????���쳣ִ����ɺ�,��ͨ��ERETָ��ر��쳣�жϳ���Ķϵ㴦����ִ��,��ָ�ʹӲ��ִ�����²���:

(1)��SPSR_ELx�Ĵ��������ݻָ�PSTATE�Ĵ���

(2)��ELR_ELx�Ĵ��������ݻָ�PCֵ

????���������̿��Կ���,ִ��ERETָ�������ִ��������SPSR_ELx��ELR_ELx���������,������ִ�о���֮�����ת,ֻҪ��ERET֮ǰ��ELR_ELx����Ϊ����ת�������ڵ�ַ,��������ȷ��SPSR_ELx�������

6?�ڴ�滮

6.1?�ڴ�滮ԭ��

????Ƕ��ʽϵͳ���ڴ�һ�����ROM��SRAM��DDR,����ROM��SRAMλ��SOCƬ��,DDRλ��оƬ�ⲿ�����ǵ��ص�����:

(1)ROM�е����ݶϵ����ʧ,���������ڴ���ִ��,���������ھ���洢,����ֻ��ֻ��Ȩ��

(2)SRAM��DDR�е������ڶϵ����ʧ,���ֻ�ܱ����ڴ���Ķ�ִ̬��,���������ھ���洢

(3)ROM��SRAM����ֱ������������,ϵͳ�ϵ��ֱ��ִ�С���DDR��Ҫͨ��DDR phy��DDR controller���ӵ�������,���ʹ��֮ǰ����Ҫ�ȶ���ִ�г�ʼ������

????�������������ڴ���ص��ǰ�澵������������̵�����,���ڴ�滮��������Ҫ�������¼�������:

(1)����BL1��Ҫ�̻���ROM��,����ϵͳ����ִ�е�,���ROM��ַ��Ҫ��ӳ�䵽cpu��������ַ��

(2)����ROM��ֻ����,BL1������˴���κ�ֻ�����ݶ�֮������ɶ�д���ݶ�,�ⲿ��������BL1����ʱ��Ҫ��ROM�ض�λ��SRAM��

(3)����BL1���̻���ROM��,оƬ������Ͳ��ܸ���,���DDR��ʼ�����벻�ܼ��ɵ�BL1�С���BL2��Ҫ�����ص�SRAM��ִ��,����BL2��ִ��DDR��ʼ������

(4)BL2֮�����������ȿ���������SRAM��,Ҳ����������DDR��

(5)��ǰ��ľ����������̿�֪,��BL2������secure EL1��,����ִ����ɺ�,��Ҫͨ��smc�ٴ�����BL1ȥִ��BL31����,���BL2��BL1�ĵ�ַ�������ص�

(6)BL31����ִ������������,��ϵͳ���й����л�����secure monitor�ķ�ʽפ��,Ϊnormal�ռ��smc�쳣�ṩ��������,�Լ�Ϊnormal os��trust os֮���ṩ��Ϣת�����ж�·��ת���ȹ��ܡ����,BL31������Ҫ����פ���ڴ�,��ϵͳ������ɺ��ܱ�����

(7)��BL31����,BL32����������Ҫפ���ڴ�Ϊϵͳ�ṩ��ȫ��ط���,���Ϊ����������ڴ�Ҳ���ܱ�����

(8)����֮��,BL1��BL2��BL33(һ��Ϊuboot)���ڴ���ϵͳ������ɺ��Ա��ͷŸ�����ϵͳʹ��

6.2?qemu virtƽ̨�ڴ�滮ʾ��

���������ڴ�滮ԭ��,qemu virt machine�������ε��ڴ�滮����:

| ���� | ��ʼ��ַ | ������ַ | ���� | �Ƿ�secure�ڴ� | ���� |

|---|---|---|---|---|---|

| ROM | 0x00000000 | 0x00020000 | 128k | Yes | BL1(bootrom) |

| SRAM | 0x0e04e000 | 0x0e060000 | 72k | Yes | Bl1(rwdata) |

| SRAM | 0x0e000000 | 0x0e001000 | 4k | Yes | Sharedram |

| SRAM | 0x0e01b000 | 0x0e040000 | 148k | Yes | BL2 |

| SRAM | 0x0e040000 | 0x0e060000 | 128k | Yes | BL31 |

| SRAM | 0x0e001000 | 0x0e040000 | 252k | YES | BL32 |

| DDR | 0x60000000 | 0x100000000 | 2.5G | NO | BL33 |