Cortex-M3��Cortex-M4

1. ���������롢������������

һ����˵,������ʹ��ǰ��Ҫ��ʼ��,һ��������¼���:

- �����Ҫ,����ʱ�ӿ��ƻ�·ʹ�����ӵ�����Ͷ�Ӧ���ŵ�ʱ�ӡ������ִ�������������ʱ���źŷֲ��ľ�ϸ����,��ʹ��/��ֹ��ÿ�������ʱ�������Խ�ʡ���ġ�����ʱ��һ����Ĭ�Ϲرյ�,��Ҫ�ڱ������ǰʹ��ʱ�ӡ���Щ�����,���ܻ���Ҫʹ����������ϵͳ��ʱ�ӡ�

- ��Щ�����,���ܻ���Ҫ����I/O���ŵIJ���ģʽ����������������и��õ�I/O����,�����ڶ���Ŀ�ġ�Ϊ��ʹ������,����

I/O������ƥ����;�Ǻ��б�Ҫ��(������/��������ܵ�)������,���ܻ���Ҫ������������üĴ���,����������͵�Ԥ��ĵ�������(��ѹ������/�����Ϳ�©��)�� - �������á����������а�������ɱ�̼Ĵ���,������Ҫ��ʹ��ǰ�������á���Щ�����,�ᷢ���������̱�8λ������Ҫ������һЩ,������Ϊ32λ������������һ��Ҫ��8λ/16λϵͳ������Ҫ���ӵöࡣ����,��������Ӧ��һ����ṩ�豸���������,����ʹ����Щ���������Խ�������ı�̹�������

- �ж����á���������Ҫʹ���жϲ���,����Ҫ���

Cortex-M3/M4���������жϿ�����(NVIC),ʹ���жϺ������ж����ȼ���

��������Ӧ����Ҫ������IJ������ӵ��洢��ϵͳ��;

- ����洢��,һ����Flash��

- ���ݴ洢��,һ����SRAM��

- ����

2. Cortex-M3��Cortex-M4 OS֧�ֺ�ϵͳ������

Cortex M3��Cortex-M4�����������ʱ�Ϳ����˶�Ƕ��ʽOS�ĸ�Ч֧�֡����Ǿ���һ�����õ�ϵͳ���Ķ�ʱ��SysTick,����ΪOS��ʱ�ṩ�����Զ�ʱ�жϡ�����SysTick��ʱ�������е�Cortex-M3��Cortex-M4�豸�ж�����,Ƕ��ʽOS��Դ������Ժ����ؾ����������е���Щ�豸��,������Ϊ�豸��صĶ�ʱ�������ġ�

Cortex-M3��Cortex-M4��������ջָ��: OS�ں˺��ж��õ���ջָ��(MSP)�Լ�Ӧ�������õĽ���ջָ��(PSP)������,OS�ں��õ�ջ�ͺ�Ӧ�������ջ���뿪����,�ɿ��Եõ���ߵ�ͬʱ,ջ�ռ��ʹ��Ҳ�õ����Ż���û��OS�ļ�Ӧ�ÿ���ֻʹ��MSP��

Ϊ�˽�һ����߿ɿ���,Cortex-M3��Cortex-M4֧�ֶ�������Ȩ�ͷ���Ȩ����ģʽ,��������������Ĭ�ϴ�����Ȩģʽ����ʹ��OS��ִ���û�����ʱ,�û���������ڷ���Ȩ����ģʽ��ִ��,����������ǿijЩ����,����ֹ��һЩNVIC�Ĵ����ķ��ʡ���Ȩ�ͷ���Ȩ����ģʽҲ����ͬMPUһ��,��ֹ����Ȩ�������ijЩ�洢����������,�û���������ƻ�OS�ں��Լ��������������,���,Ҳ�������ϵͳ���ȶ��ԡ�

3. �Ĵ���

3.1 R13,ջָ��(SP)

R13Ϊջָ��,��ͨ��PUSH��POP����ʵ��ջ�洢�ķ��ʡ������ϴ�������ջָ��:��ջָ��(MSP,��ЩARM����Ҳ����ΪSP_main)ΪĬ�ϵ�ջָ��,�ڸ�λ����������ڴ���ģʽʱ,��ᱻ������ѡ��ʹ�á�����һ��ջָ����Ϊ����ջָ��(PSP,��ЩARM����Ҳ����ΪSP_process),��ֻ�������߳�ģʽ��ջָ���ѡ��������Ĵ���CONTROL������

MSP��PSP����32λ��,����ջָ��(MSP��PSP)�������λ����Ϊ0,������λ��д�����������á�����ARMCortex-M������,PUSH��POP����32λ��,ջ�����ĵ�ַҲ������뵽32λ���ֱ߽��ϡ�

��������,��Ӧ�ò���ҪǶ��ʽOS,PSPҲû��Ҫʹ�á������Ӧ�ÿ�����ȫ������MSP,һ�����õ�Ƕ��ʽOSʱ�Ż�ʹ��PSP ,��ʱOS�ں�ͬӦ�������ջ��������ġ�PSP�ij�ʼֵδ����,��MSP�ij�ʼֵ����Ҫ�ڸ�λ�����дӴ洢���ĵ�һ������ȡ����

ͬ�������еĴ������ܹ�һ��,Cortex-M������������ʱ��Ҫջ�洢��ջָ��(R13)����ջ���ִ洢��ʹ�û�����,�洢����һ-���ֿɱ���������ȳ������ݴ洢���塣ARM��������ϵͳ���洢������ջ�ռ����,��ʹ��PUSHָ����ջ�д洢�����Լ�POPָ���ջ����ȡ���ݡ�ÿ��PUSH��POP������,��ǰʹ�õ�ջָ�붼���Զ�������

ջ������:

- ������ִ�еĺ�����Ҫʹ�üĴ���(�Ĵ�������)�������ݴ���ʱ,��ʱ�洢���ݵij�ʼֵ����Щ�����ں�������ʱ���Ա��ָ�����,������ú����ij���ʧ����

- ���������ӳ����е���Ϣ���ݡ�

- ���ڴ洢�ֲ�������

- ���жϵ��쳣����ʱ���洦����״̬�ͼĴ�����ֵ��

3.2 R14,���ӼĴ���(LR)

R14Ҳ���������ӼĴ���(LR),���ں������ӳ������ʱ���ص�ַ�ı��档�ں������ӳ������ʱ,������ƿ���ͨ����LR����ֵ���س��������(PC)�з��ص��ó�������ִ�С���ִ���˺������ӳ�����ú�,LR����ֵ���Զ����¡���ij������Ҫ��������һ���������ӳ���,������Ҫ���Ƚ�LR����ֵ������ջ��,����,��ִ���˺������ú�,LR�ĵ�ǰֵ��Gʧ��

���쳣�����ڼ�,LRҲ�ᱻ�Զ�����Ϊ�����EXC_RETURN(�쳣����)��ֵ,֮�����ֵ�����쳣��������ʱ�����쳣���ء�

3.3 R15,���������(PC)

R15Ϊ���������(PC),�ǿɶ���д��,���������ص�ǰָ���ַ��4(������Ƶ���ˮ�����Լ�ͬARM7TDMI���������ݵ���Ҫ)��дPC(����,ʹ�����ݴ���/����ָ��)��������ת������

����ָ�����Ҫ���뵽���ֻ��ֵ�ַ,PC�����λ(LSB)Ϊ0������,��ʹ��һ-Щ��ת/���洢��ָ�����PCʱ,��Ҫ����PCֵ��LSB��1�Ա�ʾThumb״̬,����ͻ�������ͼʹ�ò�֧�ֵ�ARMָ��(��ARM7TDMI�е�32λARMָ��)�����������쳣�����ڸ��������(����C��C++),���������Զ�����תĿ���LSB��λ��

���������,��ת�͵�����ר�ŵ�ָ��ʵ��,�������ݴ���ָ�����PC�������Ϊ�ټ�������,�ڷ���λ�ڳ���洢���е��ַ�����ʱ,PC����ֵ�dz�����,���,�ᾭ�����ִ洢����������PC��Ϊ����ַ�Ĵ���,����ַƫ������ָ���е����������ɡ�

CONTROL�Ĵ���������:

- ջָ���ѡ��(��ջָ��/����ջָ��)��

- �߳�ģʽ�ķ��ʵȼ�(��Ȩ/����Ȩ)��

����,���ھ��и��㵥Ԫ��Cortex-M4������,CONTROL�Ĵ�������һλ��ʾ��ǰ������(����ִ�еĴ���)�Ƿ�ʹ�ø��㵥Ԫ��

4. Cʵ�ֵ��쳣����

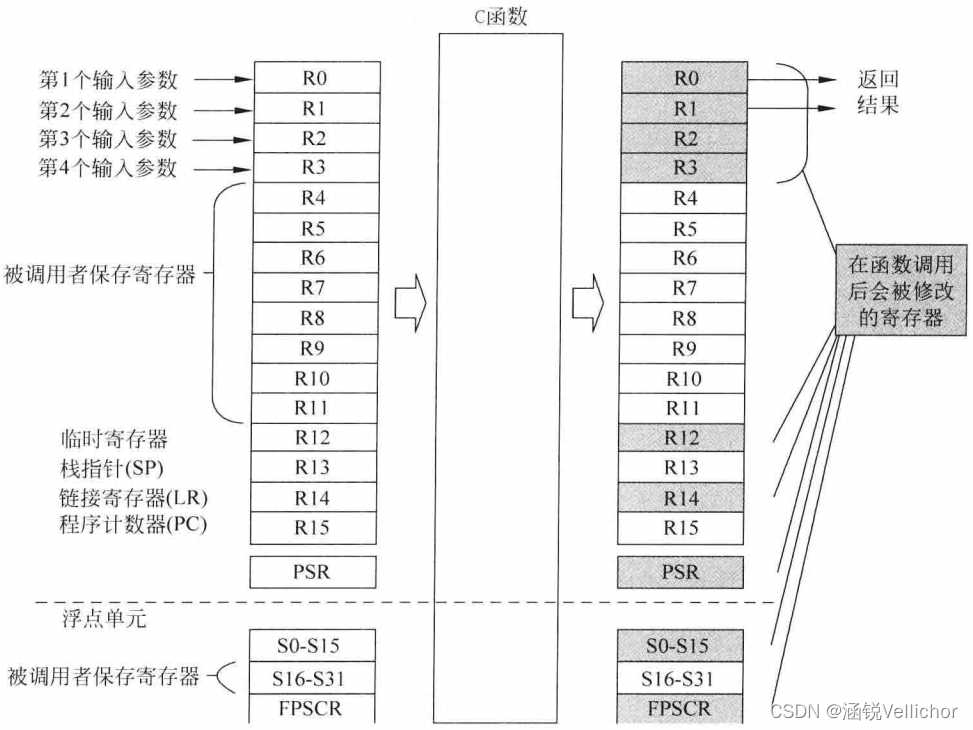

����ARM�ܹ���C��������ѭARM��һ����ΪAAPCS(ARM�ܹ����̵��ñ�)�Ĺ淶��������ݱ�,C����������R0~ R3��R12��R14(LR)�Լ�PSR����C������Ҫʹ��R4~R11,��Ӧ�ý���Щ�Ĵ������浽ջ�ռ���,�����ں�������ǰ�����ǻָ�,����ͼ��ʾ��

R0~R3��R12��LR�Լ�PSR�������������߱���Ĵ�����,���ں������ú���Ҫʹ����Щ�Ĵ�������ֵ,�ڽ��е���ǰ,�����ӳ���ij��������Ҫ����Щ�Ĵ��������ݱ��浽�ڴ���(��ջ)���������ú���Ҫʹ�õļĴ�����ֵ���ñ��档

R4~R11Ϊ���������߱���Ĵ�����,�����õ��ӳ��������Ҫȷ����Щ�Ĵ����ں�������ʱ���ᷢ���仯(����뺯��ʱ����ֵһ-��)����Щ�Ĵ�������ֵ���ܻ��ں���ִ�й����б仯,������Ҫ�ں����˳�ǰ�����ǻָ�Ϊ��ʼֵ��

һ����˵,�������ý�R0~R3��Ϊ�������,R0���������ؽ����������ֵΪ64λ,��R1Ҳ�����ڷ��ؽ������ͼ��

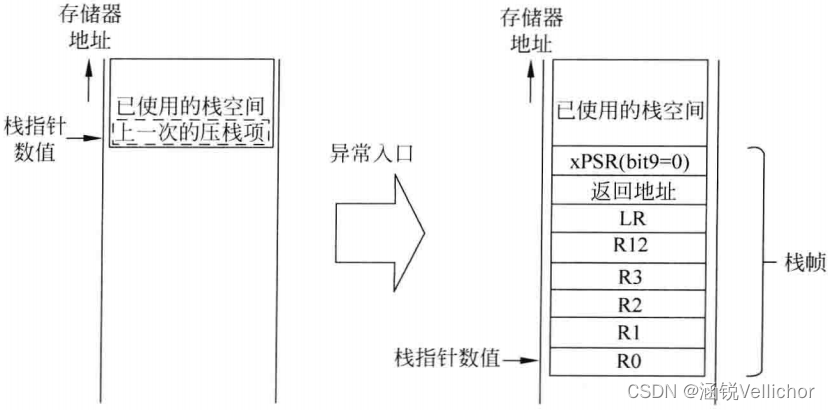

ҪʹC�������������쳣����,�쳣������Ҫ���쳣��ڴ��Զ�����R0~R3��R12��LR�Լ�PSR,�����쳣�˳�ʱ�����ǻָ�,��Щ��Ҫ�ɴ�����Ӳ�����ơ�����,�����ص����жϵij���ʱ,���ԼĴ�������ֵ����ͽ����ж�ʱ��ͬ������,����ͨ��C�������ò�ͬ,���ص�ַ(PC)����ֵ��û�д洢��LR��(�쳣�����ڽ����쳣ʱ��EXC_RETURN���������LR��,����ֵ�������쳣����ʱ�õ�),���,�쳣����Ҳ��Ҫ�����ص�ַ���档��������Contex-M3���и��㵥Ԫ��Contex-M4������,��Ҫ���쳣�����ڼ䱣��ļĴ�������8����

���쳣����ʱ,Ӳ�����Զ���һ���ּĴ���ѹ��ջ�б���,����ͼ��ʾ��

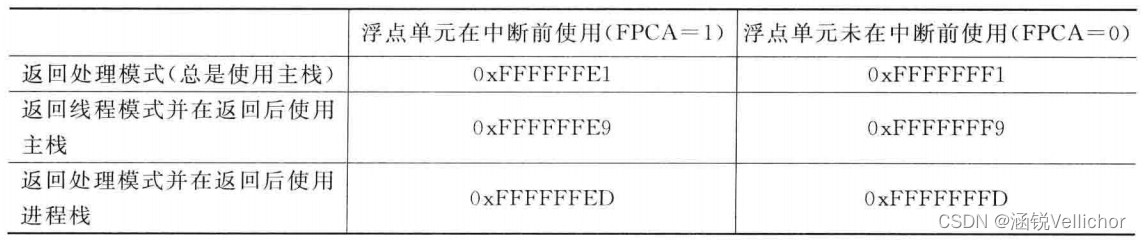

5. EXXC_RETURN

�쳣��������˵����Ҳ��C����,������ͨ������ʲô������?

�������������,��������ͨ����ʱ,LR�Ĵ����ᱣ������һ������ʱ�ĵ�ַ,���ں��淵���á��������쳣��������ǰ,Ӳ�����Զ���һ���ּĴ���ѹ��ջ�б���,�쳣����������LR�ᱻ����Ϊһ������ֵ,���쳣������������ʱ,����LR��һ������ֵ�Ļ�,�ͻᴥ��Ӳ���ָ�֮ǰӲ���Զ����������ļĴ�����

�����������쳣�������жϷ������(ISR)ʱ,���ӼĴ���(LR)����ֵ�ᱻ����ΪEXC_RETURN��ֵ��������BX��POP��洢������ָ��(LDR��LDM)�����ص�����Ĵ�����ʱ,����ֵ���ڴ����쳣���ػ��ơ�

6. Ӱ��ջָ��

Cortex-M�������д�������ջָ��:

- ��ջָ��

(MSP)ΪĬ�ϵ�ջָ�롣��CONTROL��bit[1](SPSEL)Ϊ0ʱ�����߳�ģʽ,�ڴ���ģʽ��������ʹ�á� - ����ջָ��

(PSP),��CONTROL��bit[1](SPSEL)Ϊ1ʱ�����߳�ģʽ��

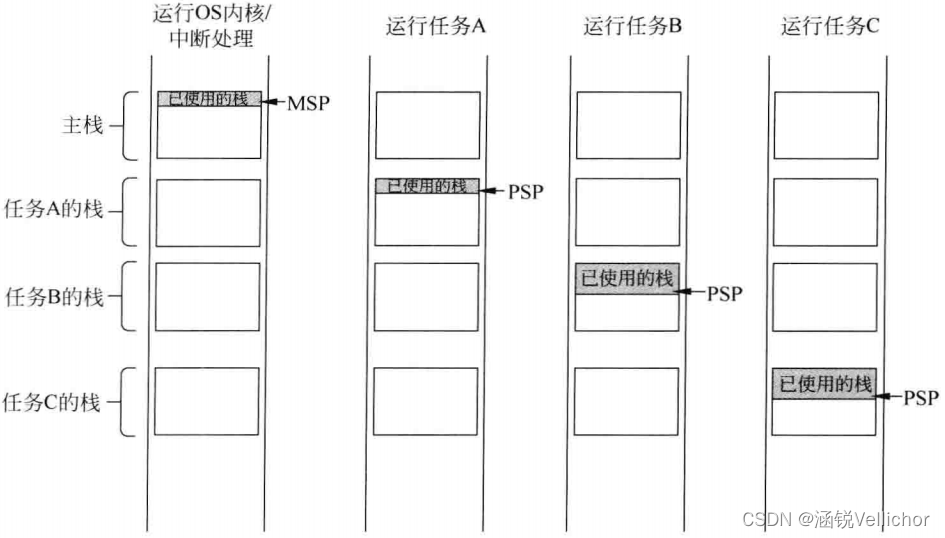

PUSH��POPָ��ʵ�ֵ�ջ������ʹ��SP(R13)�Ķ���ָ���ʹ�õ�ǰѡ���ջָ��,����������MRS��MSRָ��ֱ�ӷ���MSP��PSP�����ڲ�����Ƕ��ʽOS��RTOS�ļ�Ӧ��,���������в�����ֻʹ��MSP,�����ù�PSP��

���ھ���Ƕ��ʽOS��RTOS��ϵͳ,�쳣����(��������OS�ں�)ʹ��MSP,��Ӧ��������ʹ��PSP��ÿ��Ӧ���������Լ���ջ�ռ䡣OS�е��������л�������ÿ���������л�ʱ�������PSP��

��������м����ŵ�:

- ��Ӧ�����������ᵼ��ջ�ƻ�������,OS�ں�ʹ�õ�ջ�����������ջ�����ܵ�Ӱ��,��˿������ϵͳ�Ŀɿ��ԡ�

- ÿ�������ջ�ռ�ֻ������ջ������������һ��ջ֡(����Cortex-M3�����㵥Ԫ��Cortex-M4,���9����,����������˵���,���߶��ھ��и��㵥Ԫ��Cortex-M4�����Ϊ27����),����ISR��Ƕ���жϴ�����ջ�ռ�ᱻ��������ջ�С�

- �����ڴ���

Cortex-M�������õĸ�ЧOS�� - OS���������ô洢��������Ԫ(MPU)������Է���ij��ջ�����Ӧ��������ijӦ���������ջ���������,MPU���Դ���һ��

MemManage�����쳣,���ұ��������ջ�ռ�����Ĵ洢�������ǡ��ϵ��,MSP ����ʼ��Ϊ�������е���ֵ,��Ҳ�Ǵ�������λ���̵�һ���֡����������ӵ�C��������Ҳ����ִ�ж���ջ���г�ʼ��������������֮��������MSRָ���ʼ��PSP,����д��CONTROL����SPSEL,����һ�㲻����ô����

7. SVC�쳣

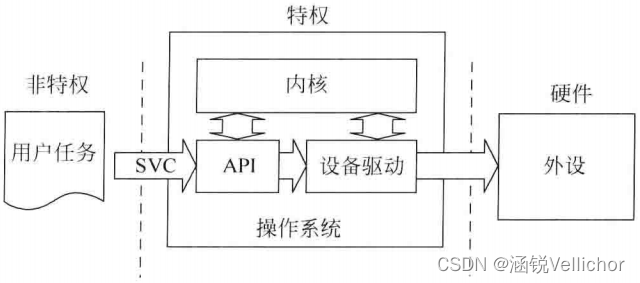

������Ҫ�߿ɿ��Ե�ϵͳ,Ӧ��������������ڷ���Ȩ���ʵȼ�,������ЩӲ����Դ�ɱ�����Ϊֻ֧����Ȩ����(����MPU),Ӧ������ֻ��ͨ��OS�ķ��������Щ�ܱ�����Ӳ����Դ���������ַ�ʽ,����Ӧ����������ùؼ�Ӳ���ķ���Ȩ��,Ƕ��ʽϵͳ����ӽ�׳�Ͱ�ȫ��

����C��̻���,��Ҫ��SVC������Ϊ��������:

- ��һ������ȡջ֡����ʼ��ַ,��������Ϊ����������ݸ��ڶ����֡��ô���Ҫ�û��ʵ��,������Ϊ��Ҫ���LR����ֵ(EXC_RETURN),��������Cʵ�֡�

- �ڶ����ִ�ջ֡����ȡѹջ��PC��ֵ,Ȼ��ӳ�������еõ�SVC��š���������ѡ����ȡ��ѹջ�ļĴ�����ֵ��������Ϣ��

8. PendSV�쳣

PendSV(�ɹ����ϵͳ����)�쳣��OS����Ҳ�dz���Ҫ,���쳣���Ϊ14�Ҿ��пɱ�̵����ȼ�������д���жϿ��ƺ�״̬�Ĵ���(ICSR)���ù���λ�Դ���PendSV�쳣����SVC�쳣��ͬ,���Dz���ȷ�ġ����,���Ĺ���״̬���ڸ������ȼ��쳣����������,�һ��ڸ����ȼ�������ɺ�ִ�С�

���ø�����,����PendSV����Ϊ��͵��쳣���ȼ�,������PendSV�쳣���������������жϴ���������ɺ�ִ�С�������������л��dz�����,Ҳ�Ǹ���OS����еĹؼ���

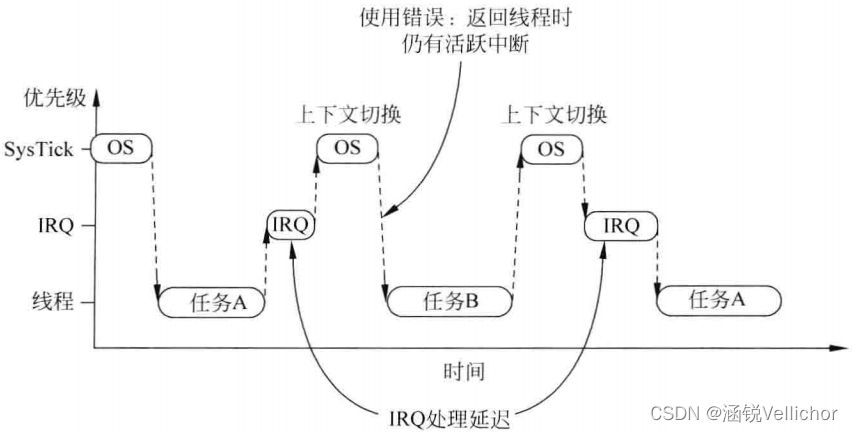

��OS������,������������Ծ����Ƿ�Ӧ��ִ��,�������л����ٶ�OS�ں˵�ִ����SysTick �쳣����,ÿ������������л���һ����ͬ������

���ж�����(IRQ)��SysTick�쳣ǰ����,��SysTick�쳣���ܻ���ռIRQ�����������������,OS��Ӧִ���������л�������,IRQ�����ͻᱻ�ӳ�,����ͼ��ʾ������Cortex-M3��Cortex-M4������,�����ڻ�Ծ���쳣����ʱ,���Ĭ�ϲ��������ص��߳�ģʽ�������ڻ�Ծ�жϷ���,��OS��ͼ���ص��߳�ģʽ,��ʹ�ô����쳣�ᱻ������

��һЩOS�����,Ҫ����������,�����������жϷ���ʱ��ִ���������л�,��ʱ���Լ��ջ֡�е�ѹջxPSR��NVIC�е��жϻ�Ծ״̬�Ĵ���������,ϵͳ�����ܿ��ܻ��ܵ�Ӱ��,�ر��ǵ��ж�Դ��SysTick�ж�ǰ�������������ʱ,�����������л����ܾ�û��ִ�еĻ����ˡ�

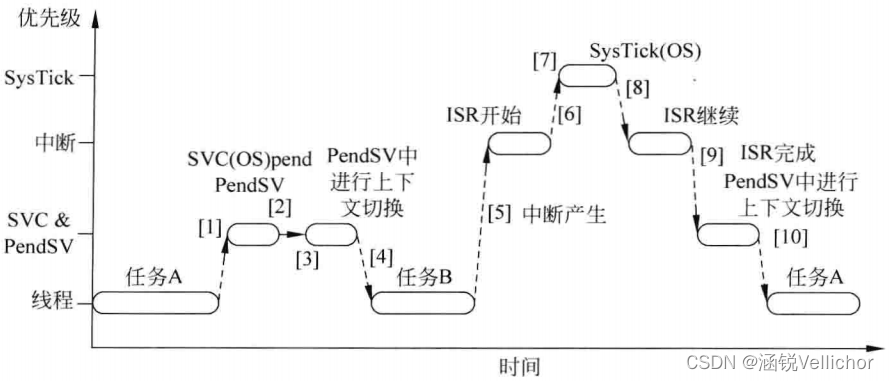

Ϊ�˽���������,PendSV�쳣���������л������ӳٵ���������IRQ�������Ѿ���ɺ�,��ʱ��Ҫ��PendSV����Ϊ������ȼ�����OS��Ҫִ���������л�,��������PendSV�Ĺ���״̬,����PendSV�쳣��ִ���������л�����ͼ��ʾΪ����PendSV�����������л���һ��ʵ��,�����������¼�����:

- A�������SVC���������л�(����,�ȴ�һЩ�������)��

- OS�յ�����,�������������л�,�ҹ���

PendSV�쳣�� - ��CPU�˳�SVCʱ,����������

PendSV�ҽ����������л��� - ��

PendSV��ɲ������̵߳ȼ�ʱ,OS��ִ��B���� - �жϲ����ҽ����жϴ�����

- �������жϴ�������ʱ,

SysTick�쳣(����OS����)������� - OSִ����Ҫ����,Ȼ�����

PendSV�쳣���������������л��� - ��

SysTick�쳣�˳�ʱ,�᷵�ص��жϷ������ - ���жϷ�����������,

PendSV��ʼִ��ʵ�ʵ��������л������� - ��

PendSV��ɺ�,���ص��̵߳ȼ�,�������ص�����A������ִ�С�

����OS�����е��������л�,PendSV�������ڲ�����OS�Ļ����С�����,�жϷ�����������ҪһЩ����ʱ��,Ҫ�����IJ��ֿ��ܻ���Ҫ�����ȼ�,������������ISR�����ڸ����ȼ���ִ�е�,�������жϷ�������ںܳ�ʱ���ڶ���ִ�С������������,���Խ���.�Ϸ���������Ϊ��������:

- ��һ���ֶ�ʱ��Ҫ��Ƚϸ�,��Ҫ����ִ��,�����ȼ��ϸߡ���λ����ͨ��ISR��,��ISR����ʱ,����

PendSV�Ĺ���״̬�� - �ڶ����ְ����жϷ��������ʣ��Ĵ�������,��λ��

PendSV�������Ҿ��нϵ͵��쳣���ȼ���

![[����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-NzACoVBT-1652249640119)(C:\Users\���\AppData\Roaming\Typora\typora-user-images\image-20220511134226109.png)]](https://img-blog.csdnimg.cn/9f4c395c5648480383cc0b07809427f7.png)