7.1环境

这一章节描述了系统级的中断环境以及中断控制器功能。PS端是基于ARM架构的,并且使用了两个Cortex-A9处理器以及型号为pl390的GIC中断控制器。整个中断结构与处理器、可编程逻辑器件(PL)、从外部IO接受到的中断请求有非常紧密的联系。本章节包含了下面这些关键点:

1 私有、共享以及软件中断

2 GIC功能

3 中断优先级和中断处理

7.1.1 私有、共享以及软件中断

每个CPU拥有一组使用banked寄存器(R8~R14) 且拥有私有访问权限的 私有外部中断(PPI)。PPI的来源包含了本地timer,私有看门狗timer,私有timer,以及来自于PL的FIQ/IRQ。软件生成中断(SGIs)被发送到1个或者两个CPU,SGIs通过写通用中断控制器(GIC)的寄存器来产生,详情查看7.3章节-寄存器概述。共享外部中断(SPIs)通过PS/PL端的I/O和内存控制器来产生。SPIs只会被发送到两个CPU中的一个。来自PS端外设的SPI中断也会被发送到PL端。

7.1.2 通用中断控制器(GIC)

GIC是一个集中式的中断管理块,用来管理发送到CPU的中断。GIC以编程的方式来进行以下操作:使能、失能、屏蔽、对中断资源的优先级排序、确定中断发送到哪一个CPU。此外,GIC对于有安全需求系统的操作是支持安全扩展的。

控制器的版本为 Generic Interrupt Controller Architecture version 1.0 (GIC v1),非矢量型。

寄存器通过CPU私有总线访问,私有总线的高速读写响应是内部通过避免暂时阻塞以及其他瓶颈来实现。

在将一个最高优先级的中断发送到独立的各个CPU之前,GIC会集中所有的中断资源。GIC确保一个指定发送到多个CPU的中断同一时间只被一个CPU捕获。每一个中断源都拥有一个独特的中断号。每一个中断源都有可配置的优先级和目标CPU列表(一个中断可能被发送到多个CPU,那么此时就需要一个表来存储需要被发送到的CPU号)。

7.1.3 重置以及时钟

中断控制器通过 reset子系统 来进行重置。具体操作为写A9_CPU_RST_CTRL寄存器的PERI_RST位。同样的重置信号也会重置CPU私有timers以及私有看门狗timers(AWDT)。reset之后,所有的中断包括挂起的或者需要处理的,都将被忽略。

7.1.4 时钟示意图

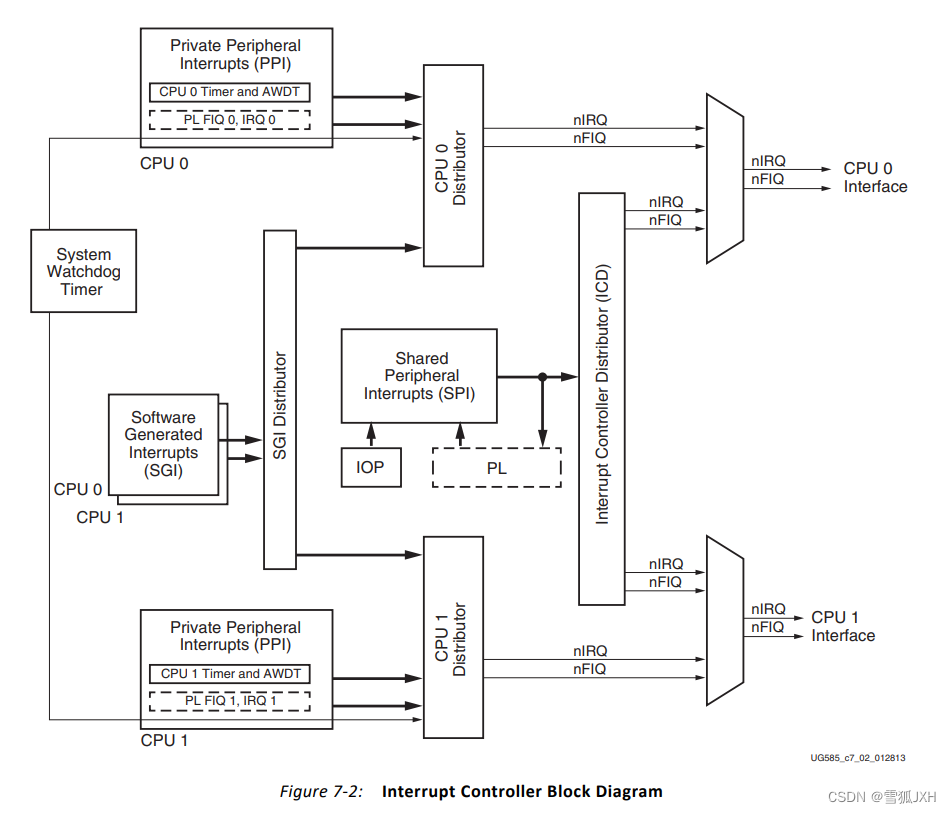

共享外部中断由多个子系统产生,这些子系统包括 PS端的I/O外设以及PL端的逻辑。中断源如图7-2所示。

7.1.5 CPU中断信号传递

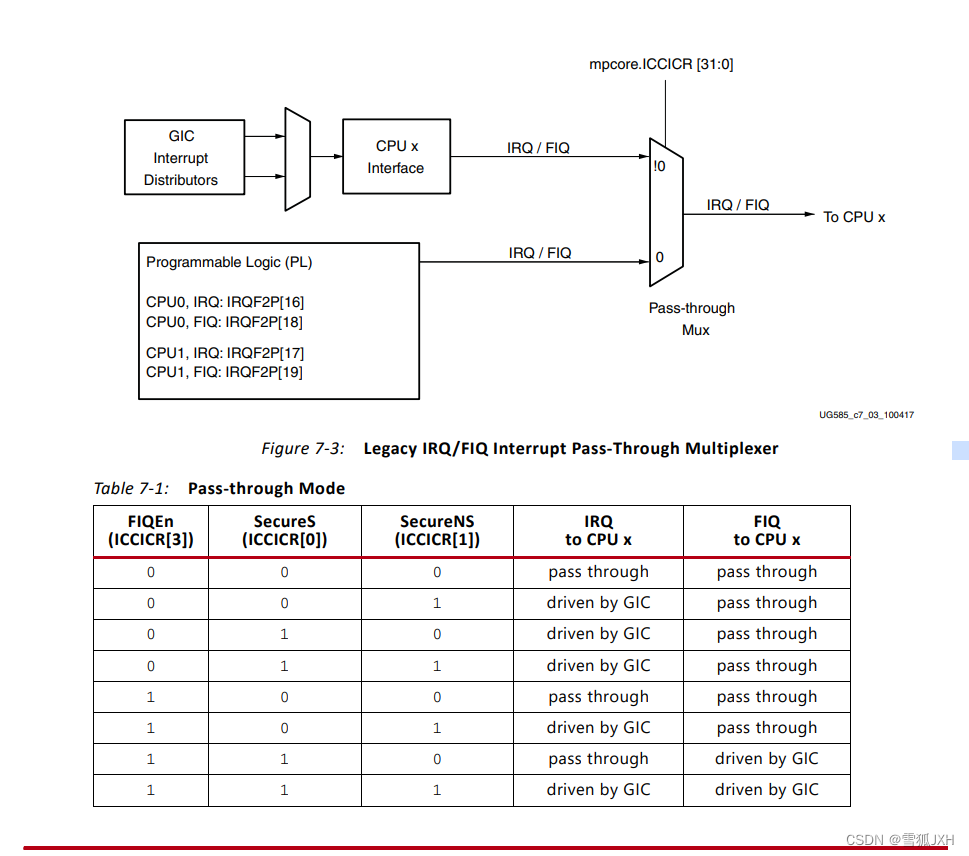

来自于PL的IRQ/FIQ中断可以通过GIC作为PPI中断发送,或者绕过GIC,使用传递数据选择器。传递模式通过mpcore的ICCICR寄存器使能,如表7-1所示。

7.2 功能描述

7.2.1软件中断(SGI)

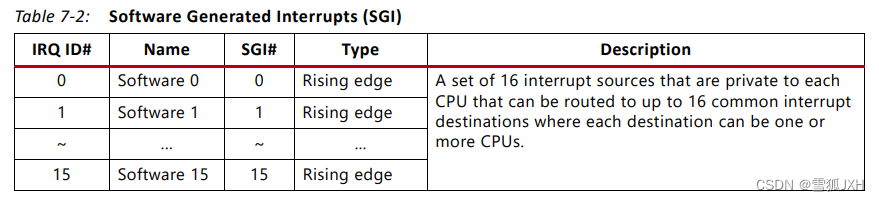

使用软件中断,每个CPU可以中断自己、中断其他的CPU、或者中断多个CPU。一共有16个软件中断(Table 7-2)。一个SGI中断通过写入中断号到ICDSGIR寄存器来产生中断以及指定目标CPU,这样的写入操作通过CPU的私有总线进行。每个CPU拥有它自己的SGI寄存器组来产生一个或多达16个软件中断。通过写入ICCIAR寄存器的 corresponding 位为1 或 读取ICCIAR寄存器来清除中断。

所有的SGI中断是边沿触发的。SGI中断的触发类型是固定的且不可更改;ICDICFR0寄存器是只读寄存器,它指定了所有的16个SGI中断的触发类型。

7.2.2 CPU私有外部中断(PPI)

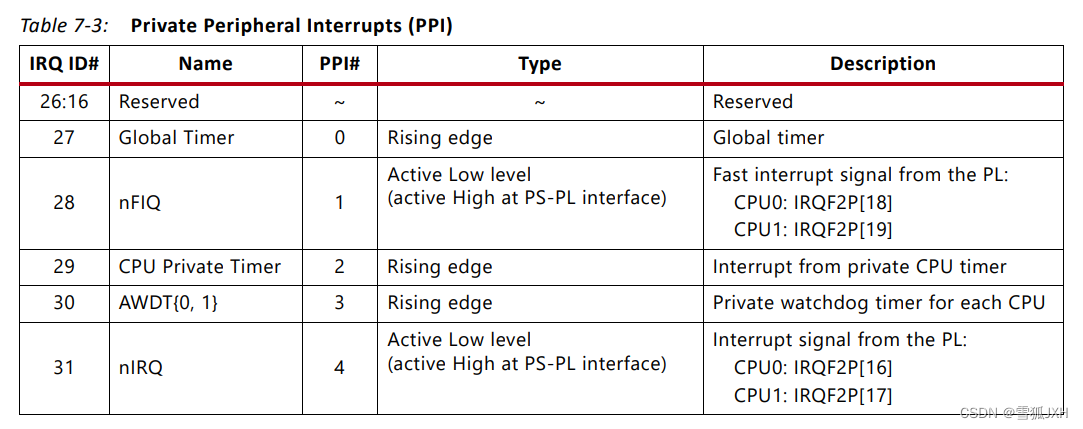

每个CPU连接到5个私有外部中断。PPI中断列在Table7-3中。

PPI中断的触发类型也是固定的且不可改变的;因此,ICDICFR1寄存器是只读的,它指定了这5个PPI中断的触发类型。注意:来自于PL端的FIQ中断和IRQ中断信号被反转然后发送到中断控制器,因此,即使ICDICFR1寄存器中指示他们为低电平活跃状态(也就是低电平会触发中断),他们在PS-PL的接口上仍然是高电平活跃状态。

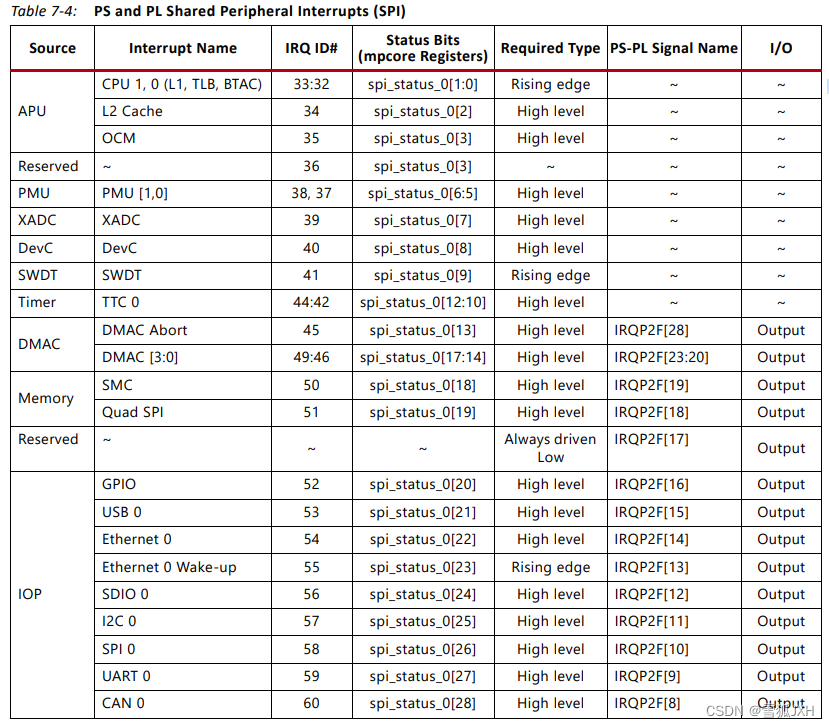

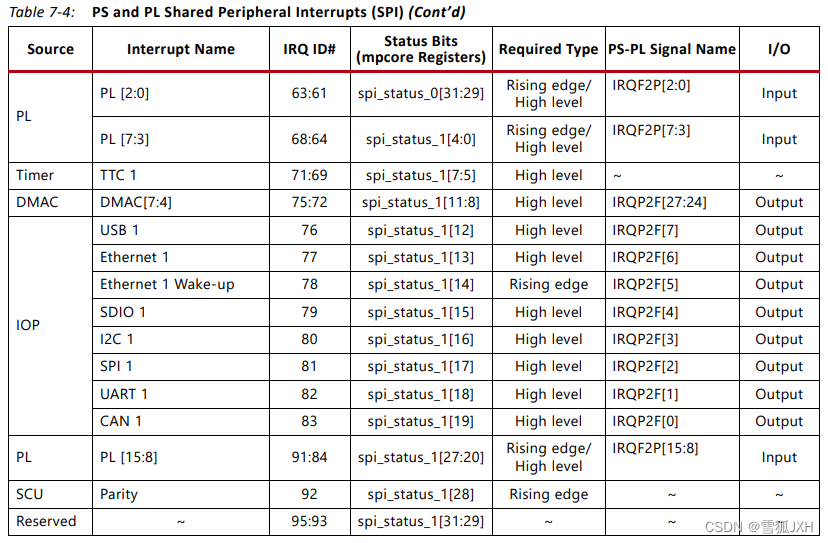

?7.2.3共享外部中断(SPI)

来自于各个模块的大约60个中断可以发送到1个或多个CPU或PL端。GIC控制器管理这些中断的优先级和接收者。

除了 61~68号以及84~91号中断,所有的中断触发类型都是由请求源固定的且不可改变的。GIC控制器需要通过编程来适应上面的特性。boot ROM(固化在芯片内部的一段起始代码)不会编程这些寄存器;因此SDK设备驱动(uboot/kernel)必须对GIC进行编程来适应这些触发类型。

对于一个电平触发方式的中断,在中断被收到之后,请求源必须提供一种中断操作方法来清除中断。这一要求应用到所有的使用高电平触发方式的IRQF2P[n]中断。

对于一个上升沿触发方式的中断,请求源必须提供一个足够被GIC控制器捕获的脉冲宽度。通常情况下这个脉宽至少需要两个 CPU_2x3x 周期。这一要求应用到所有的使用上升沿触发方式的IRQF2P[n]中断。

ICDICFR2寄存器通过ICDICFR5寄存器配置SPI中断的中断类型,每个中断占用2bit位域,用来指定触发方式以及处理方式。

SPI中断见Table 7-4。

?7.2.4中断触发、目标、处理

?7.2.4中断触发、目标、处理

?有三种进入GIC的中断:SPI,PPI,SGI(在以上章节已经介绍过)。一般情况下,中断信号包含一个触发设定,处理中断的CPU数量,中断的目标CPU。然而,大多数的中断信号的功能是固定的,其他的中断信号是部分可编程的。

有两组寄存器用来中断触发,处理,指定目标:

1 mpcore.ICDICFR[5:0]寄存器: 触发方式以及处理方式,见Figure 7-4。

2 mpcore.ICDIPTR[23:0]寄存器:指定CPU,见Figure7-5。

共享外部中断(SPI)

SPI中断可以被发送到任意数量的CPU,但却只会有一个CPU处理它。如果一个中断发送到两个CPU且这两个CPU同时回复GIC控制器,那么MPcore就会确保只有一个CPU会读到这个中断的ID号。而另外一个CPU则读到伪中断ID号--1023或者读到下一个挂起等待处理的中断的ID号,到底读到哪一个,这取决于时序。在中断服务执行时通过锁来移除一个请求。通过ICDIPTR[23:8]寄存器可以获取指定CPU的操作是否结束。每个SPI中断的触发方式必须通过编程来匹配表7-4所列出的内容。触发方式通过ICDICFR[5:2]寄存器位来编程。

私有外部中断(PPI)

每个CPU拥有自己独立的PPI中断。触发方式、处理方式、发送目标这些选项都是无法编程的,每个中断只会发送到它自己所属的CPU并且被处理。ICDICFR[1]寄存器是只读的且ICDIPTR[5:2]寄存器实际上是闲置的。

软件中断(SGI)

SGI中断总是边沿触发的并且只有当软件写中断号到ICDSGIR寄存器时中断才会产生。所有定义在ICDIPTR[23:8]寄存器位中的目标CPU必须处理掉中断来清除ICDSGIR寄存器。