简介

缓存一致性 关注的是 "同一个数据" 在 "高速缓存1"和"高速缓存2" ... 和"内存" 中的 一致性 问题

存在 不一致的 这种问题 ,该如何解决.有三种解决方案:

1. 关cache,不用cache

2. 硬件提供cache维护指令 ,软件调用指令维护缓存一致性

3. 硬件维护缓存一致性 ,软件不需要任何操作

arm 提供了cache ,自然不会建议 使用者关闭cache 来解决这些问题

arm 采用 2 和 3 来解决以下问题

arm mmu 话题 中的 “内存属性(Shareability & Cacheability)” 与 “muti core 和 multi cluster” 的 缓存一致性 强相关

P134

In the Armv8 memory model, the Shareability memory attribute indicates the degree to which hardware must ensure

memory coherency between a set of observers, see Memory types and attributes on page B2-143.

在Armv8内存模型中,可共享性内存属性表示硬件必须确保一组观察者之间的内存一致性的程度,请参阅第B2-143页的内存类型和属性。

The cacheability and shareability memory attributes

Cacheability and shareability are two attributes that describe the memory hierarchy in a multiprocessing system:

可缓存性和可共享性是描述多处理系统中内存层次结构的两个属性:

注意 : shareability 在多核中才有意义 , 在单核中设置为什么值效果都一样

Cacheability

This attribute defines whether memory locations are allowed to be allocated into a cache or not.

Cacheability is defined independently for Inner and Outer Cacheability locations.

该属性定义是否允许将内存位置分配到缓存中。

可缓存性是为内部和外部可缓存性位置独立定义的。

Shareability

This attribute defines whether memory locations are shareable between different agents in a system.

Marking a memory location as shareable for a particular domain requires hardware to ensure that

the location is coherent for all agents in that domain. Shareability is defined independently for Inner

and Outer Shareability domains.

此属性定义系统中不同代理之间是否可以共享内存位置。

将内存位置标记为特定域的可共享位置需要硬件来确保该位置对于该域中的所有代理都是一致的。

可共享性是为内部和外部可共享性域独立定义的。

For more information about Cacheability and Shareability, see Memory types and attributes on page B2-143.

共享性

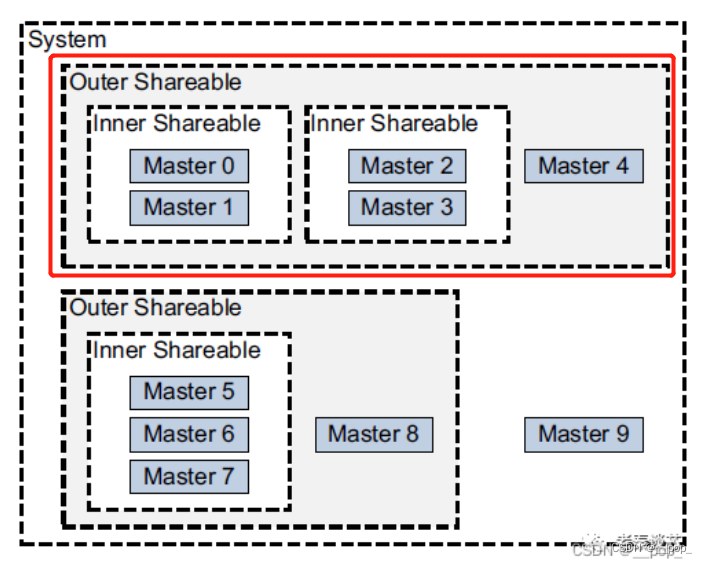

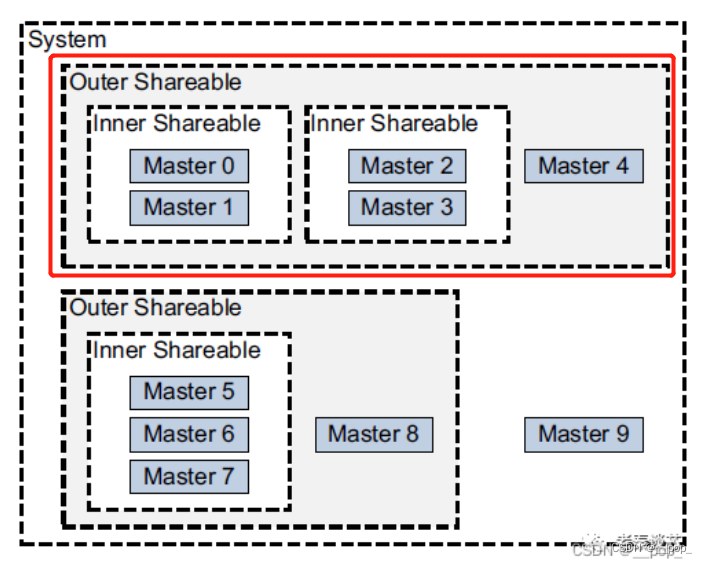

ARM引入了一个概念,共享域(shareability domains.)包含以下几种:

Inner shareable,意味着它适用于整个内部可共享域。

这表示该domain内的处理器之间可以相互share数据。

一个系统可以有多个inner shareable domains,并且当某个操作影响到其中一个inner shareable domain时,它并不会影响到其它的inner shareable domain。

Outer shareable,意味着它适用于内部可共享和外部可共享域。

一个outer shareable domain可以由一个或多个inner shareable domain组成,

并且当一个操作影响到outer shareable domain时,

也会影响到其下所有的inner shareable domain。

Non-shareable,表示相关区域只能给指定的处理器访问。

Full System,包含全部处理器。

system with 2 clusters:

cluster0 : cpu0(L1cache) cpu1(L1cache) L2cache

cluster1 : cpu2(L1cache) cpu3(L1cache) L2cache

L3cache

no-share

对于cpu0 来说 , no-share 为 cpu0的L1cache 和 cluster0的L2cache

inner share

对于 cpu0 来说, inner share 为 cpu0的L1cache 和 cluster0的L2cache 和 cpu1的L1cache

outer share

对于 cpu0 来说, outer share 为 cpu0的L1cache 和 cluster0的L2cache 和 cpu1的L1cache 和 cluster1 的所有cache 和 两个cluster共有的L3cache

Full System

等同于 outer share

问题

aarch64

1.

shareability domains 把 cache 分成了 多个域

但是我们用 "shareability" 来设置内存属性

一个是内存,一个是cache ,有什么关系呢?

mmu page table walk的时候 好像会根据 这个 内存属性 "shareability" 来 将其缓存到 对应的 cache域

shareability是cci读取并做解释的

应该和 arm 如何 实现 这些 域 有关系

2.

MMU translation table walk 时, 遇到 不同的 "shareability"的内存 就会缓存到对应的 "shareability domains",我在内核中找到 linux 只会用到 inner-share, 为什么?

linux是cacheable,inner的

因为smp共享的可缓存的,都会走l1l2再到l3,arm的cluster内部有一层cci,默认总线的事务不要出去,到下一个层级的

如果miss l3兜底.这个主要为了节省硬件的总线流量和功耗

3.

shareability 和 PoC/PoU 有什么关系

PoC/PoU 也是限定了范围,看起来和 "shareability domains" 限定的范围 相同,是不是可以 不同?

简而言之,PoU/PoC定义了指令和命令的所能抵达的缓存或内存,在到达了指定地点后,Inner/Outer Shareable定义了它们被广播的范围。

https:

4.

PoC/PoU 除了 可以用在 cache维护指令中 限定cache 范围,还可以做什么

没了

5. shareability 会在哪里被用到

1. 叶子页表中的值

2. 屏障指令中的参数

3. cache 维护指令的广播域

"muti core 和 multi cluster" 的缓存等级

可以控制 是否缓存

可以控制 缓存是否失效

可以控制 缓存 到哪一级别吗?

single core的 缓存一致性问题

DMA 和 高速缓存 一致性问题

问题描述

解决方案

自修改代码问题

问题描述

指令高速缓存和数据高速缓存不一致

数据高速缓存为新代码,指令高速缓存为老代码. 导致无法执行新代码

解决方案

2. 硬件提供指令,软件维护缓存一致性

软件调用高速缓存维护指令 : dc ic

修改页表

问题描述

tlb 保存的数据过时,导致索引到错的物理地址

解决方案

2. 硬件提供指令,软件维护缓存一致性

刷新tlb

multi core 新增问题

cpu0 和 cpu1 一致性问题

问题描述

cpu0 读 了内存地址A的值 , 缓存到 cpu0 的 l1 cache , 并修改了 该值

之后

cpu1 要读内存地址A的值 , 从哪里读

解决方案

3. 硬件维护缓存一致性,软件不需要任何操作

什么硬件:

基于 MESI 协议 的 SCU(Snoop control unit)

multi cluster 新增问题

cluster0 和 cluster1 一致性问题

问题描述

cluster0 读 了内存地址A的值 , 缓存到 cluster0 的 l1 cache , 并修改了 该值

之后

cluster1 要读内存地址A的值 , 从哪里读

解决方案

3. 硬件维护缓存一致性,软件不需要任何操作

什么硬件:

多cluster:基于 (AMBA4)ACE 协议 的 CCI控制器

众cluster:基于 (AMBA5)CHI 协议 的 CCN控制器

|