һ������

? ? ? ?SPI��Ӣ��Serial Peripheral interface����д,����˼����Ǵ�����Χ�豸�ӿڡ���Motorola��������MC68HCXXϵ�д������϶���ġ�SPI�ӿ���ҪӦ����EEPROM,FLASH,ʵʱʱ��,ADת����,���������źŴ������������źŽ�����֮�䡣SPI,��һ�ָ��ٵ�,ȫ˫��,�̾���ġ�ͬ����ͨ������,������оƬ�Ĺܽ���ֻռ���ĸ���,��Լ��оƬ�Ĺܽ�,ͬʱΪPCB�IJ����Ͻ�ʡ�ռ�,�ṩ����,���dz������ּ����õ�����,����Խ��Խ���оƬ����������ͨ��Э��

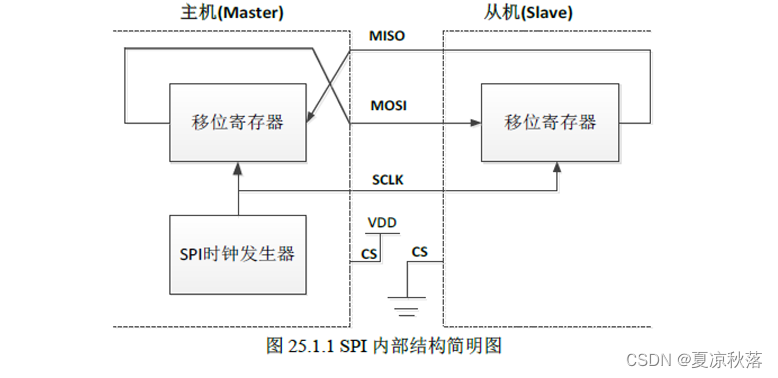

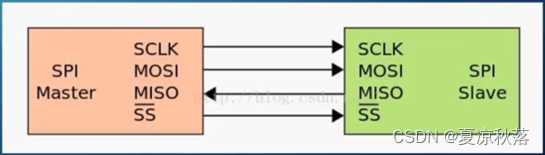

����ͼ��ʾ,SPI�ӿ�һ��ʹ��4����ͨ��:

MISO ���豸��������,���豸���������

MOSI ���豸�������,���豸�������롣

SCLK/SCKʱ���ź�,�����豸������

CS���豸Ƭѡ�ź�,�����豸����(CS,��ʱ���ֳ�ΪNSS),�͵�ƽ��Ч

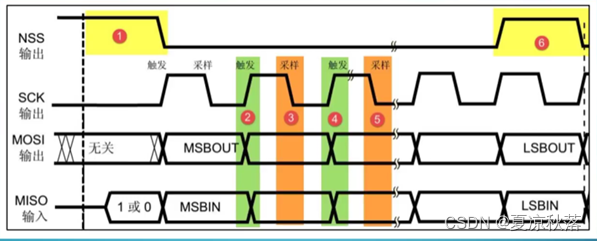

��ʼ�ź�:CS/NSS/SS�ɸߵ�ƽ��Ϊ�͵�ƽ

��ֹ�ź�:CS/NSS/SS�ɵ͵�ƽ��Ϊ�ߵ�ƽ

SPI��Ҫ���������п���,��ʼ���߽��������������ơ�SpiЭ��ͨ��������ȴ����λ,Ȼ���ٴ����λ��

SPI��Ҫ�ص���:����ͬʱ�����ͽ��մ�������;���Ե���������ӻ�����;�ṩƵ�ʿɱ��ʱ��;���ͽ����жϱ�־;д��ͻ����;���߾��������ȡ�

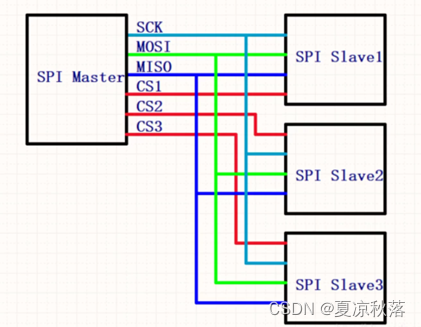

SPI�����豸ͨ���������ͼ��ʾ:ͨ��ʱͨ��cs�źŽ�������,�Ӷ�ѡ�����Ǹ��豸����ͨ�š�

����ʱ��˵��

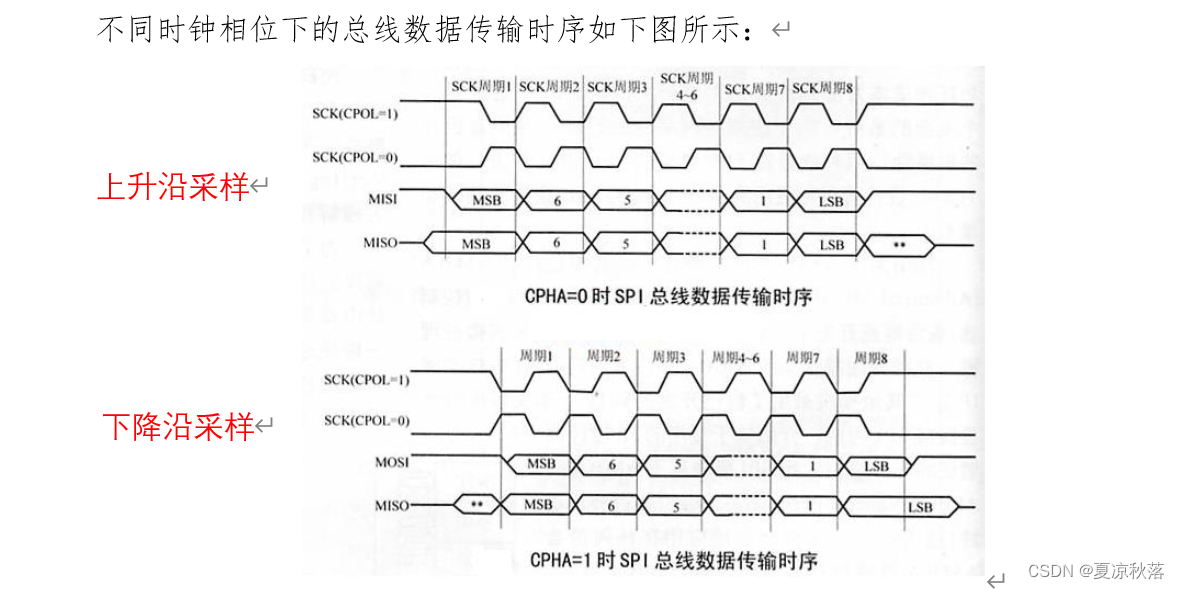

? ? ? ? SPI�������ֹ�����ʽ:SPI ģ��Ϊ�˺�����������ݽ���,�������蹤��Ҫ��,���������ͬ��ʱ�Ӽ��Ժ���λ���Խ�������,ʱ�Ӽ���(CPOL)�Դ���Э��û���ش��Ӱ�졣���CPOL=0,����ͬ��ʱ�ӵĿ���״̬Ϊ�͵�ƽ;���CPOL=1,����ͬ��ʱ�ӵĿ���״̬Ϊ�ߵ�ƽ��ʱ����λ(CPHA)�ܹ���������ѡ�����ֲ�ͬ�Ĵ���Э��֮һ�������ݴ��䡣���CPHA=0,�ڴ���ͬ��ʱ�ӵĵ�һ��������(�������½�)���ݱ�����;���CPHA=1,�ڴ���ͬ��ʱ�ӵĵڶ���������(�������½�)���ݱ�������SPI��ģ�����֮ͨ�ŵ����豸ʱ����λ�ͼ���Ӧ��һ�¡�

��ͬʱ����λ�µ��������ݴ���ʱ������ͼ��ʾ:

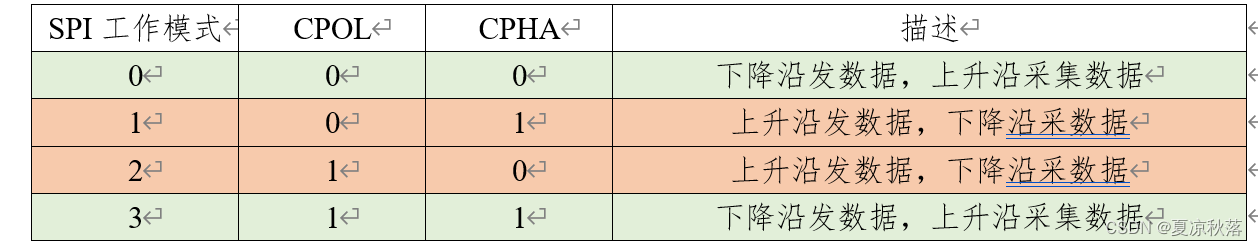

�����ʹԻ�����ģʽ��Ҫƥ��,����������,�����Ӧ��ϵ���±���ʾ:

�����ʹԻ�����ģʽ��Ҫƥ��,����������,�����Ӧ��ϵ���±���ʾ:

SPIһ֡���Դ���8λ����16λ,��Ҫ��SPI_CR1������

SPI��fpga��ʵ��ʱ,���Բ����������л�(һ��always������,һ��always�������ݵķ���)/״̬��(ͨ������һ��ʽ��������ʽ)ʵ�֡�

����SPI�����ƺ�ȱ��

(1)SPIͨѶ������

? ȫ˫������ͨ��;

? �������ݴ������ʡ�

? ����������;

? �����������ݴ���,������8λ,�������������С����;���Բ��ñ�ͷ�ͱ�β,ֻҪcs���;Ϳ�ʼ�źŵĴ��䡣

? �dz���Ӳ���ṹ����վ����ҪΨһ��ַ(��I2C��ͬ)���ӻ�ʹ������ʱ��,����Ҫ����ʱ������/����(��UART��ͬ)������Ҫ�շ���(��CAN��ͬ)��

? ���ȷ��͵�Ϊ���ݵĸ�λ

? ��cs�ź����Ͷ�Ӧ�����������Ǹ��Ǹ����������źš�

? ȫ˫��ͬ������,�ٶ�Լ��50Mbps,��Լ5.9MB/s

(2)SPI��ȱ��

? û��Ӳ���ӻ�Ӧ���ź�(���������ڲ�֪��������������);

? ͨ����֧��һ�����豸(ͨ����Ƭѡ�ź�����,�Ӷ�ȷ��Ҫͨ�ŵ����Ǹ�Ԫ����);

? ��Ҫ���������(��I2C��ͬ);

? û�ж���Ӳ������Ĵ�����Э��;

? ��RS-232��CAN�������,ֻ��֧�ַdz��̵ľ���;

? Spi�Ŀɿ��������ֻ��1~3m��

�ġ��ο�����

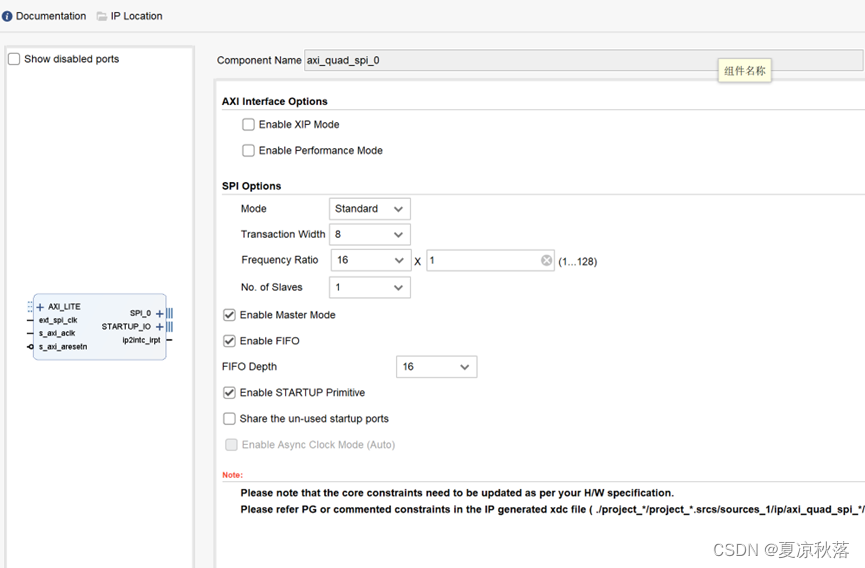

Enable XIP Mode: XIPʹ��AXI4 �� AXI4-Lite(����ΪAXI4�ļ汾)�ӿ�,��ַģʽ����ѡ��24bit��32bit;

Enable Performance Mode: ʹ��AXI4�ӿ�;ʹ��AXI4�ӿڿ����ں˵ķ��ͺͽ���FIFO��ַ������ͻ�����ܡ�����ʹ��performanceģʽʱ,AXI4-Lite����ʹ�á�

Mode: standard(����SPI,CS��CLK��SIO)/dual(�ĸ���:CS��CLK��SIO1��SIO2)/quad(������:CS��CLK��SIO1��SIO2��SIO3��SIO3)

Transacton Width: 8/16/32����˫SPI����SPIģʽ��,������ȱ�����Ϊ8λ����XIPģʽ��,��������ڱ�ģʽ��˫ģʽ����ģʽ�б�����Ϊ8��

Ƶ�ʱ���:2~2048, ������SPI��sck = ext_spi_clk/ratio ;

NO. of Slave: ������slave�ĸ���;1~32;

Enable Master Mode: ����ģʽѡ��,�ڱ�ģʽ�¿���ѡ��,����ģʽֻ֧����ģʽ

Enable FIFO: ʹ��fifo

Enable STARTUPEn Primitive: ��ѡʱ������а���STARTUPԭ��,δ��ѡʱʡ��ԭ�7ϵ��fpga����STARTUPE2ԭ��,UltraScale�豸����STARTUPE3ԭ��������ⲿSPI���豸����SPIʱ��ʱ�����á����ԭ�����豸�Ĵ���ģʽ�����DZ����õġ�

Enable Async Clock Mode: ֻ�е����Ĵ��ڶ���ģʽ,��axis�ӿں��ⲿSPIʱ������λ/���Ժ�Ƶ�ʷ��治ͬʱ,�����ô�ѡ���ѡ����IP�������б����á��˲����������ӵ����ĵ�ʱ���Զ����������AXIʱ�Ӻ�ext_spi_clk��ͬ����,�ò�������Ϊ0;������첽��,�ò�������Ϊ1��

�塢�ο�����

˵��;DI����,DO���