文章目录

一、微处理器外部结构

――表现为数量有限的输入/输出引脚(构成了微处理器级总线)

8086/8087共40个引脚,是16位CPU,有20根地址线,可以寻址1MB。

IO端口-传输信息的通道,一个IO端口至少占用一个IO地址,简称为IO端口地址。

统一编编址的优缺点,如8051和8031

| 统一编址优点 | 统一编址缺点 |

|---|---|

| 浪费存储器的地址空间,没专用的IO操作指令 | IO驱动程序编写简单、灵活 |

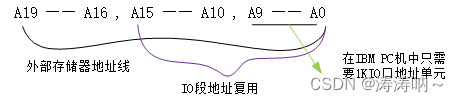

8086CPU采用的是独立编址,用M/IO来区分是对IO编址还是存储器编址

| 独立编址优点 | 独立编址缺点 |

|---|---|

| 节约存储器地址空间 | 指令记忆复杂,IO程序设计不灵活 |

8086存储器寻址方式有5种!而IO操作寻址方式只有2种。

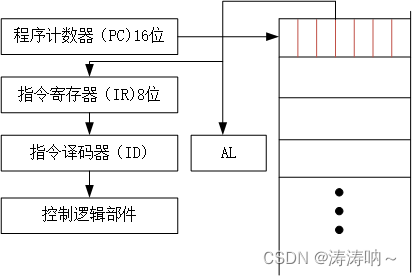

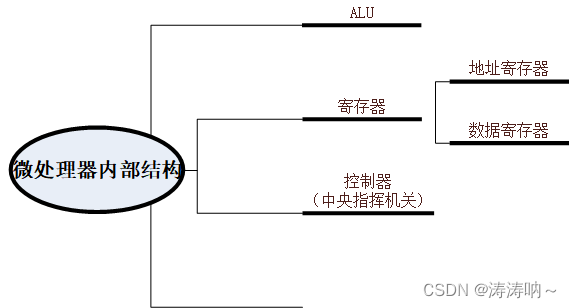

二、一般微处理器内部结构

例如指令MOV AL 20H

这条指令用到了2个地址空间,这种结构的微处理器是先取指令再执行指令,效率比较低!

堆栈:由先进后出原则组织的一段存储器区域

8086:堆栈必须按照字操作

三、8086/8088 CPU内部结构

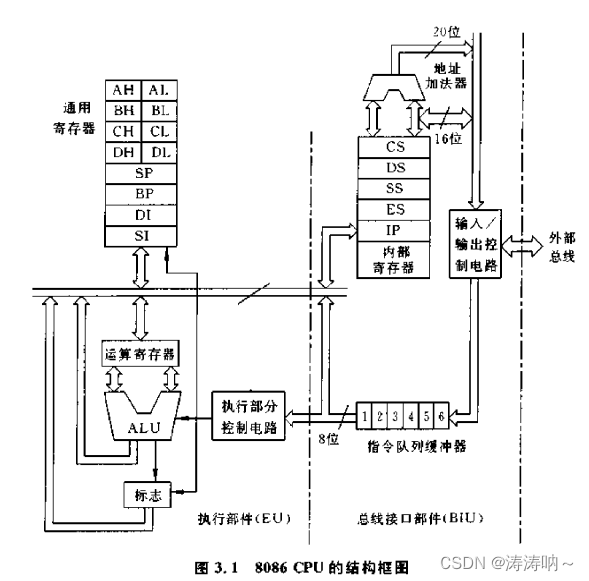

一般微处理器内部结构工作效率低,所以intel公司提出了8086内部机构。

8086CPU内部存储单元分为段地址和段内地址,将存储器分为多个段,一段是64Kb。

8088内部的指令队列寄存器是4字节组成的,与8086之间唯一的区别。

BIU―主要负责从外部存储器中取指令,并将取得指令放入指令队列中。

EU―负责从指令队列中获取指令,遵循“先进先出”原则,并对该指令加以执行。

BIU“休息”时间:EU要用总线了

EU“休息”时间:指令队列为空

在这种情况下总线一直在工作状态,总线利用率很忙!

通用寄存器:组成8086汇编语言程序设计的编程逻辑。

三、8086 CPU内部寄存器组成

8086CPU共有14个16位寄存器

3.1通用寄存器(8个)

(1)数据寄存器(4个)

4个数据寄存器可以作为16位寄存器也可以作为8位寄存器

AX(AH\AL) ――累加器,AX是16位累加器,AL是8位累加器

BX(BH\BL) ――基址寄存器(段内的地址可以用BX操作)(默认在数据段)

CX(CH\CL) ――计数器

DX(DH\DL) ――数据寄存器,再IO端口的in和OUT中可以作为IO地址寄存器

(2)地址指针(2个)与变指寄存器(2个)

SP――堆栈指针寄存器(默认在堆栈端)

BP――地址指针寄存器

SI――源变址寄存器

DI――目的变址寄存器

后三个找的的那元都默认在数据段

3.2段寄存器

CS――代码段寄存器

DS――数据段寄存器

ES――附加数据段寄存器

SS――堆栈段寄存器

CS的初始值不能由用户进行,由操作系统完成

后面三个寄存器用户需要对其进行初始值设定

3.3控制寄存器

IP――指令指针寄存器,不能做目的地址

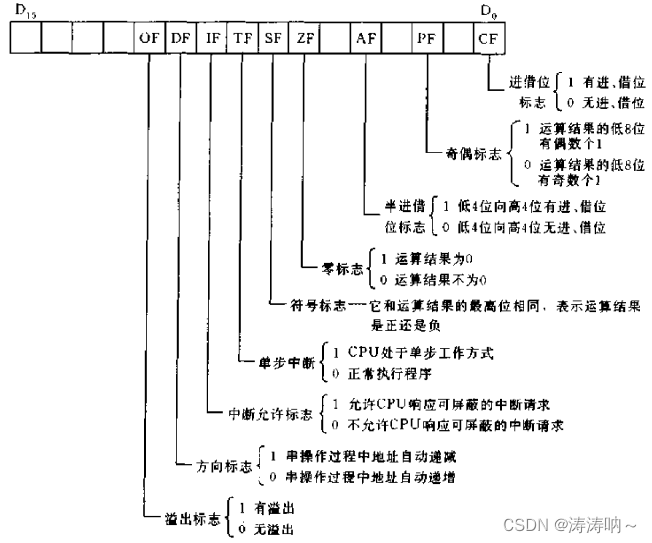

PSW――处理器状态寄存器,16位中有用的只有9位

状态标志位:SF、ZF 、PF 、CF 、AF和 OF

反映的是ALU运算后结果的状态

控制标志:DF、IF和TF,三个控制标志用于控制CPU的运行状态。

CPU的外部中断是可以屏蔽的

四、8086 CPU存储器和地址空间

4.1 8086地址空间

4.2 数据存放格式

高字节存储在高地址,低字节存储在低地址!

一个字有16位,在对字进行数据操作时为提高速度,尽量将字定义在偶字节。

4.3 存储器的分段与物理地址的形成

1、存储器为什么要进行分段?

16位地址线没法直接对1M字节的存储单元进行寻址,所以要将存储器进行分段处理。

2、存储器怎么分段?

每个逻辑段最大为64K,每个逻辑段的起始地址必须能被16整除!

每个存储单元只有唯一的物理地址,和不同的逻辑地址!逻辑地址表示为:

16位段地址:16位段内偏移地址

每个逻辑单元的物理地址PA为:段地址*16+段内偏移地址(即段内有效地址EA)