数字IC设计笔试题汇总(一)

快秋招了,这篇博客记录了一些最近看见的数字IC设计相关的笔试题,我的答案不一定对,仅供参考

1. 用100MHz的时钟A去采样200MHz的时钟B(与A无关)产生的8bit信号是同步采样还是异步采样?采样时需要注意哪些问题?怎样解决?

慢时钟信号对快时钟信号的采样应为异步采样。200MHz下产生的信号长度为5ns,而100MHz时钟的周期为10ns(10ns采样一次),所以如果只采用同步采样的话,可能会难以捕捉到信号;

需要注意的问题:即使是异步采样,如果A持续产生8bit信息,可能导致B无法及时采样到这些信息(时钟A输出一个信息为5ns,B为10ns);

怎样解决:根据具体的电路特性,引入一个FIFO存储来不及被B采样的信息。

2. 用100MHz的时钟A去采样50MHz的时钟B(与A无关)产生的1bit信号是同步采样还是异步采样?采样时需要注意哪些问题?怎样解决?

快时钟信号对慢时钟信号的采样应为同步采样。50MHz下产生的信号长度为20ns,而100MHz时钟的周期为10ns(10ns采样一次),所以采用同步采样完全可以捕捉到50Mhz产生的信号;

需要注意的问题,怎样解决:暂时想不到有啥需要注意的,想到了再来补充;

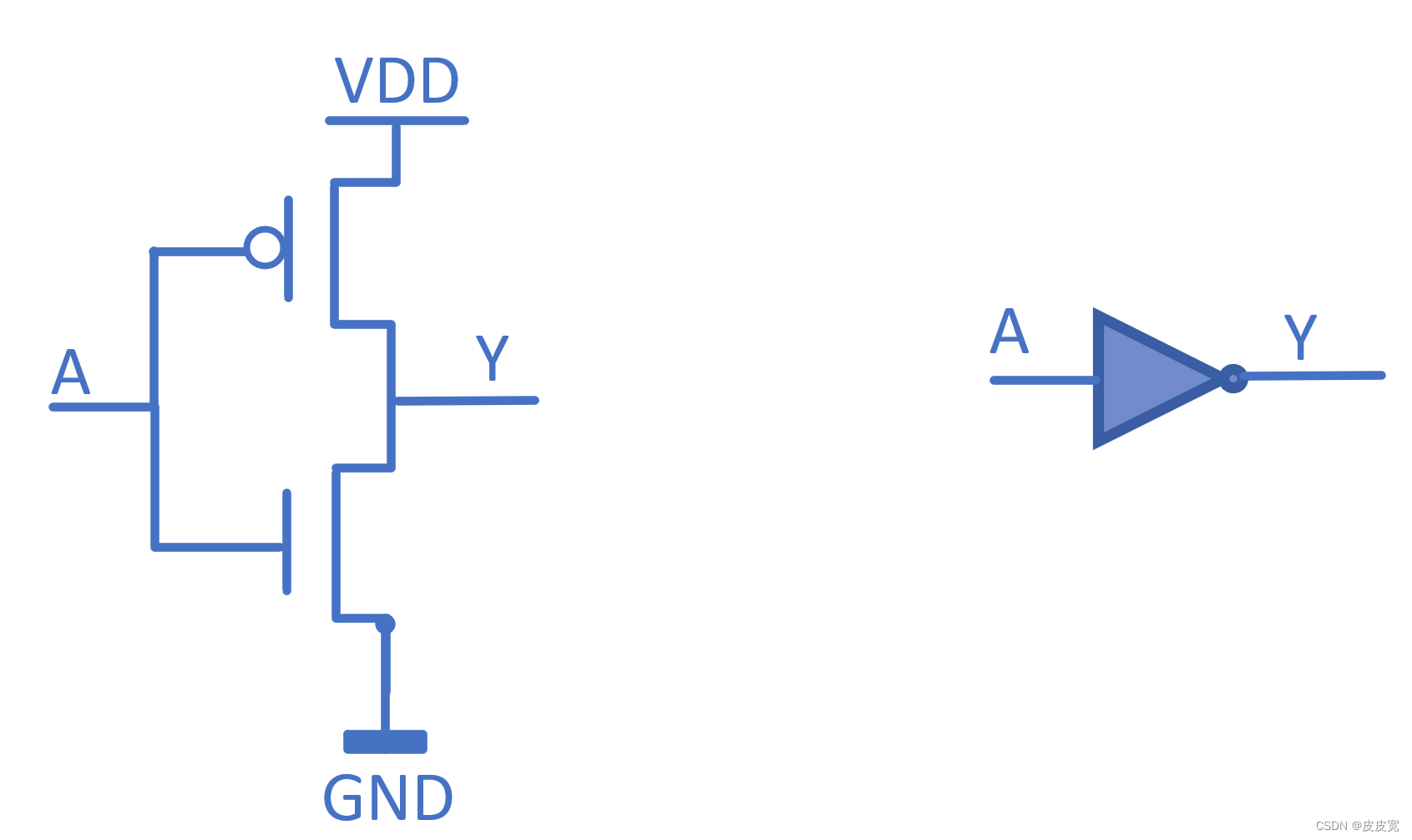

3. 请画出CMOS反相器的电路图,是否可以PMOS和NMOS位置互换?原因是?

不能互换; MOS管通常在电路中起到开关的作用,其他条件不变的情况下,栅极的电压大小,决定了漏极和漏极之间电流的大小;对于NMOS(下方MOS管),当栅极(A)的电压大于一定的值就会导通,而对于PMOS(上方MOS管),栅极(A)的电压小于一定的值就会导通。当A为高电平时,NMOS管导通,PMOS管截止,Y为低电平;当A为高电平时,NMOS截止,PMOS导通,Y为高电平;从而实现反相器的功能。若NMOS和PMOS互换,则A为高电平时,Y也为高电平,A为低电平时,Y也为低电平,无法起到反相器的作用。

4. 是否了解(激光雷达的)测距基本原理,可举例简速;

根据发送和接收信号的时间差来计算距离。发送端A在 t 1 t_{1} t1?时刻发射出一道光或者声波信号,遇到B后被反射回来,A接收到反射信号的时间为 t 2 t_{2} t2?,假设发射出的信号速度为 c c c,则A与B之间的距离为 s = c ? ( t 2 ? t 1 ) s =c*(t_{2}-t_{1}) s=c?(t2??t1?)

5. 芯片领域常用的名词解释:DSP? DMA? SIMD? Noc? 传统经典RISC架构的CPU有哪5级流水?

- DSP: 数字信号处理(Digital Signal Processing,DSP),简单来说就是处理数字信号的芯片;

- DMA:DMA(Direct Memory Access,直接存储器访问) 允许外部设备和存储器之间直接读写数据,不需要通过CPU干预。

- SIMD: 全称Single Instruction Multiple Data,单指令多数据流,能够复制多个操作数,并把它们打包在大型寄存器的一组指令集。简单来就是一个指令能处理多个操作数,比如 a = [ 1 , 2 , 3 , 4 ] , b = [ 5 , 6 , 7 , 8 ] a=[1,2,3,4],b=[5,6,7,8] a=[1,2,3,4],b=[5,6,7,8],执行SIMD的指令可直接完成 c = a + b c=a+b c=a+b;

- Noc: 片上网络(NoC:Network-on-Chip)是一种针对多核SoC设计的新型片上通信架构, 是在单个芯片上实现的基于网络通信的电子系统,其形态是集成电路芯片。

- 传统经典RISC架构CPU的5级流水: 取指,译码,执行,访存,回写;

6. CPU中,MMU基本作用?WatchDog基本作用?从计算机体系结构方面说一两个影响中断嵌套深度的因素?CPU复位需要注意哪两种时序问题?

- MMU基本作用:MMU是Mermory Management Unit(内存管理单元),当CPU访问某个内存地址时,MMU负责将CPU想访问内存的虚拟地址(或逻辑地址)转换为物理地址;

- WatchDog的作用:看门狗,简单来说就是,设计一个定时器,该定时器内部的计数器随时间递增,当增加到某个值时,系统强制复位,而当程序正常运行时,每隔一段时间就会将该定时器清零,这样系统就不会被复位,而当程序出现故障,无法正常运行时,自然难以及时清理计数器,这是WatchDog(看门狗)就会将系统强制复位,从而解决程序跑飞的问题。

- 中断嵌套深度的因素:中断或更高级的中断来临时,系统将当前执行的程序的位置保存到堆栈中,当更高级的中断的程序执行完毕后,再陆续从堆栈中取出程序地址,继续执行之前未完成的指令,因此,堆栈的容量影响中断嵌套的深度。

7. 请写出常用的低功耗设计思路

- a. Power gating 电源门控技术: 就是关闭暂时不用的模块,比较简单粗暴;

- b. 多电压供电技术:简单来说,就是对不同的模块,根据其特性分配不同的电压,从而达到降低整体功耗的效果;

- c. clock gating 门控时钟技术:只保留当前运行的模块的时钟信号,对于其他模块的时钟信号始终为0,从而减少系统的触发器的无效翻转,从而降低整体功耗;

- d. 寄存器传输级降低功耗技术:(1)资源共享。如果实现计算较多的逻辑,一定要共享计算结果,防止在不同位置重复计算;(2)去除多余的转换。

8. 请简要解释什么是MOS管的动态功耗,静态功耗;

动态功耗:动态功耗指芯片在工作中,晶体管处于跳变状态所产生的功耗 。

静态功耗:静态功耗是指漏电流功耗,是电路状态稳定时的功耗。

简单来说,就是系统内各个电平信号变换翻转产生的功耗就是动态功耗,系统内各个位置电平不变时,产生的功耗为静态功耗;

9. 请简述sram相关问题,a. Single-port sram(单端口)和dual-port sram(真-双端口)的差别;b.Two-port sram(伪双端口sram)和dual-port sram的差别(指可以支持同时读写的双端口sram)

| RAM类型 | 官方解释 | 数据读写接口数量 | 地址接口数量 |

|---|---|---|---|

| 单端口 | 允许通过一个端口对存储进行读写访问 | 1 | 1 |

| 伪双端口 | 提供了两个端口A和B, 通过端口A进行写访问,通过端口B进行读访问 | 1 | 2 |

| 双端口 | 提供两个端口A和B, 这两个端口都可以对存储进行读写操作 | 2 | 2 |

10. 请简述以下两种RTL语句的区别,然后比较他们之间的优劣。

(a)assign OUT1 = (SEL === 0) ? IN1 : IN2;

(b)always(*)

if(SEL === 0)

OUT1 = IN1;

else

OUT1 = IN2;

(b)中,OUT1为reg类型,always(*)表示对所以输入信号电平敏感,如果SEL未发生变化,那么初始OUT1为不稳定态,而(a)中的OUT1为wire类型,OUT1初始会通过判断SEL赋值;

PS: 实际综合出的电路,这两种写法并无区别,虽然b中需要将OUT1定义为reg类型,但综合后仍为wire