��ע+�DZ깫����,��ʱ��ȡ���༼������~?

?���� | ���������

�Ź��ں�?|?Ƕ��ʽ���Ӵ��ͽ�?

��x86�ܹ���,���Ǿ����������ֲ���:

uint8_t?TestBytes[10]?=?{0,?1,?2,?3,?4,?5,?6, 7};

uint32_t?IntData;

IntData?=?*(uint32_t?*&)TestBytes[2];

//������

>>IntData?=?0x05040302;?//���

>>IntData?=?0x02030405;?//С����һ�����ֽ��������ȡ��ַ,Ȼ��ǿ��ת��Ϊ����ָ���ȡֵ,�ٸ�ֵ��IntData������

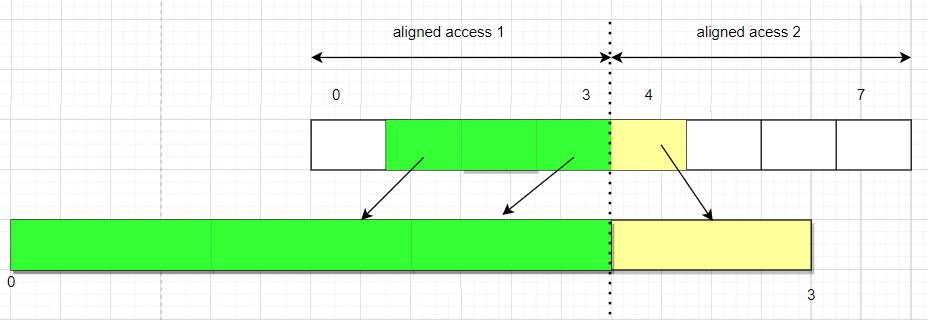

������ֵ��,���CPU�dz����С��ģʽ(Little End)�Ļ�,IntData�ĸ�ֵ�������0x5432;����Ǵ��ģʽ�Ļ�,����0x2345���൱�ڰ�����TestBytes���Ԫ��ֵ���θ�����IntData���ĸ��ֽڡ�����ͼ��ʾ:

ʹ�õ�ַǿ��ȡֵ����

���ξ�����ǰʹ�ù���оƬ�ж�����������,����Cortex-M3��M4,����PowerPC�ܹ���,����Linuxƽ̨��Ҳ������ʹ�õġ����������ʹ�ø�����FmqlоƬʱ,�ڳ�������������ƵIJ���,�������ֱ�Ӿͽ����ַ�����쳣�ж��ˡ�

���ξ���ʾ������,�ѵ��Լ�����֪��ʲô��������?�Ҵ��²²�͵�ַ�������й�ϵ�ġ����ǰ��ξ����˸�����,�Ѵ���ij������������ܹ���ȷִ��:

uint8_t?TestBytes[10]?=?{0,?1,?2,?3,?4,?5, 6, 7};

uint32_t IntData;

IntData = *(uint32_t *&)TestBytes[4];

uint16_t ShortData;

ShortData= *(uint16_t *&)TestBytes[2];

//������

>>IntData = 0x07060504;

>>ShortData?=?0x0302;����εĽ�����Կ���,ֻҪȡ�����ݵ�ַ�ǰ����ֽڶ����,���ܹ�����ִ��,����ͻ�ִ���쳣��

��������Ϊ��ջ������DDR������ô?�Ͼ�DDR�ĵ�ַȡ��һ����64λ�ġ����ǰ��ξ�����д�˸�����,�Ѷ�ջ������оƬ�ڲ���RAM��,����һ��,˵��������DDR������,����֮ǰ��Xilinx��оƬҲû�����Ƶ����Ⱑ!

Ī����IAR��������?���ξ�������������������Keil��ʵ��,Ҳ���ֹ���������,������stm32����ȴ������ִ�С�ԭ���ڡ�Cortex-M3Ȩ��ָ�ϡ�����д��:

The Cortex-M3 processor also supports unaligned data accesses, a feature previously available only in high-end processors.

�����˼����˵,Cortex-M3 ��������֧�ַǶ�������ݷ���,������ǰ���ڸ߶˴������п��õĹ���...?�ð�֪�����������˰�?����������ע���һ����:unaligned access(�Ƕ������),Ҳ������ƪ���µĺ����ˡ���������ͼ�����չʾ��оƬ�Ƕ������ʱ��ʵ�ʲ�������:�������߽�,�ײ�Ҫ����������� ,Ȼ������ݺϲ�֮����,�����ָ��ײ��ܹ�,�������ǿ������ײ�ϸ�ڵġ�

�Ƕ������ָ������

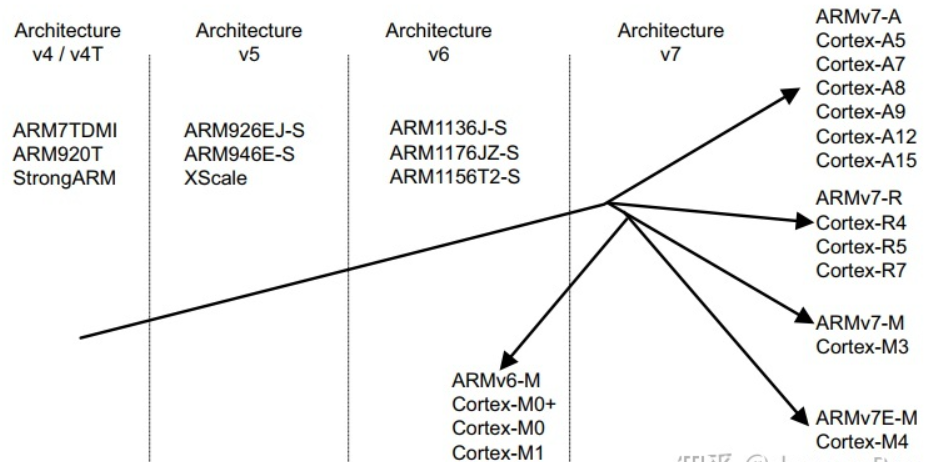

Cortex-M3֧�ַ��ֽڶ������,��ô�����õ�Fmql��ARM��֧����?Ī����оƬ�ܹ�������?���ξ���ǰ����������ᵽ��,Xilinx�õ�����ƬCortex-A9,�������õ�����ƬCortex-A7,�Dz���������оƬ��ʲôϸ�IJ�����?

������һϵ�����Ϻ�,���ξ�����,�Դ�ARM-v7�ܹ���,��֧���˷Ƕ������,���dz��õ�Cortex-M3��M4������ARM-v7�ܹ�,A7��A9����оƬҲ���Ǹüܹ��µġ�

ARM-v7�ܹ�֧�ֵ��Ӽܹ�

��ô��ȻоƬ��֧�ַǶ�����ʵ�,����ʲôԭ��ᵼ��ִ�г�����?��,�Ƕ�����ʻ�����������:

-

SCTRL.A�Ĵ�����������Ϊ0;

-

ֻ�в��ַô�ָ��֧�ַǶ������;

-

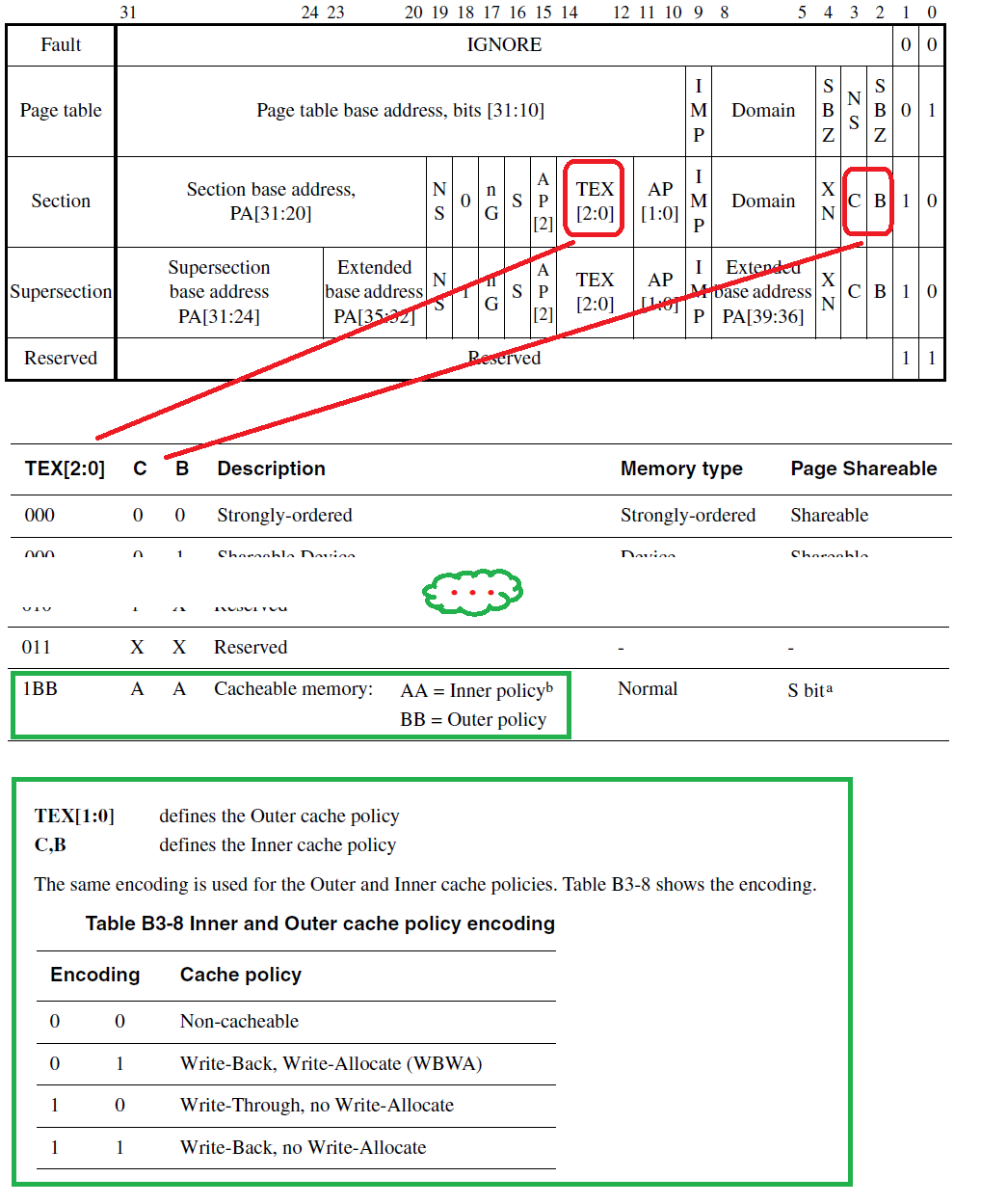

�����ʵĵ�ַ�ռ�洢�����Ͳ���Ϊstrongly-order��device-memory;

-

������ʹ���˷Ƕ�����ʡ�

������4��������?

ARM-v7֧�ַǶ�����ʵ�����

����ͼ���Կ������ָ��LDRB,LDRH,LDR,�ֱ��Ӧ C���Ե�char,short,int��LDRB�ǰ��ֽڷô��,û�ж���Ҫ��,LDRH��2�ֽڶ���(��ַҪ���� 2�ı���),LDR����4�ֽڶ���(��ַҪ����4�ı���)��

��ô���ξ��Ͱ����ⶨλ����3���͵�4����,��Ե�4��,���ȼ��IAR������,��������һ����˵��IAR�ı���ѡ�������һ�����Cno_unaligned_access�����,������ֻ���ñ��������������Ƕ�����ʵ����,������������ǿ�ƷǶ�����ʵĸ�����ʲô���á�

��Ȼ����ĸ������ڱ�����,��ô���ξ����������������?��ʵ����MMU Table�����档����Ҫʹ��MMU,������ҳ�ڴ������Ԫ,�����ʹ��,ֱ�Ӱ�strongly-ordered����(���ƼĴ����ĵ�ַ�������Ƕ�����ʵ�)��

�Ƕ�����ʱ���ʹ��MMU

��ôΪɶ��Cortex-M3��M4�ﲻ��Ҫʹ��MMU��?��Ϊ��������û��MMU����

��ôʹ��MMU��,��ô���ܸ��Ĵ洢�ռ��������?��mmu_table.s���濴��������䡣

/* (DDR Cacheable) */

SECT set SECT+0x100000

rept DDR_REG_CACHE

/* S=b0 TEX=b000 AP=b11, Domain=b0000, C=b0, B=b0 */

/*�ص������ֵ*/

????????DC32????SECT?+?0xC02?

SECT set SECT+0x100000

????????endr���0xC02���ǰ���Ƭ�洢�ռ䶨�����device memory,����ǰ���ᵽ�IJ��ܷǶ�����ʵ����;��ô��ô����?�ij�normal memory���ԡ�

/* (DDR Cacheable) */

SECT set SECT+0x100000

rept DDR_REG_CACHE

/* S=b1 TEX=b101 AP=b11, Domain=b1111, C=b0, B=b1 */

/*�ص������ֵ*/

DC32 SECT + 0x15DE6

SECT set SECT+0x100000

endr���Ǵ�ARM���ֲ�����Կ������ȥ����memory������,����ͼ��ʾ:

memory����������

���ξ���memory�������ó��˿ɶ���д��normal memory,�����������طǶ��������~

���Ǹ�����εĽ�ѵ,���ǵ�֪,���ֽڶ�����ʲ��������е�оƬ����֧�ֵ�,����Cortex-M0,�������DZ�̵�ʱ��,����Ҫ����������ֽڶ�����ʵIJ���,��������dz���Ŀ���ֲ�ԡ�

�����������ƪ���°ﵽ����,�������������������,���Ĺ�������ǰ���Ķ���~

��ע�������ں� ��Ƕ��ʽ���Ӵ��ͽ��� ��ȡ���༰ʱ��������~

??��ע+�DZ깫����,��ʱ��ȡ���༼������~?