����dz�����˽�STM32�е�ʱ����

1 ���ĵ�Ŀ��

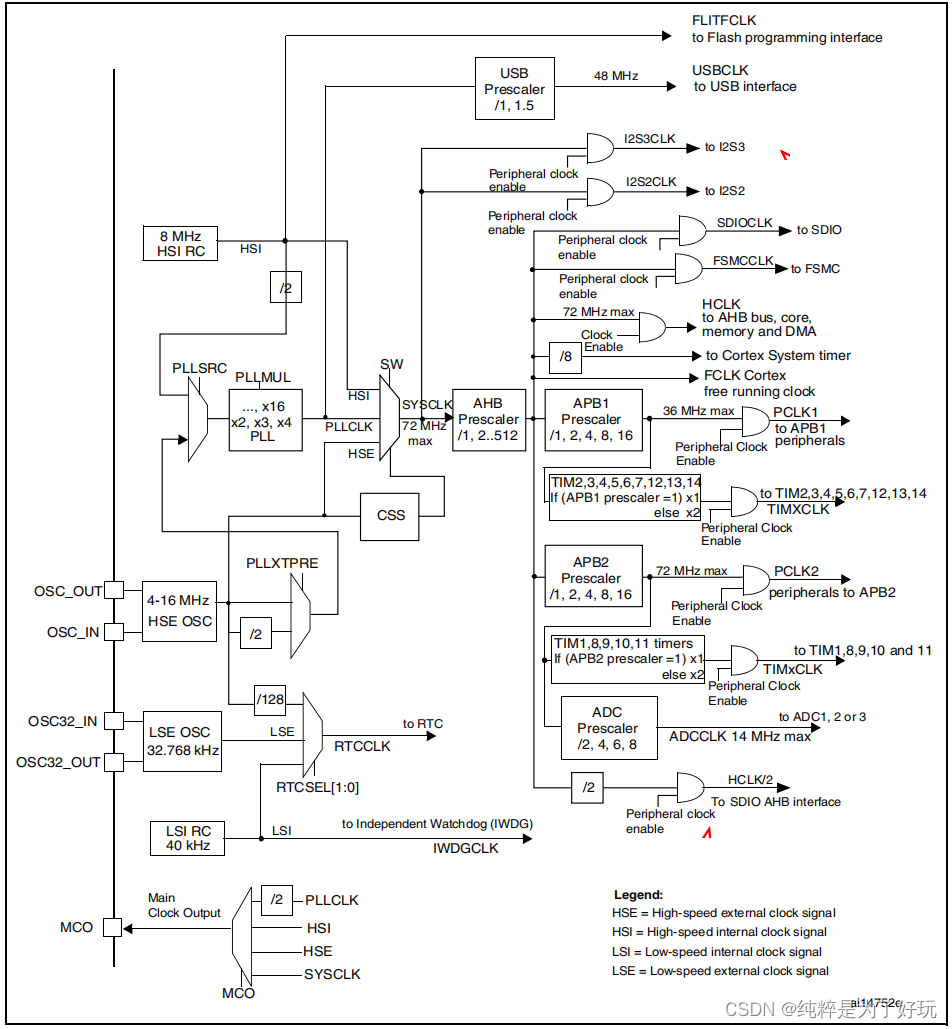

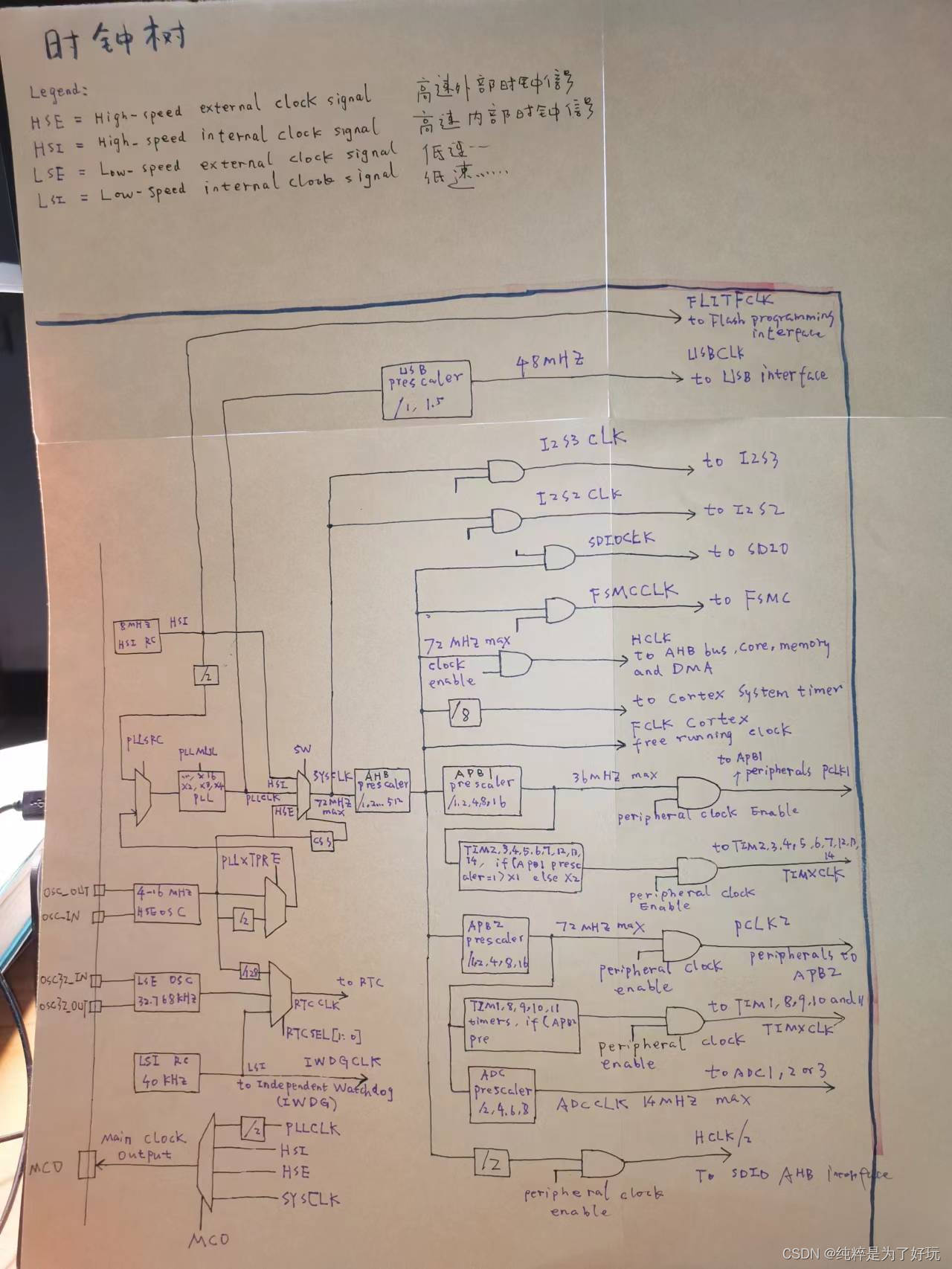

?Ū�����������ͼ,Ҳ����ʱ����

2 ����ʲô��ʱ���ź�?

������ô˵:

?In electronics and especially synchronous digital circuits, a clock signal is a particular type of signal that oscillates between a high and a low state and is utilized like a metronome to coordinate actions of circuits.

?ʱ���ź���һ���������͵��ź�,���ڸߵ�״̬֮����,���������һ��������Э����·�Ķ�����

3 ʱ���ź�����ô������?

?֮ǰд����ƪ����,�������:�� keil ��������STM32�����Ĺ���ģ��C��ϸ����

4 ʱ���ź��м���

STM32Fl03 ���ʱ�� ���Է�Ϊ���� 3 ��:

(1) ����ʱ��

(2) ϵͳʱ��

(3) ����ʱ��:��ϵͳʱ�ӷ�Ƶ�õ�

4.1 ����ʱ��

?STM32Fl03 �� ����ʱ�ӿ������Բ�ͬ��ʱ��Դ��

?��Ƶ�ʺ�Դ�Ƕ�����,��������:

?����ʱ��Ϊ STM32Fl03 ����ʱ���ṩʱ���ź�,

?����ʱ�ӽ�Ϊʵʱʱ�� (Real Time Clock, RTC) ���������Ź�(Independent Watch Dog, IWDG)�ṩʱ���źš�

?��оƬ�Ƕ�����,���Է�Ϊ�ڲ�ʱ��(Ƭ��ʱ��)���ⲿʱ��Դ(Ƭ��ʱ��)���ڲ�ʱ����оƬ�ڲ� RC��������,����Ͽ�,���ϵͳ��ʱ����оƬ���ϵ�ʱĬ�ϲ����ڲ�����ʱ�ӡ����ⲿʱ��ͨ�����ⲿ��������,�ھ��Ⱥ��ȶ����϶����кܴ�����ơ�

?���,ͨ���ϵ�֮��ͨ���������ý���ʱ��ת�������ⲿ����ʱ���źš�

(1)�����ⲿʱ��

?�����ⲿʱ�� (High Speed External clock signal, HSE)ͨ�����ⲿ������Ϊʱ��Դ,����Ƶ �ʿ�ȡ��ΧΪ 4 ~ 16MHz, ST �ٷ��Ƽ�ѡȡ 8MHz ��Ӿ�����Ϊ

STM32Fl03 �������� HSE��

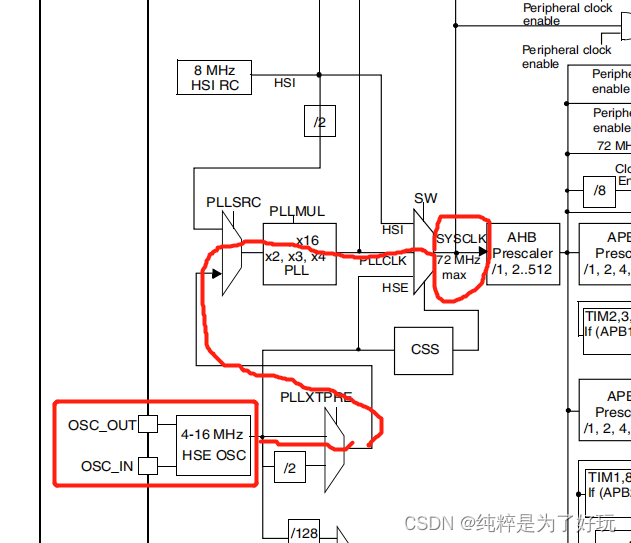

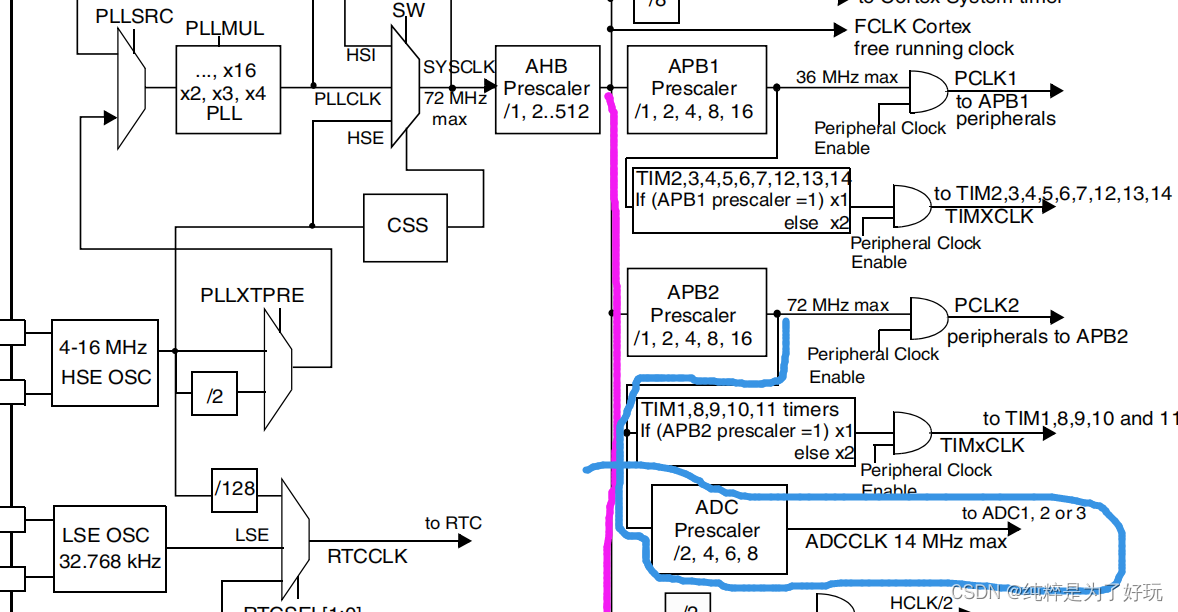

?���漴�����8MHz������Ϊ�����ⲿʱ��Ϊ��,������ͼ��STM32F103ʱ����,����STM32F103��ʱ��ϵͳ����δӸ����ⲿʱ��(8MHz����)��ʼһ�����õ�ϵͳʱ��SYSCLK��

OSC_IN �� OSC_0UT : ������˵� osc_IN �� OSC_ OUT �� ʼ,

STM32Fl03 �����������ŷֱ����ӵ� 8MHz �ⲿ��������ˡ�

PLLXTPRE: 8M �� HSE ������·ѡ���� PLLXTPRE(HSE divider for PLL entry)�� ͨ��������üĴ���,����ѡ�� PLLXTPRE����� : ������ʱ�ӵĶ���Ƶ��Ƶ�� ͨ��ѡ��Ƶ,���,���� PLLXTPRE ��,�����Ȼ�� 8MHz ��ʱ���źš�

PLLSRC: 8MHz��HSE������·ѡ����PLLSRC (PLL entry clock source)�� ͬ

������ͨ�����üĴ���,ѡ��PLLSRC ������Ǹ����ⲿʱ��HSE������ڲ�ʱ��

HSI�� ͨ��,ѡ�����Ϊ�����ⲿʱ��HSE��

PLL: 8MHz��HSE�������CPLL ),����PLL ��,���ʱ�ӳ�ΪPLLCLK�� ͨ

������PLL �Ĵ���,ѡ��Ƶϵ�� PLLMUL (PLL mul tipli cation factor),���Ծ���

PLLCLK���Ƶ�ʡ� ͨ��,Ϊ��ʹSTM32Fl03��Ƶ����,ͨ������Ƶϵ����Ϊ9�� ����,����PLL��,ԭ��8MHz��ʱ��HSE�����72MHz��ʱ��PLLCLK��

SW: 72MHz��PLLCLK������·ѡ����SW�� ͨ�����üĴ���,����ѡ��SW��

��ΪPLLCLK��HSE��HSI�� SW�������STM32Fl03��ϵͳʱ��SYSCLK,ͨ��ѡ

��PLLCLK��ΪSW����� ���,STM32Fl03��ϵͳʱ��SYSCLK Ϊ72MHz��

(2) �����ڲ�ʱ��

�����ڲ�ʱ��(High Speed Internal clock signal, HSI)��Ƭ��RC��������,Ƶ��

Ϊ8MHz,�����ȶ��� STM32Fl03���ϵ翪ʼ������HSI��Ϊ��ʼ��ϵͳʱ�ӡ�

(3)�����ⲿʱ��

�����ⲿʱ��(Low Speed External clock signal , LSE)ͨ�����ⲿ������Ϊʱ��Դ,

��Ҫ�ṩ��ʵʱʱ��ģ��,����һ�����32. 768 kHz��

(4) �����ڲ�ʱ��

�����ڲ�ʱ��(Low Speed Internal clock signal, LSI)��Ƭ��RC��������,����

�ṩ��ʵʱʱ��ģ��Ϳ��Ź�ģ��,Ƶ��Ϊ40 kHz��

4.2 ϵͳʱ��

?���Ͽ�֪,ϵͳʱ��SYSCLK �ɶ�·ѡ����SW�����û�����ѡ��PLLCLK��HSE��HSI�е�һ·������á� SYSCLK�����Ƶ�ʿɴ�72MHz(ͨ��Ҳ������72MHz), ��STM32Fl03�� ������ʱ����Դ��

?ͨ��,STM32Fl03���ϵ翪ʼ ,ѡ��HSI��Ϊ��ʼ��ϵͳʱ�ӡ� ����ɳ�ʼ����,һ��ѡ�ø����ȶ��ɿ���HSE��Ϊϵͳʱ�ӵ���Դ��Ϊ�����û��ܹ�ʵʱ���ʱ��ϵͳ�Ƿ���������,ST ��STM32Fl03 ϵ����������ר���ṩ������MCO(M ai nC lock Output,��ʱ�����)�� �û�����ͨ���������,ѡ��SYSCLK��PLLCLK��HSE��HSI�е�һ·��MCO�������

4.3 ����ʱ��

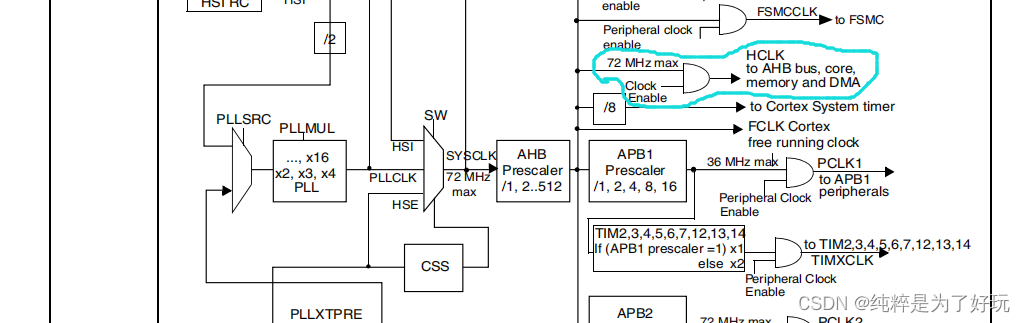

?ϵͳʱ��SYSCLK ����AHBԤ��Ƶ�������STM32Fl03�ĸ�������:

?(1)HCLK: ��������AHB��ʱ��,��ϵͳʱ��SYSCLK ��AHBԤ��Ƶ����ֱ�ӵõ��� ͨ��, ��AHBԤ��Ƶϵ������Ϊ1,HCLK�� Ϊ72MHz,��� ҲΪ72MHz�� HCLKΪCortex-M3�ں˴洢����DMA�ṩʱ���źš� �� ��Cortex-M3�ں˵�����ʱ���� �ɴ˿ɼ�, CPU��Ƶ�������ʱ���ź��� ͨ������� CPU������ �� , STM32Fl03��Ƶ��72MHz��

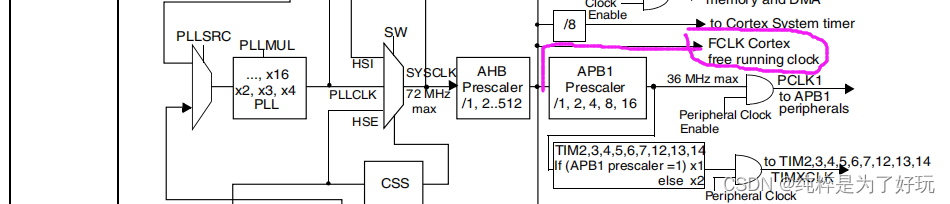

?(2)FCLK: Cortex-M3�ں˵� ���������С� ʱ��,ͬ����ϵͳʱ��SYSCLK��AHBԤ��Ƶ����ֱ�ӵõ��� ����HCLK����ͬ��,��� Ҳ ��72MHz�� ��ν�IJ����� HCLK �� �� ����HCLKֹͣʱFCLK���ܼ������С� ���� ,���Ա�֤��ʹ��Cortex-M3�ں�˯��ʱҲ�ܲ������жϺ��������¼���

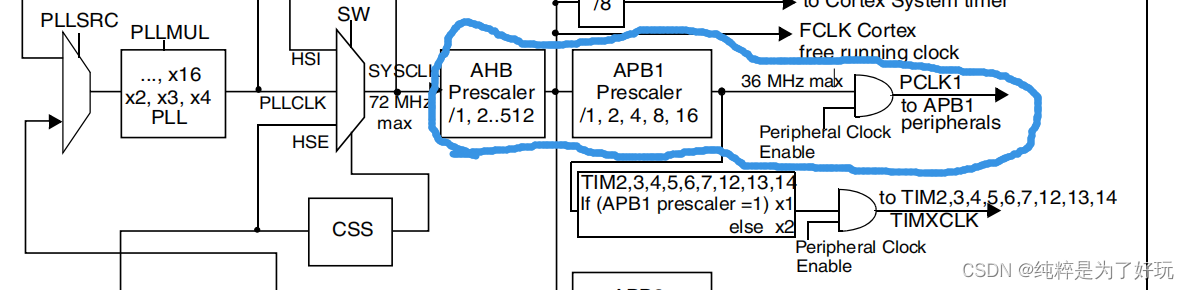

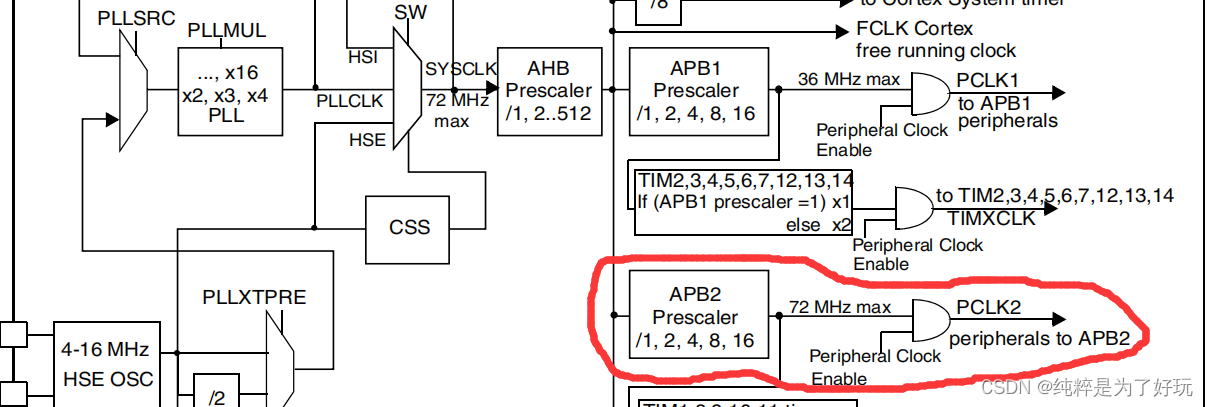

?(3)PCLK1: ����ʱ��,��ϵͳʱ��SYSCLK��AHBԤ��Ƶ��,�پ�APBlԤ��Ƶ����õ��� ͨ�������,��AHB��Ԥ��Ƶϵ������Ϊ1,��APB1 ��Ԥ��Ƶϵ������Ϊ2, PCLK1 ��Ϊ36MHz,�������Ƶ��ҲΪ36MH �� PCLK1Ϊ������APB1 �����ϵ������ṩʱ���ź�,��USART2��USART3��UART4��UART5��SPI2/I2S��SPI3/I2S��I2C1��I2C2��USB��RTC��CAN��DAC��PWR��BKP��IWDG��WWDG�ȡ����Ƶ�,����ʹ�����Ϲ�����APB2�����ϵ�����,�����ȿ���APB2�����ϸ������ʱ�ӡ�

?(4)PCLK2: ����ʱ��,��ϵͳʱ��SYSCLK��AHBԤ��Ƶ��,�پ�APB2Ԥ��Ƶ����õ��� ͨ������� ,��AHBԤ��Ƶϵ����APB2��Ԥ��Ƶϵ��������Ϊ1,PCLK2��Ϊ72MHz,�������Ƶ��ҲΪ72MH ��PCLK2Ϊ������APB2�����ϵ������ṩʱ���ź�,��GPIOA��GPIOB��GPIOC��GPIOD��GPIOE��GPIOF��GPIOG��USART1��SPI1��EXTI��AFIO�ȡ� ������Ҫע��� ��,����ʹ������ ������APB2�����ϵ����� ,�����ȿ���APB2�����ϸ������ʱ�ӡ�

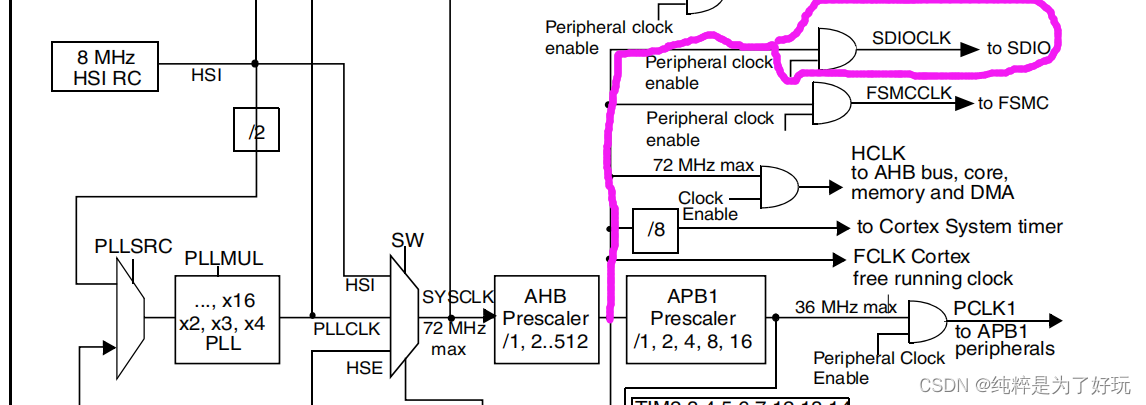

?(5)SDIOCLK: SDIO�����ʱ��,��ϵͳʱ��SYSCLK��AHBԤ��Ƶ����ֱ�ӵ�

SDI ���� ���Ƶ�,����ʹ��SDIO����,�����ȿ���SDIOCLK ��

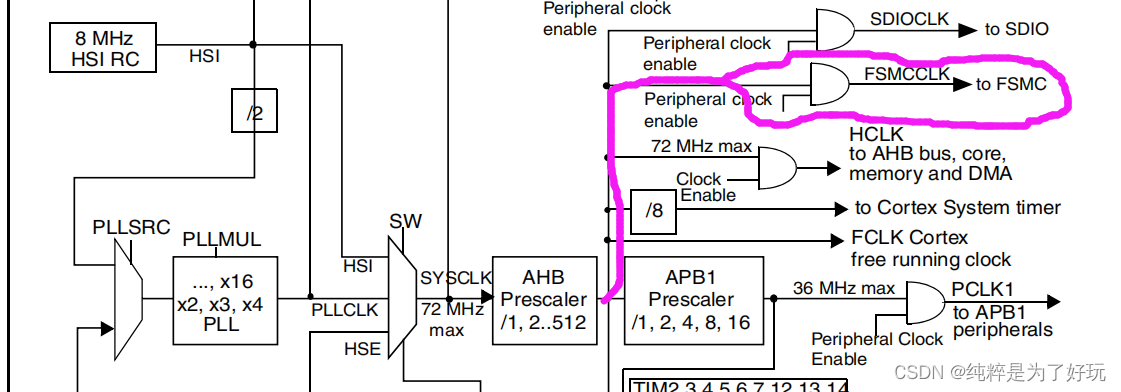

?(6)FSMCCLK: �ɱ侲̬�洢��������ʱ��,��ϵͳʱ��SYSCLK��AHBԤ��Ƶ��

��ֱ�ӵõ������Ƶ� ,����ʹ�� FSMC��Ӵ洢��,�����ȿ���FSMCCLK ��

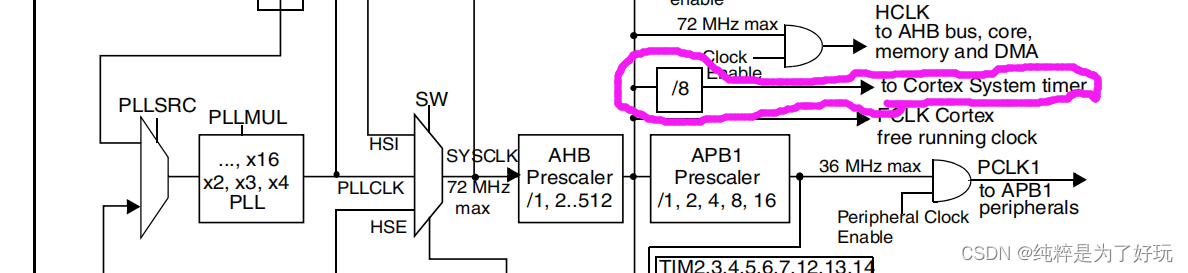

?(7)STCLK: ϵͳ��ʱ�� SYSTICK���ⲿʱ��Դ,��ϵͳʱ��SYSCLK �� AHB Ԥ��Ƶ��,�پ��� 8��Ƶ��õ�, ��ǧHCLK/8�������ⲿʱ��Դ STCLK , ϵ ͳ��ʱ��SYSTICK�����Խ�FCLK��Ϊ�ڲ�ʱ��Դ ��

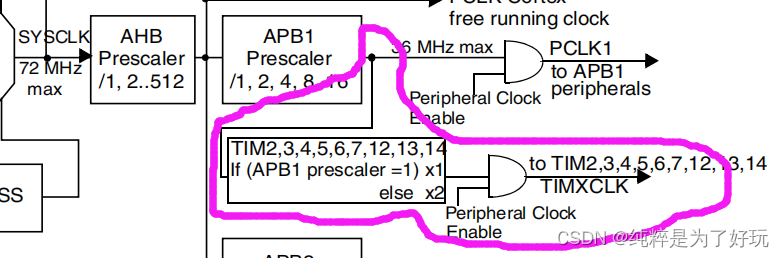

?(8)TIMXCLK: ��ʱ�� 2����ʱ�� 7���ڲ�ʱ��Դ,��APBl�����ϵ�ʱ��PCLK1 ��

����Ƶ��õ��� ���Ƶ�,����ʹ�ö�ʱ�� 2����ʱ�� 7 �е�����һ������,�����ȿ�

��APB2�����϶�Ӧ�Ķ�ʱ��ʱ�ӡ�

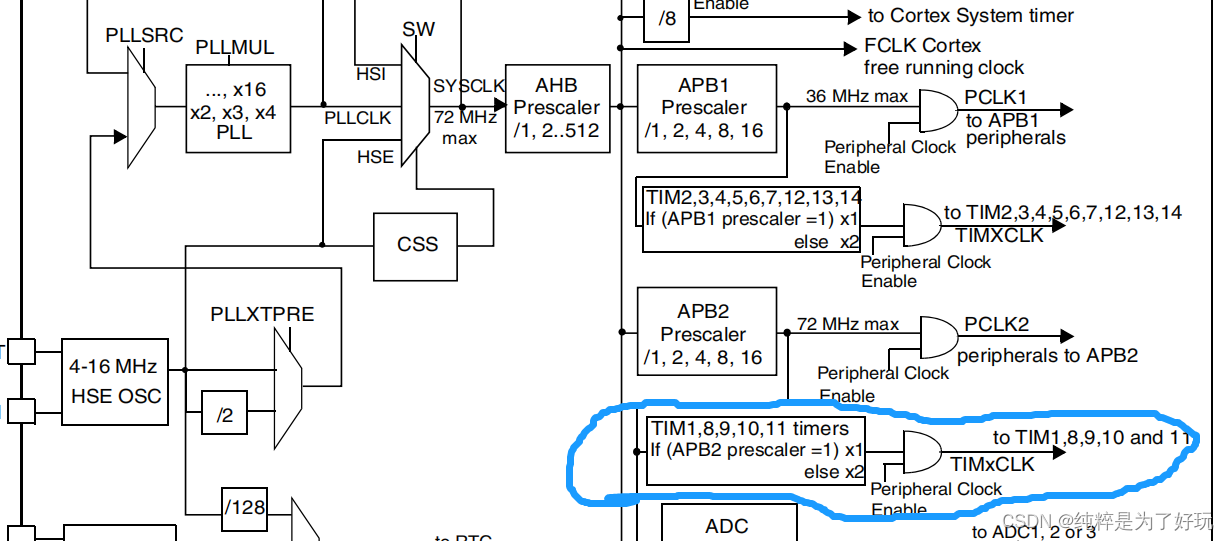

?(9)TIMxCLK: ��ʱ�� 1�Ͷ�ʱ��8���ڲ�ʱ��Դ,��APB2�����ϵ�ʱ��PCLK2��

����Ƶ��õ��� ���Ƶ�,����ʹ�ö�ʱ��1��ʱ��8 ,�����ȿ���APBl�����϶�ʱ��

1��ʱ��8��ʱ�ӡ�

?(10)ADCCLK : ADC1��ADC2��ADC3��ʱ��, ��APB2�����ϵ�ʱ�� PCLK2 �� ADC Ԥ��Ƶ���õ��� ADCCLK���Ϊ14MHz��

5 why so complication?

?���,ΪʲôSTM32Fl03��ʱ��ϵͳ ���Ե���˸�����?��Ϊ�б�Ƶ����Ƶ��һϵ������ʱ�ӵĿ��ء� ����,��Ƶ�ǿ��ǵ���ż�����,���ֱ�����һ�� 72MHz�ľ���, ���ߵ���Ƶ�ʻ��������·������Ѷȡ�

?���,��Ƶ����ΪSTM32Fl03����Ƭ������Ĺ���Ƶ�ʲ�����ͬ,���и����������� ��������, ��Ҫ�Ѹ�������͵�������ֿ�������

?���,ÿ�� STM32F103���趼�䱸��ʱ�ӿ��ء� ��ʹ��ij������ʱ, һ��Ҫ�������ʱ��;������ʹ��ij������ʱ,�����������ʱ�ӹر�,�Ӷ�����STM32�����幦�ġ�