һ.SRAM-IS62WV51216оƬ����

IS62WV51216��ISSI(Integrated Silicon Solution, Inc)��˾������һ��16λ��512K(512*16,��1M�ֽ�)(��1M�ֽ�����ô��ĺ���ὲ)������CMOS��̬�ڴ�(SRAM)оƬ��

STM32 ������оƬ�ڲ���һ����С�� SRAM,SRAM�൱�����ǵ����е��ڴ浱��������ʱ��Щ��ʱ��������Ҫ�ݴ���SRAM��,�����dz���ܴ�ʱ�����ڴ治�����Ҫ�����ڴ���չ,������������������(��Ҫ�ܶ��ַ����������),ֻ�� STM32F103ZE �������ͺŵ�оƬ�ſ�����չ�ⲿ SRAM��

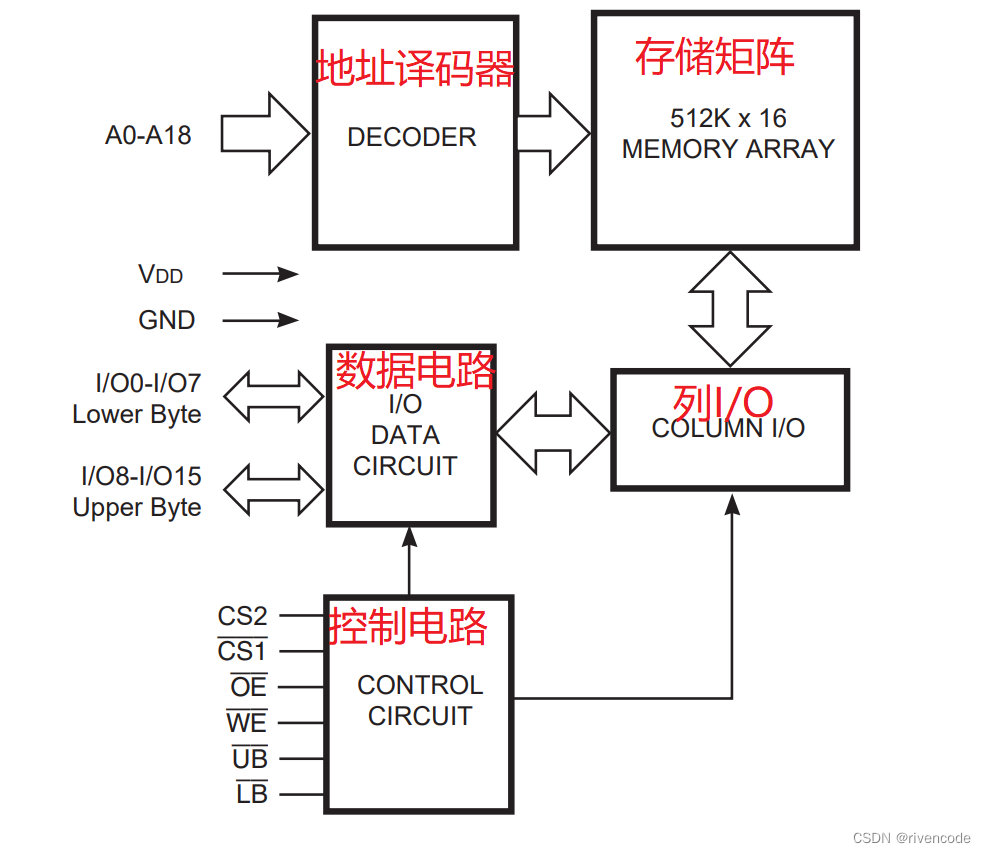

��.SRAMоƬ���ܿ�ͼ

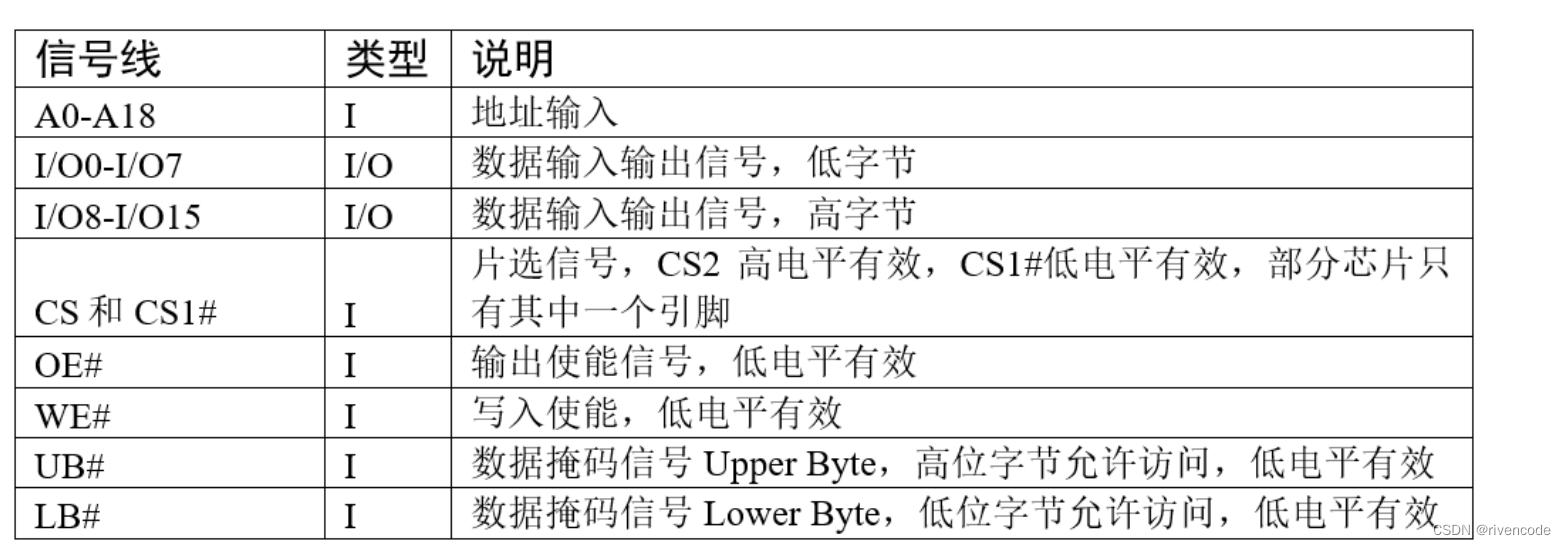

1.SRAM �ź���

ֻҪ�����ź���ʹ���˷���,�ӵ�ַ������Ҫ���ʵĵ�ַ,���ɴ� I/O������д���������ݡ�

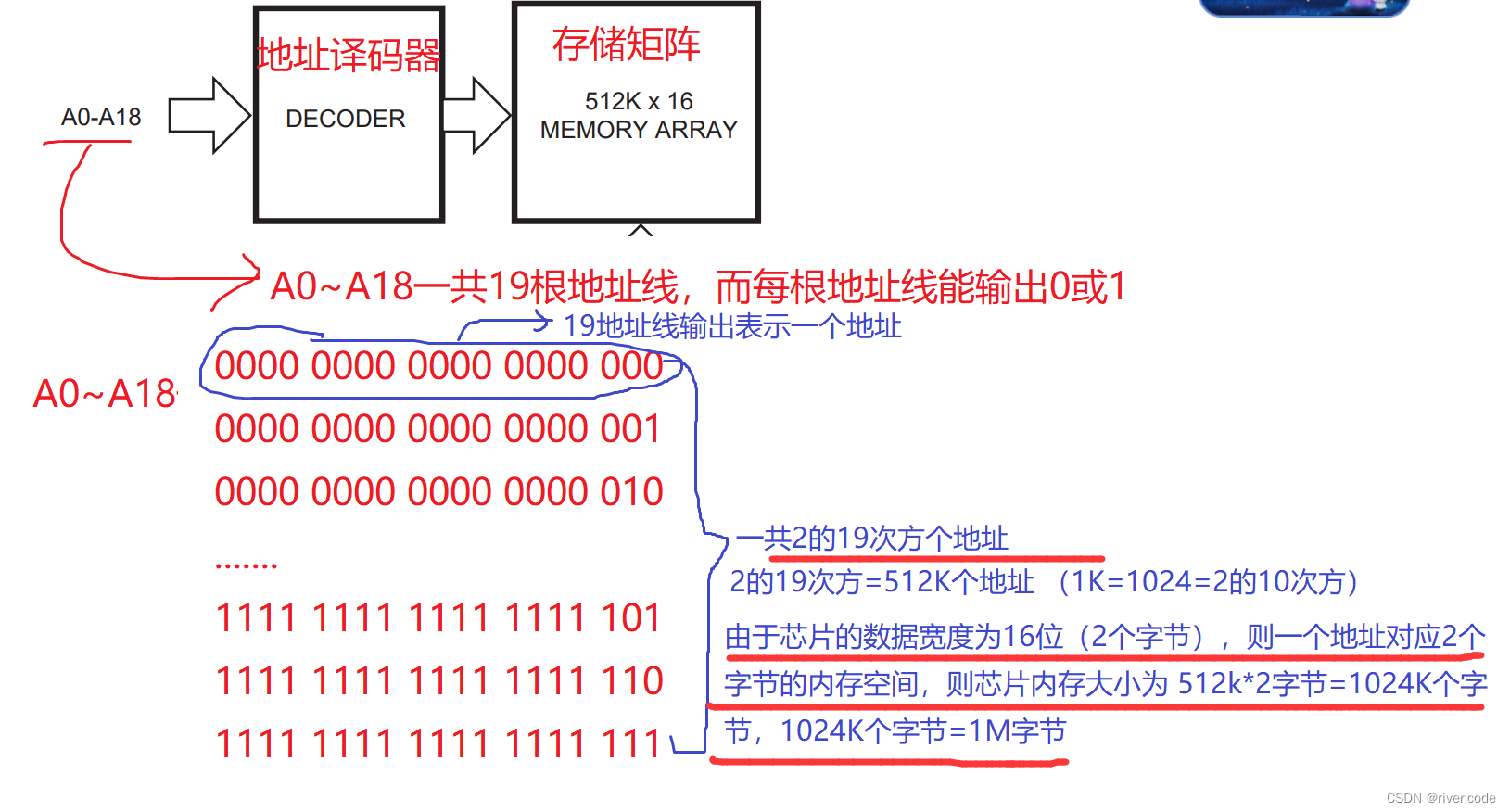

2.�洢������

SRAM �ڲ������Ĵ洢����,�����������һ�ű���,���ݾ��������ű����ϡ��ͱ������һ��,ָ��һ���е�ַ���е�ַ,�Ϳ��Ծ�ȷ���ҵ�Ŀ�굥Ԫ��,���� SRAM оƬѰַ�Ļ���ԭ����������ÿ����Ԫ��Ϊ�洢��Ԫ,�������ı���Ϊ�洢����

2.��ַ���������� I/O �� I/O ���ݵ�·

��ַ�������� N ����ַ��ת���� 2��N�η����ź���,ÿ���ź��߶�Ӧһ�л�һ�д洢��Ԫ,ͨ����ַ���ҵ�����Ĵ洢��Ԫ,ʵ��Ѱַ������洢���бȽϴ�,��ַ��ֳ��к��е�ַ,�����С��з�ʱ����ͬһ��ַ����,��������Ѱַʱ���õ�ַ�ߴ����е�ַ�ٴ����е�ַ

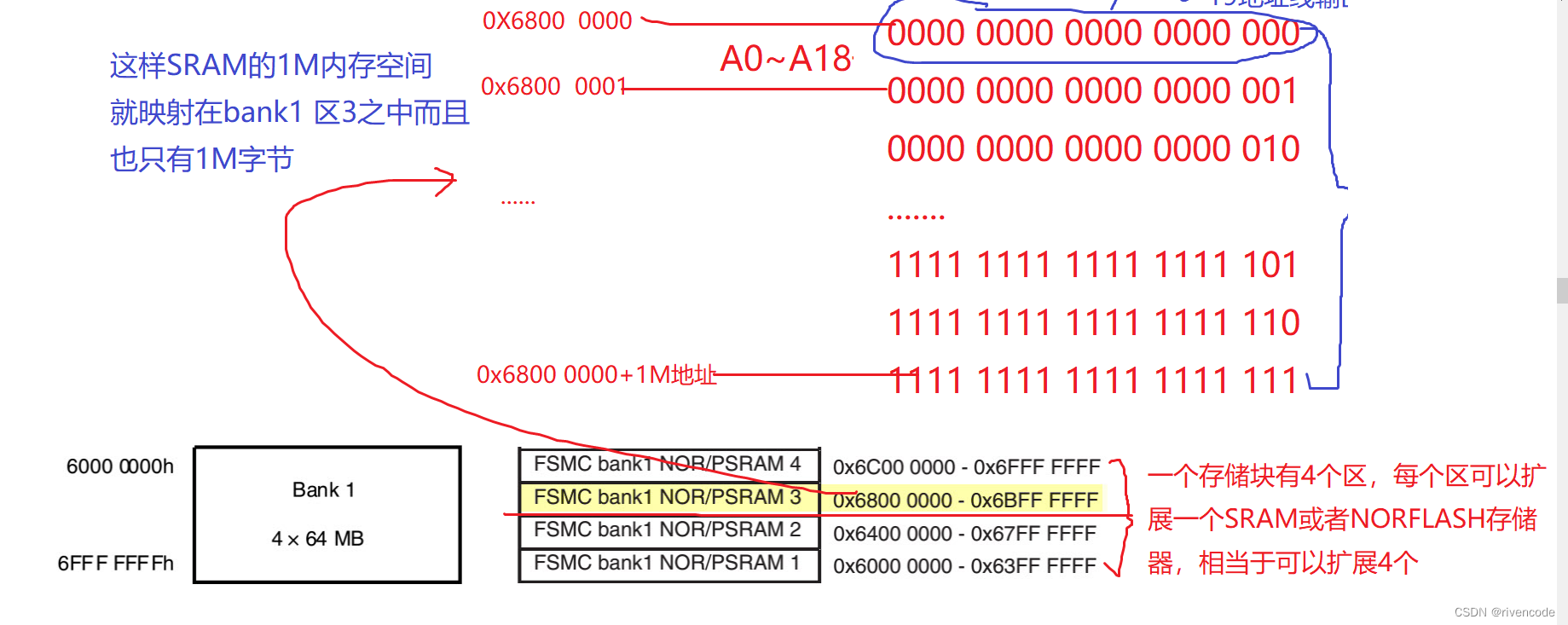

��ʵ���е�SRAM �Ƚ�С,û���е�ַ��,�������ݿ���Ϊ 16 λ,��һ���е�ַ��Ӧ 2 �ֽڿռ�,��ͼ������ A0-A18 ��19����ַ��һ�����Ա�ʾ 2��19�η�=2��8�η�x1024=512K �д洢��Ԫ,������һ���ܷ��� 512Kx2�ֽھ͵���1M�ֽڴ�С�Ŀռ䡣

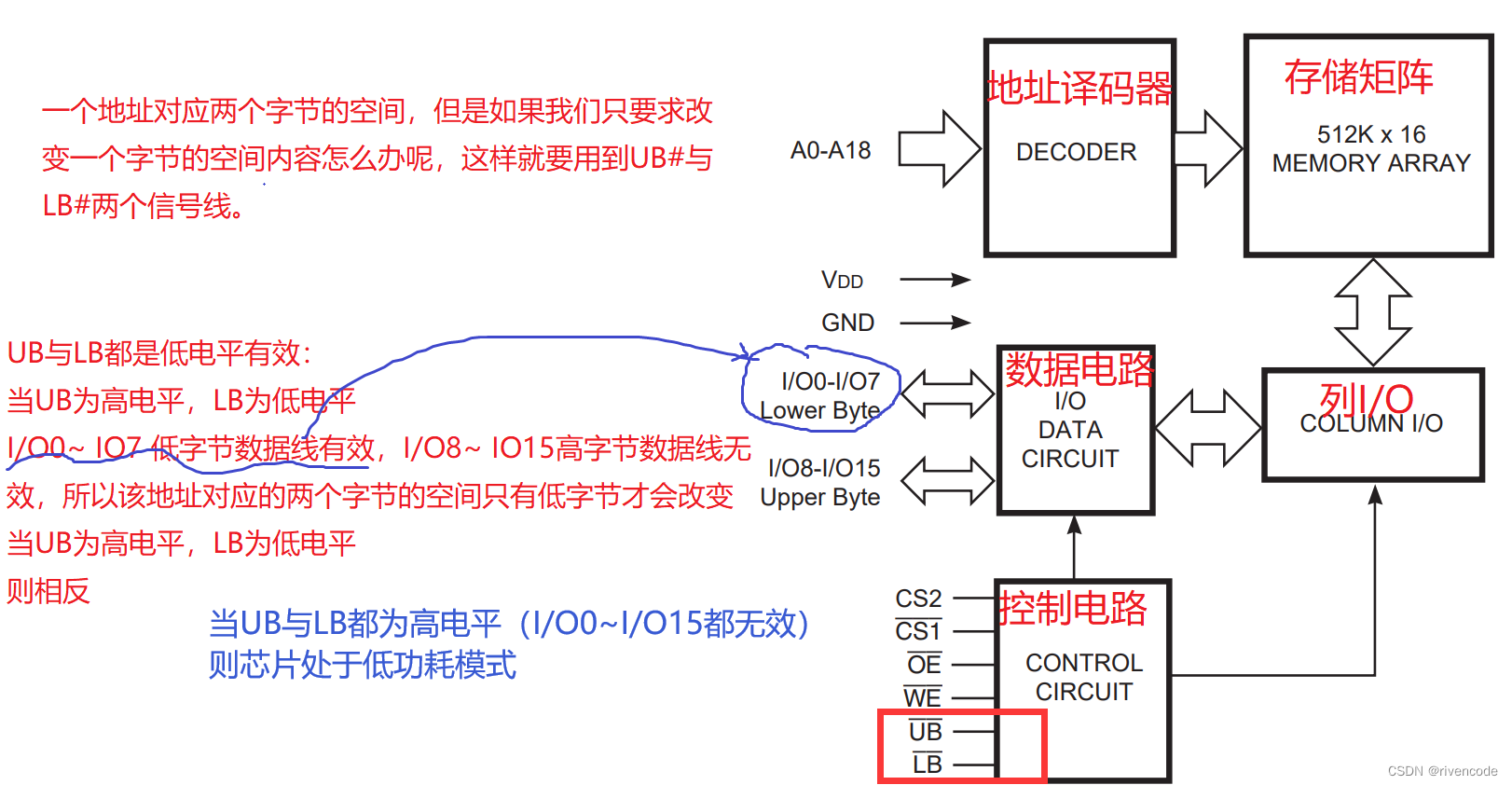

#�����͵�ƽ��Ч

����ʱ,ʹ�� UB# �� LB# �߿������ݿ���,����,��Ҫ���ʿ���Ϊ 16 λ������ʱ,ʹ���е�ַ��ָ����ַ,Ȼ��� UB# �� LB# �߶�����Ϊ�͵�ƽ,��ô I/O0-I/O15 �߶���Ч,����һ������õ�ַ�� 16 λ���� (���߽��� 16 λ���ݵ��õ�ַ);��Ҫ���ʿ���Ϊ 8 λ������ʱ,ʹ���е�ַ��ָ����ַ,Ȼ��� UB# �� LB# ����һ������Ϊ�͵�ƽ,I/O ���Ӧ����õ�ַ�ĸ� 8 λ�͵� 8 λ����,������DZ���Ϊ���������źš�

STM32��SRAM���ݽ���:ֱ��ͳͳA0~A18�ź�������һ����ַ,Ȼ������ͨ��������I/O0 ~ I/O15������Ҫ��������ݴ洢��SRAM�л�STM32��ȡ����

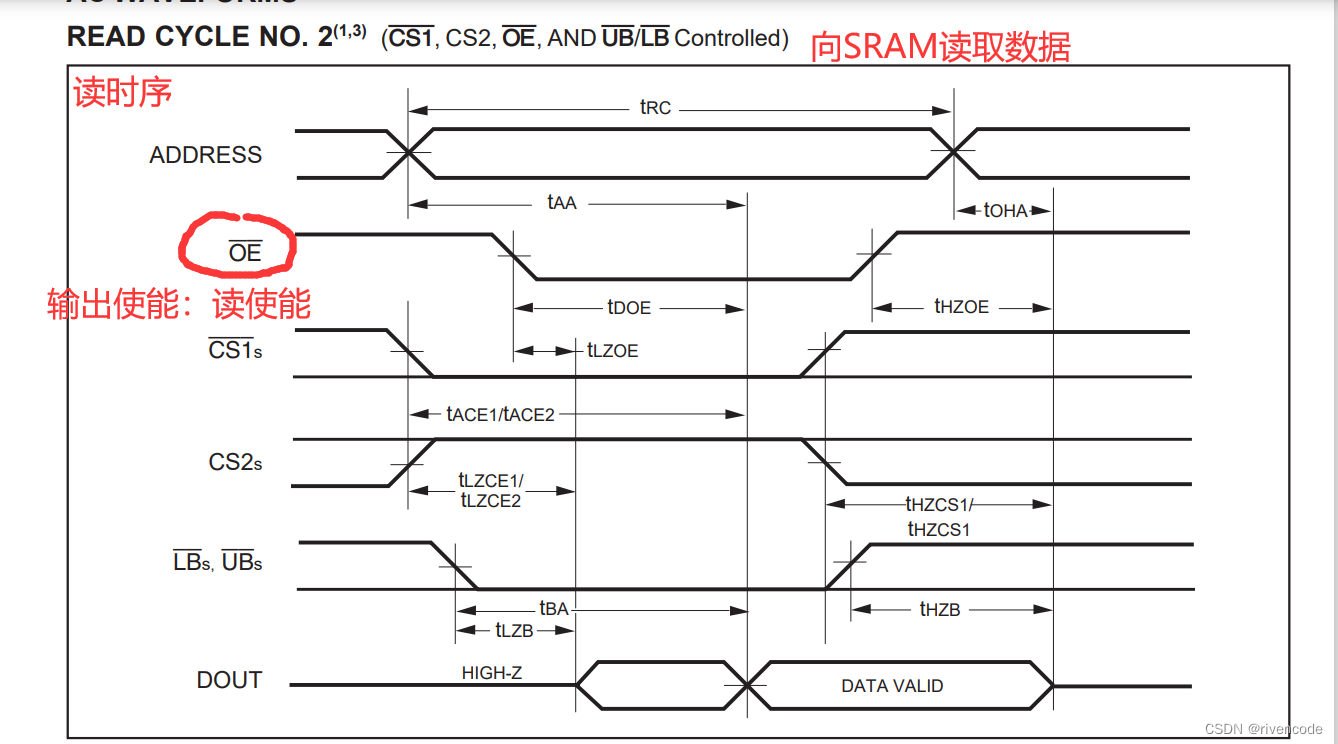

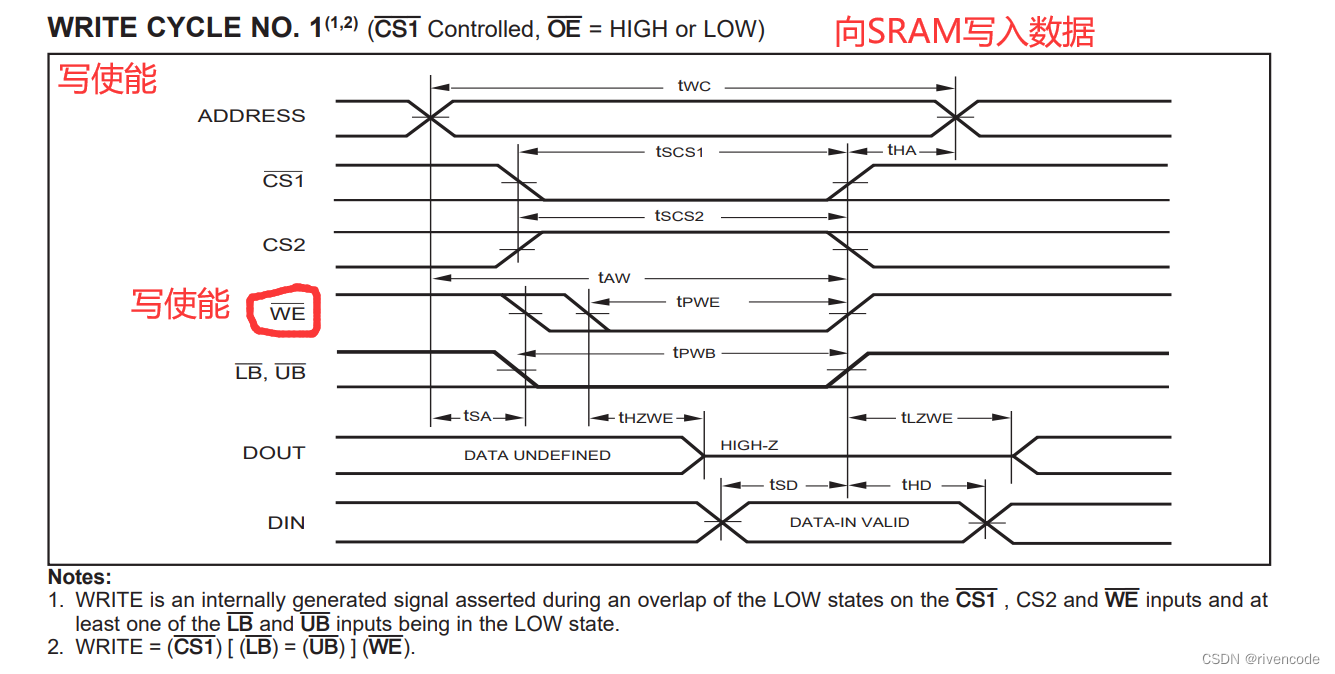

3.SRAM �Ķ�д����

(1) ����ʹ�õ�ַ�ź��߷���Ҫ���ʵĴ洢��Ŀ���ַ,��ַ��Ҫ����������дʱ��

(2) ����Ƭѡ�ź� CS1# �� CS2# ʹ�ܴ洢��оƬ;

(3) ����Ҫ���ж�����,����ƶ�ʹ���ź� OE# ��ʾҪ������,������д���������дʹ���ź�WE# ��ʾҪд����;

(4) ʹ�������ź� LB# �� UB# ָʾҪ����Ŀ���ַ�ĸߡ����ֽڲ���;

(5) ���Ƕ�ȡ����,�洢����ͨ�����������������Ŀ������,����д�����,��Ҫʹ����������洢������Ŀ�����ݡ�

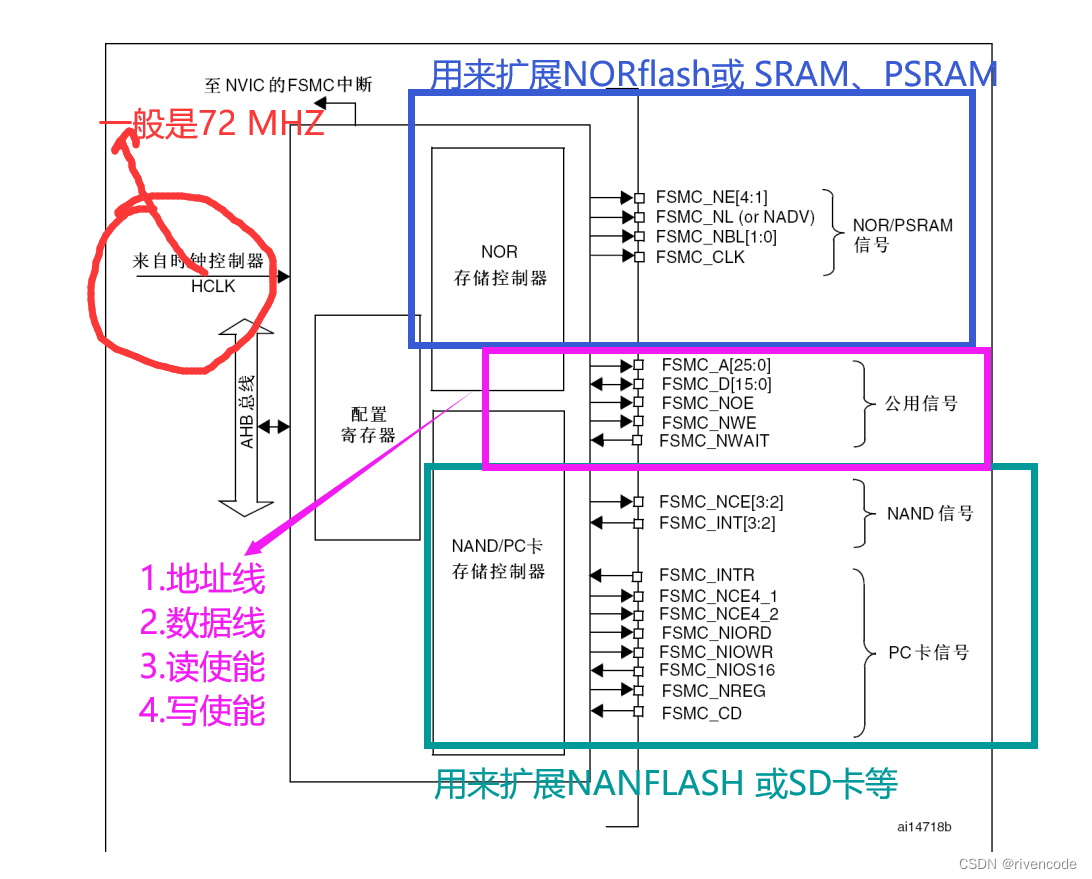

��.FSMC���蹦�ܿ�ͼ

ǰ���N�Ĵ����͵�ƽ��Ч

1.AHB�ӿ�

AHB�ӿ�Ϊ�ڲ�CPU���������߿����豸�����ⲿ��̬�洢���ṩ��ͨ����

AHB������ת�����ⲿ�豸�IJ�������ѡ����ⲿ�洢��������ͨ����16��8λʱ,��AHB�ϵ�32λ���ݻᱻ�ָ��������16��8λ�IJ�����

AHBʱ��(HCLK)��FSMC�IJο�ʱ�ӡ�

һ��IJ�������

����AHB���������ݿ��ȿ�����8λ��16λ��32λ,���ⲿ�豸���ǹ̶������ݿ���,��ʱ��Ҫ����ʵ�����ݴ����һ���ԡ�

���,FSMCִ��������������:

- AHB���������ݿ�����洢�����ݿ�����ͬ:�����ݴ���һ���Ե����⡣

- AHB���������ݿ��ȴ��ڴ洢�������ݿ���:��ʱFSMC��AHB�����ָ�ɼ��������Ľ�С���ݿ��ȵĴ洢������,����Ӧ�ⲿ�豸�����ݿ���(��:������չ��SRAM�����ݿ�����16λ��,�������Ҫд����߶���32λ������,��FSMC������Զ���ȡ��д��2��16λ������)

- AHB���������ݿ���С�ڴ洢�������ݿ���: �����ⲿ�豸������,�첽�����ݴ����п��ܲ�һ�¡�

1.������ֽ�ѡ���ܵĴ洢��(SRAM��ROM��PSRAM��)�����첽����ʱ,FSMCִ�ж�д������ͨ�������ֽ�ͨ��BL[1:0]������ȷ�����ݵġ�(������Ҫ��չ��SRAM16���ݿ��ȶ�Ӧ,������Ҫֻ��дһ���ֽڵ�����ʱ����ֻ��ͨ��UB��LB�����Ʒ��ʸߵ��ֽڵ�Ŀ��)

2.�벻�����ֽ�ѡ���ܵĴ洢��(NOR��16λNAND��)�����첽����ʱ,����Ҫ��16λ��������洢�������ֽڷ���;��Ȼ���ܶԴ洢�������ֽ�ģʽ����(ֻ����16λ�����ݴ���),���:

a. ����������д����(ֻ��д��16λ������,����д��8λ����)

b. ���Խ��ж�����(����������������16λ�洢������,ֻʹ����Ҫ���ֽ�)��

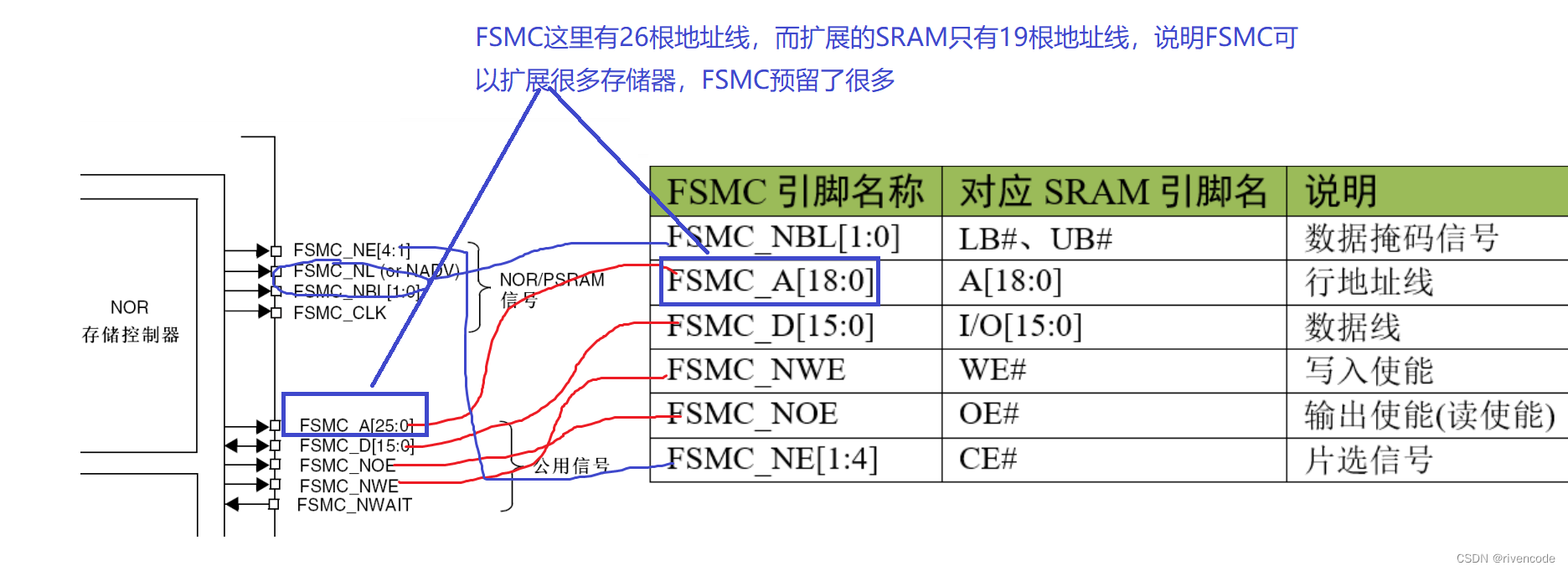

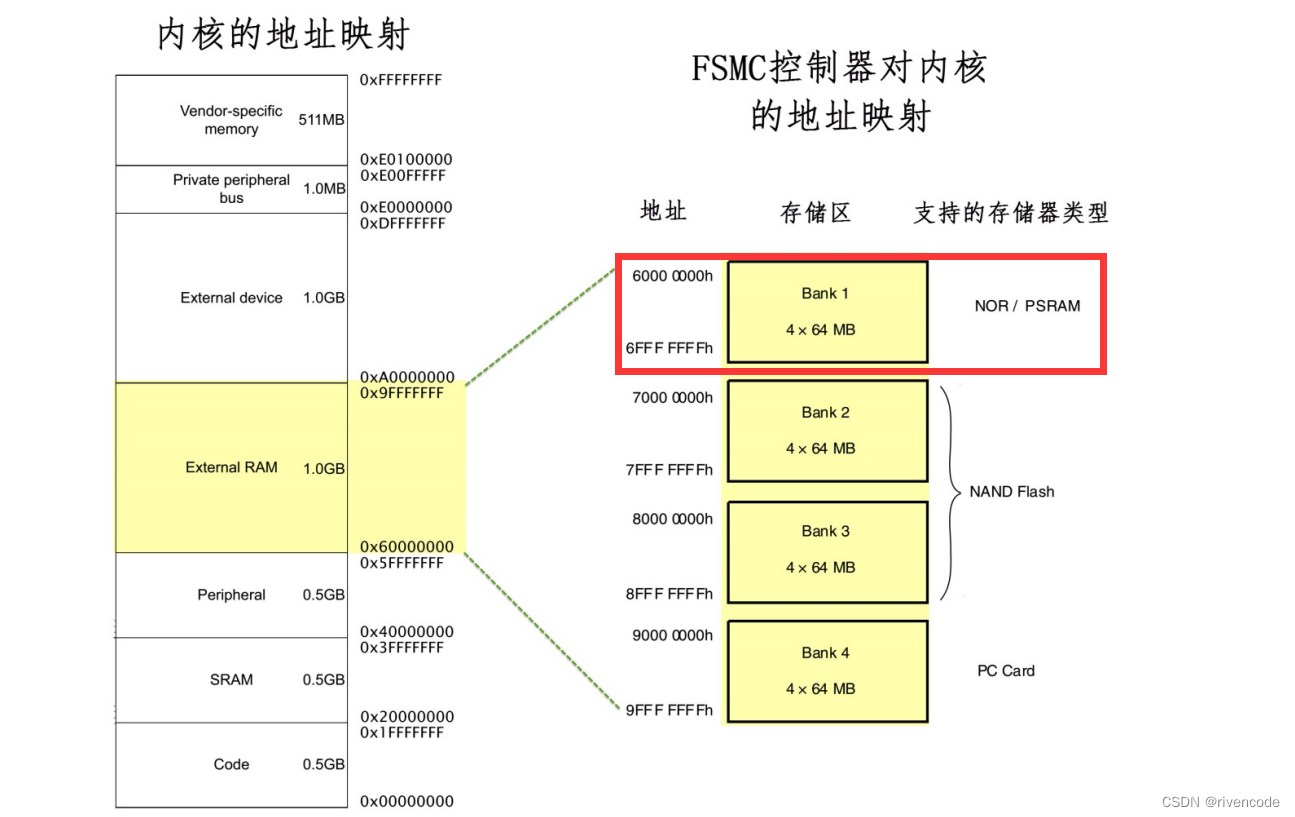

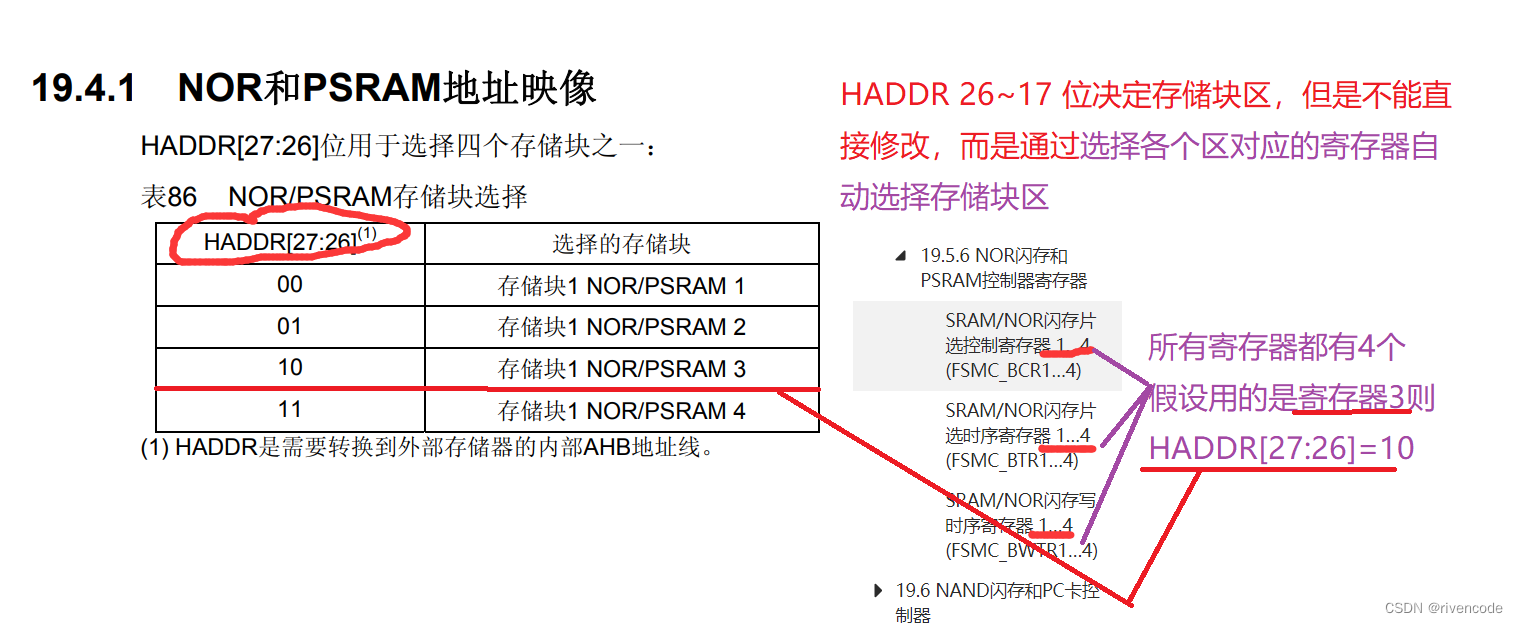

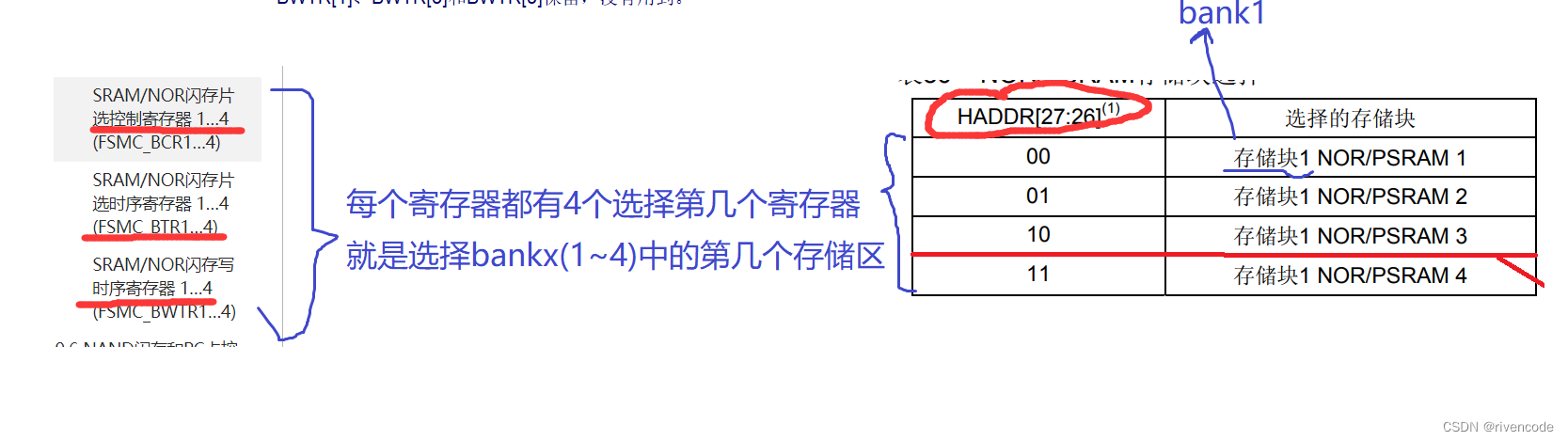

2.FSMC �ĵ�ַӳ��

��FSMC�ĽǶȿ�,�����ⲿ�洢������Ϊ�̶���СΪ256M�ֽڵ��ĸ��洢�顣

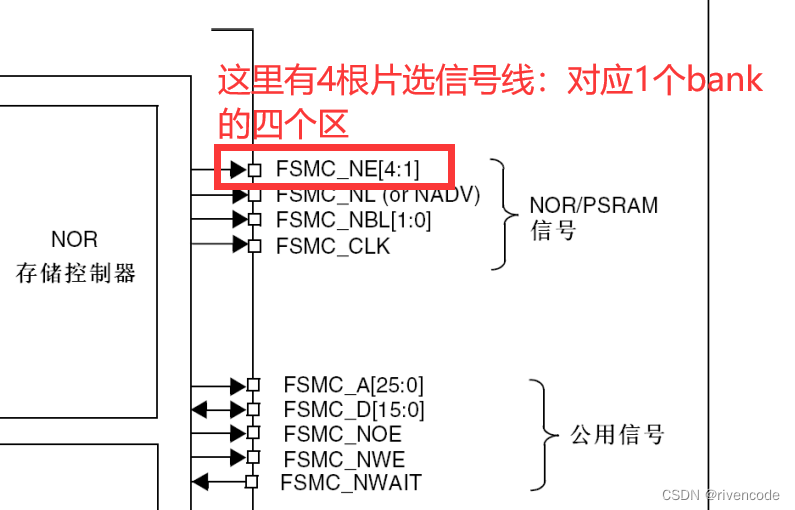

�� �洢��1���ڷ������4��NOR�����PSRAM�洢�豸������洢��������Ϊ4��NOR/PSRAM������4��ר�õ�Ƭѡ��

�� �洢��2��3���ڷ���NAND�����豸,ÿ���洢������һ��NAND���档

�� �洢��4���ڷ���PC���豸

ÿһ���洢���ϵĴ洢�����������û������üĴ����ж���ġ�

ʹ�� FSMC ��Ӵ洢��ʱ,��洢��Ԫ��ӳ�䵽 STM32 ���ڲ�Ѱַ�ռ��;�ڳ�����,����һ��ָ����Щ��ַ��ָ��,Ȼ��Ϳ���ͨ��ָ��ֱ���ĸô洢��Ԫ������,FSMC ������Զ�������ݷ��ʹ���,��д����֮��IJ�������Ҫ������ơ�FSMC�ĵ�ַӳ���ͼ FSMC �ĵ�ַӳ�䡣

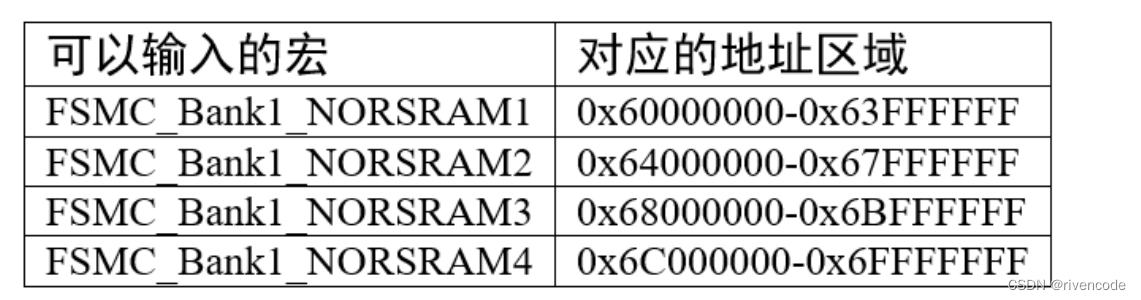

FSMC ������ External RAM �洢����ֳ��� 4 �� Bank ����,�������˵�ַ��Χ�����õĴ洢������,�� NOR �� SRAM �洢��ֻ��ʹ�� Bank1 �ĵ�ַ��

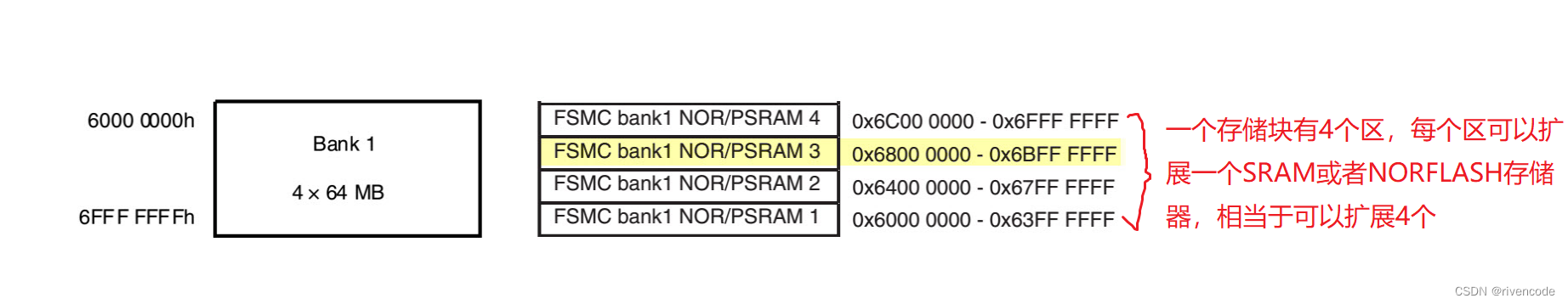

���Խ��߽ӵ��ĸ�Ƭѡ��,��д����ʱ�������������Ӧ�ĵ�ַ,��������SRAMоƬƬѡ�ӵ�����3,������ĵ�ַ��ΧΪ:0x6800 0000 �C 0x6BFF FFFF��

��ÿ�� Bank ���ڲ��ֳַ��� 4 ��С��,ÿ��С������Ӧ�Ŀ���������������Ƭѡ�ź�,FSMC_NE[4:1] �ź��߿�����ѡ�� BANK1 �ڲ��� 4 С���ַ����,��ͼ Bank1 �ڲ���С���ַ���� ,�� STM32 ���� 0x68000000-0x6BFFFFFF��ַ�ռ�ʱ,����ʵ� Bank1 �ĵ� 3 С������,��Ӧ�� FSMC_NE3 �ź�����������ź�(�ź����Զ�����(SRAMƬѡ��Ч��ʱ�Ϳ��Դ���������))��

���ѡ��洢������

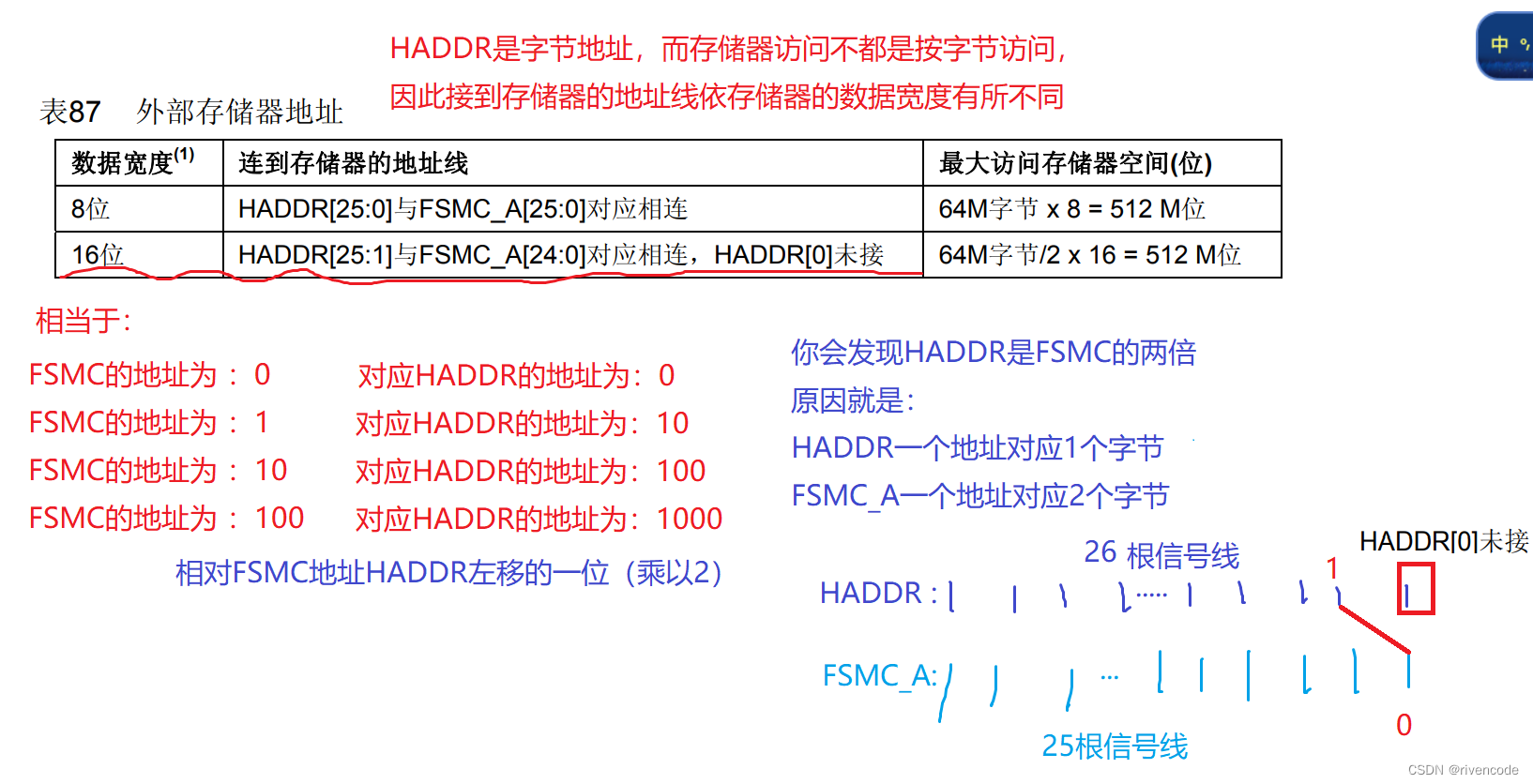

HADDR[25:0]�����ⲿ�洢����ַ��HADDR���ֽڵ�ַ,���洢�����ʲ����ǰ��ֽڷ���,��˽ӵ��洢���ĵ�ַ�����洢�������ݿ���������ͬ,���±�:

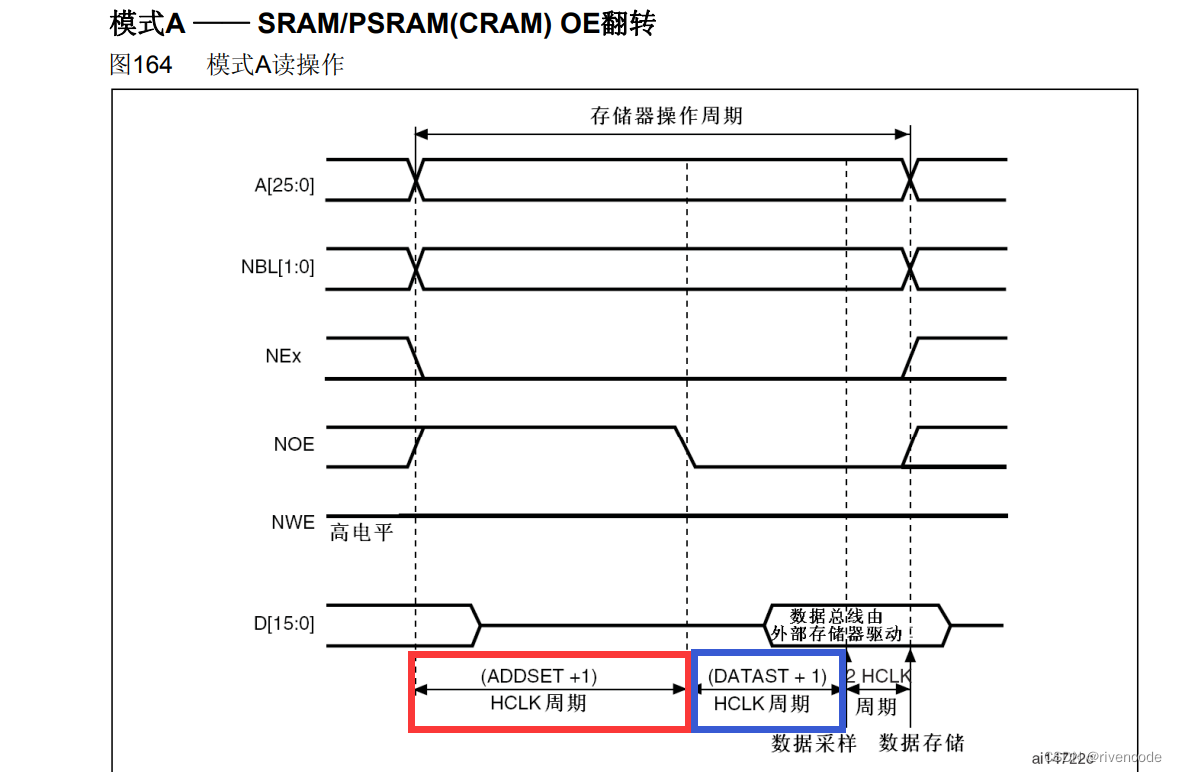

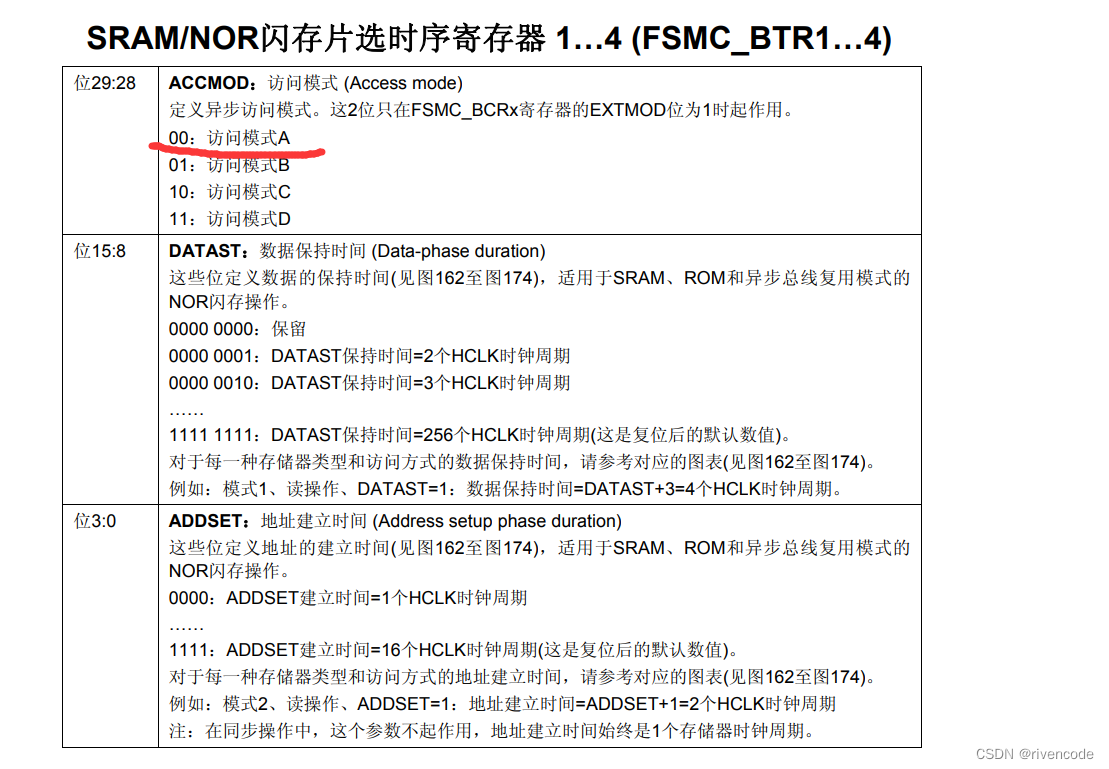

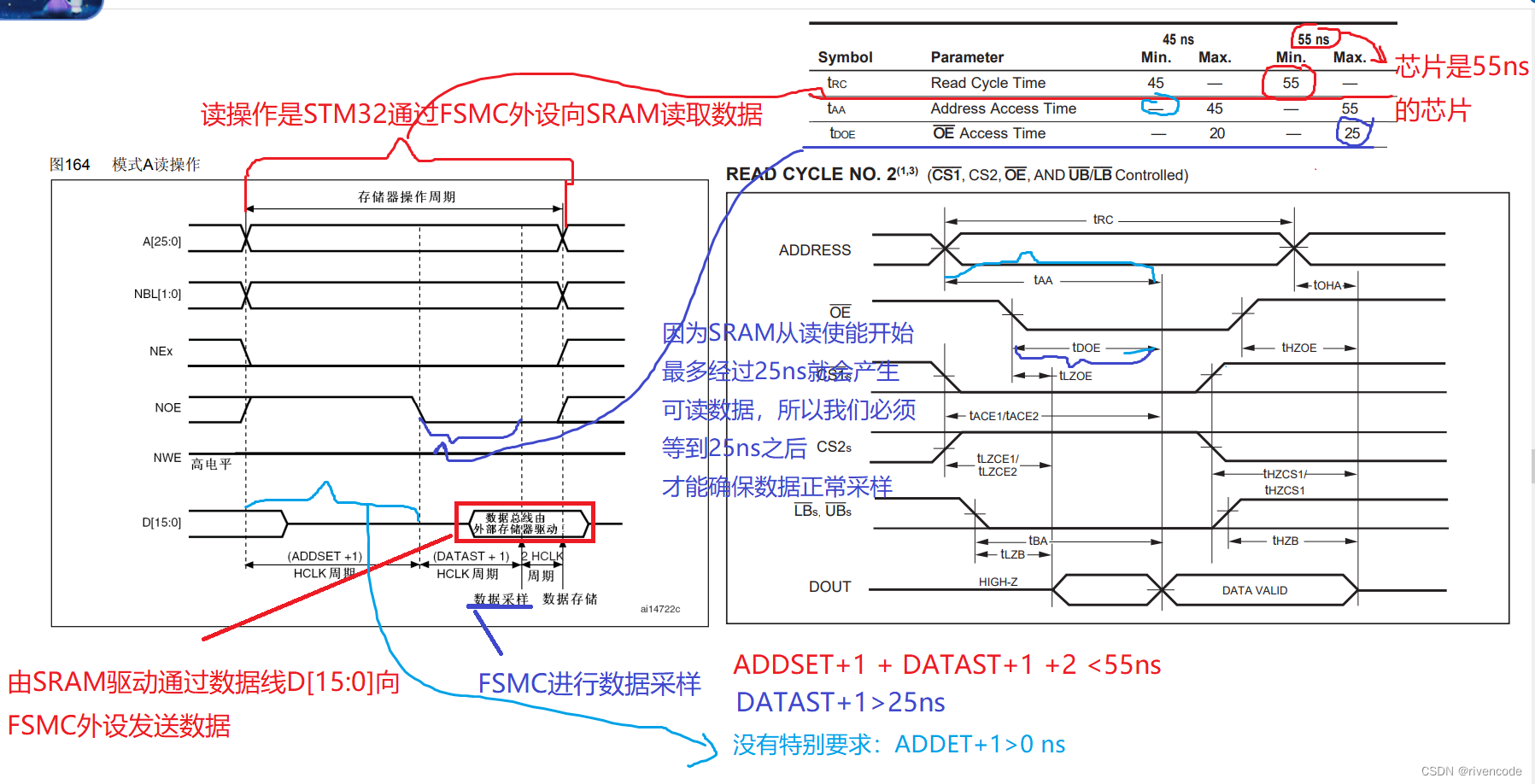

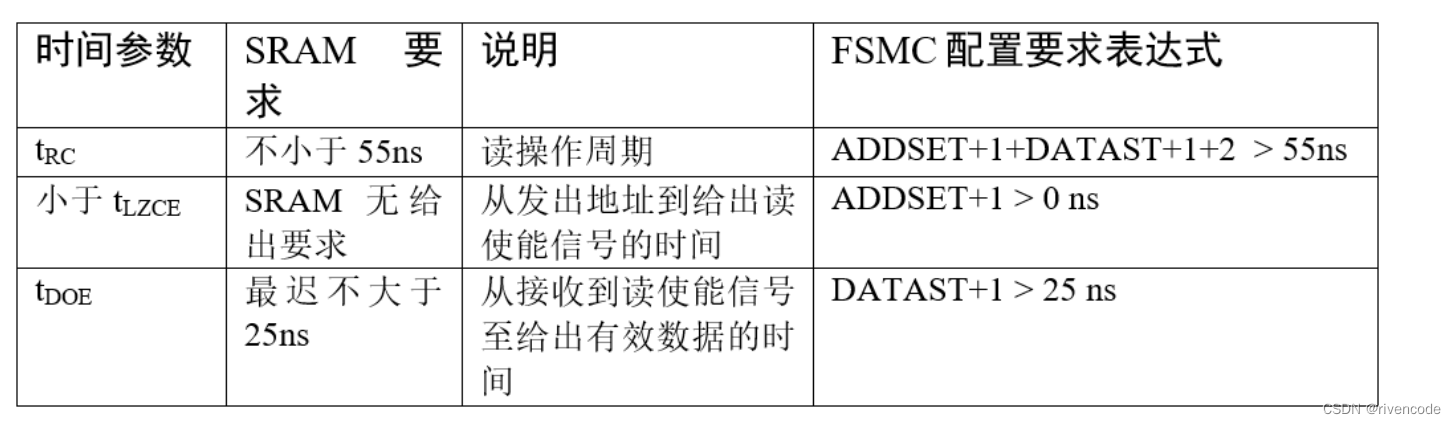

3.FSMC ���� SRAM ��ʱ��

FSMC��SRAM��ȡʱ������

FSMC��ʱ�ӵ���HCLK=72MHZ,��һ��ʱ������Ϊ1/72M=13.8ns

**���� FSMC ���ñ���ʽ������Ҫ���ʱ�䵥λ 1/72 �� (�� 1000/72 ����=13.8ns) ����,

����� ADDSET= 0,DATAST=1 ʱ���ɷ���Ҫ��

��:

tRC=ADDSET+1+DATAST+1+2 =( 0+1+1+1+2 )13.8 = 69 ns > 55 ns

tDOE=DATAST+1 = (1+1)13.8 = 27.7 > 25 ns

����,��ʵ���ܽ����������������ȡ������ݵ�ʱ����������,����ȷ������Ϊ ADDSET=0,DATAST=2

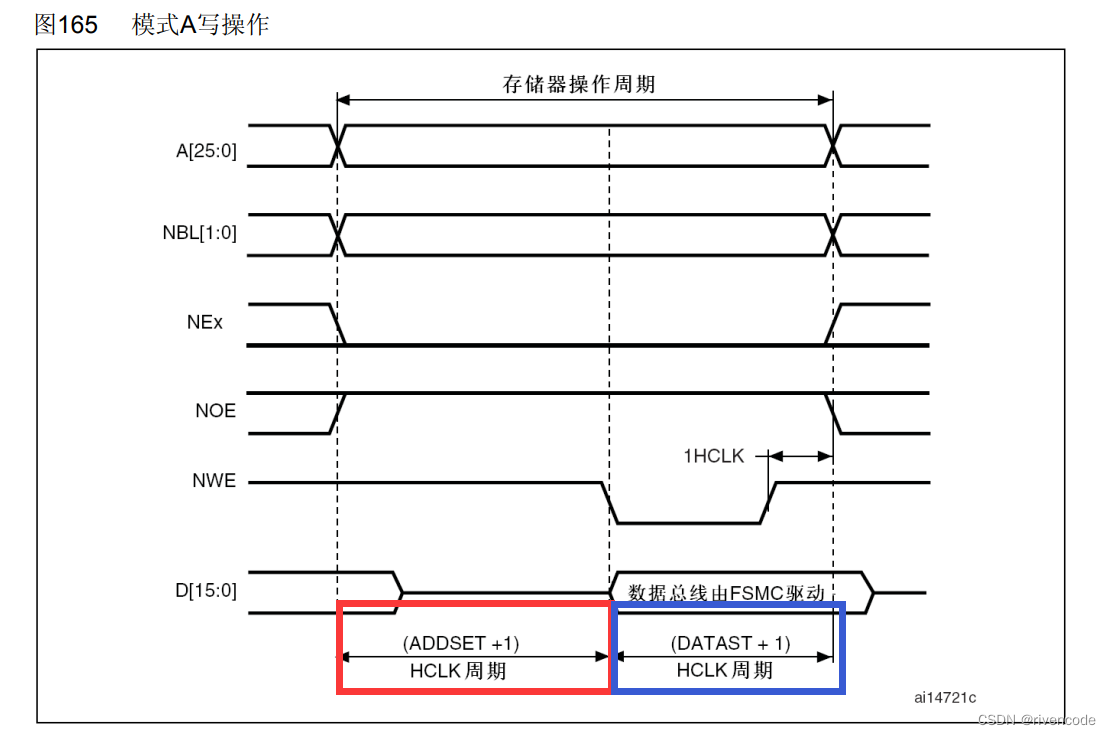

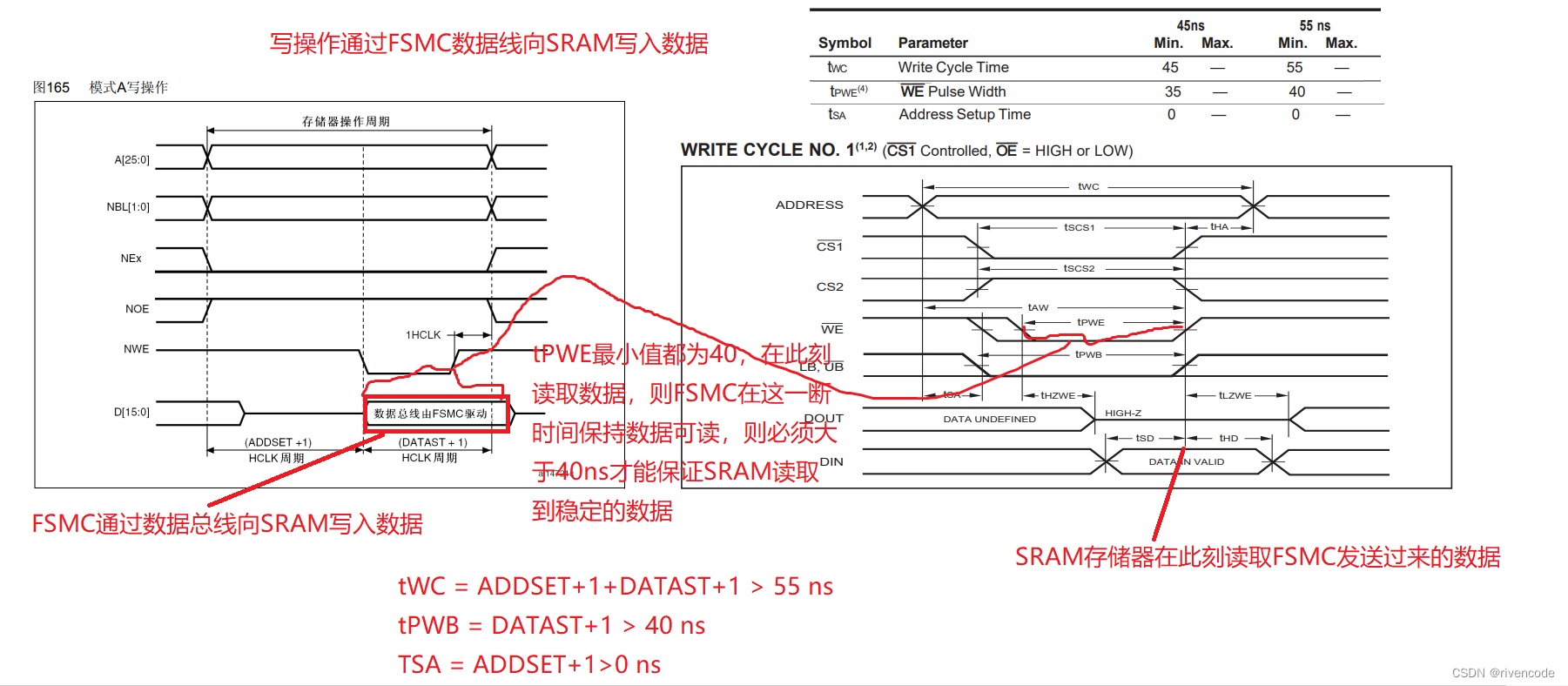

FSMC��SRAMд����ʱ������

��ʵ�����൱�ڷ������ݷ�������ʱ����ȷ�����ݽ��շ��ܽ��յ����ݡ�

**���� FSMC ���ñ���ʽ������Ҫ���ʱ�䵥λ 1/72 �� (��13.8ns) ����

�����

ADDSET= 0,DATAST=2 ʱ���ɷ���Ҫ����:

tWC = ADDSET+1+DATAST+1 =( 0+1+2+1 )13.8 = 55.2 ns > 55 ns

tPWB = DATAST+1 = (2+1) 13.8 = 41.4 > 40 ns

��.��ʼ���ṹ��

1.SRAM ʱ��ṹ��

����ס�IJ����õ���,������Ա�������Բ���

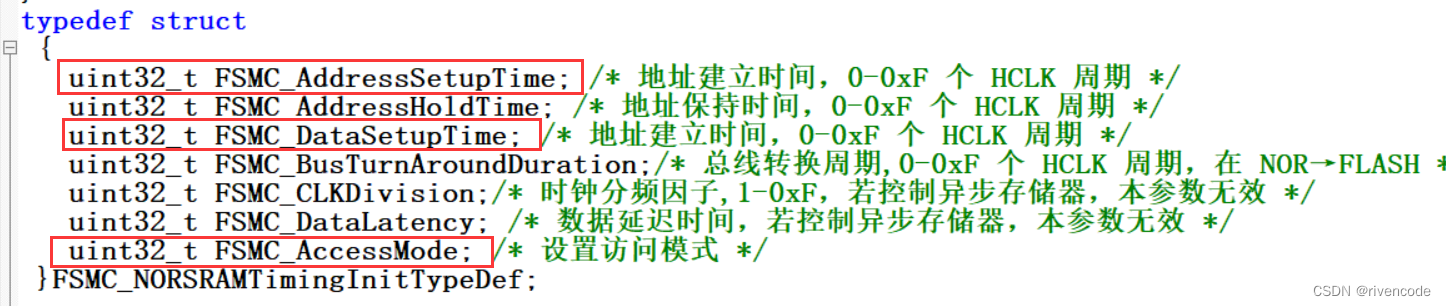

����ṹ���Ա����Ķ��� SRAM ��дʱ���еĸ���ʱ�����,��Щ��Ա�ĵIJ�������FSMC_BRT �� FSMC_BWTR �Ĵ������ö�Ӧ,������Ա��������:

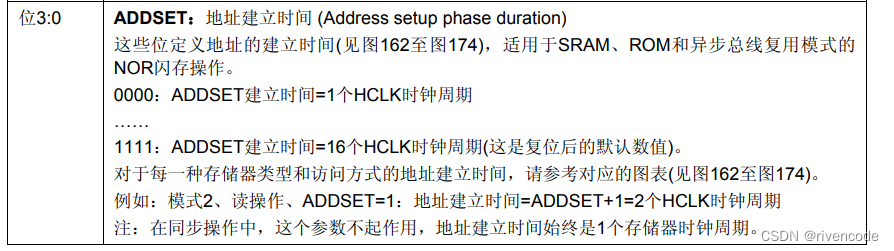

(1) FSMC_AddressSetupTime

����Ա���õ�ַ����ʱ��,�� FSMC ��дʱ��ͼ FSMC ģʽ A �Ķ�ʱ�� �е� ADDSETֵ,�����Ա�����Ϊ 0-0xF �� HCLK ������,�� STM32 �����Ĭ������,HCLK ��ʱ��Ƶ��Ϊ 72MHz,��һ�� HCLK ����Ϊ 13.8ns��

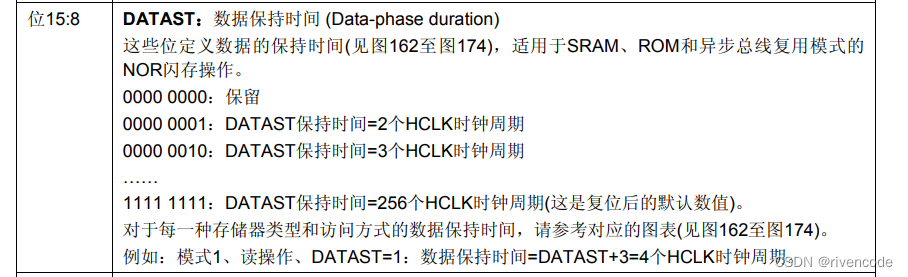

(2) FSMC_DataSetupTime

����Ա�������ݽ���ʱ��,�� FSMC ��дʱ��ͼ FSMC ģʽ A ��дʱ�� �е� DATASTֵ,�����Ա�����Ϊ 0-0xF �� HCLK ��������

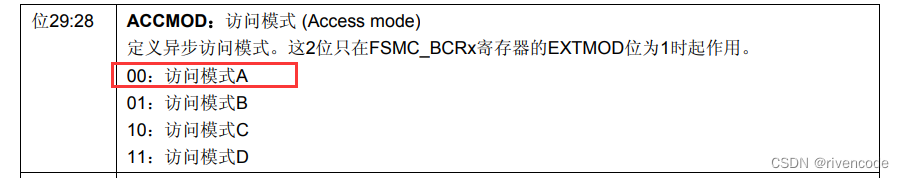

(3) FSMC_AccessMode

����Ա���ô洢������ģʽ,��ͬ��ģʽ�� FSMC ���ʴ洢����ַʱ���������ʱ��һ��,��ѡ FSMC_AccessMode_A/B/C/D ģʽ��һ����˵���� SRAM ʱʹ�� A ģʽ��

����ij�Ա����û���õ�

(4) FSMC_AddressHoldTime

����Ա���õ�ַ����ʱ��,�����Ա�����Ϊ 0-0xF �� HCLK ��������

(5) FSMC_BusTurnAroundDuration

����Ա��������ת������,�� NOR FLASH �洢����,��ַ���������߿��Է�ʱ����,����ת�����ھ���ָ������������״̬���л���Ҫ����ʱ,��ֹ��ͻ�����������洢��ʱ���������Ч,����Ϊ 0 ���ɡ�

(6) FSMC_CLKDivision

����Ա��������ʱ�ӷ�Ƶ,���� HCLK ʱ����Ϊ����,���� FSMC_CLKDivision ��Ƶ������� FSMC_CLK ������ΪͨѶʹ�õ�ͬ��ʱ�ӡ����������첽ͨѶ�Ĵ洢��ʱ

���������Ч,����Ϊ 0 ���ɡ�

(7) FSMC_DataLatency

����Ա�������ݱ���ʱ��,����ʾ�ڶ�ȡ��һ������֮ǰҪ�ȴ���������,������ָͬ��ʱ�ӵ�����,������������ͬ�� NOR FLASH ���͵Ĵ洢��,�����������͵Ĵ洢��ʱ,��������Ч��

��� FSMC_NORSRAMTimingInitTypeDef ʱ��ṹ�����õ���ʱ����,ָ��ýṹ���ָ���������Ϊ��һ�ڵ� FSMCSRAM ��ʼ���ṹ���һ����Ա��

�Խṹ��ָ�벻�����ο�-�����ṹ����⡷

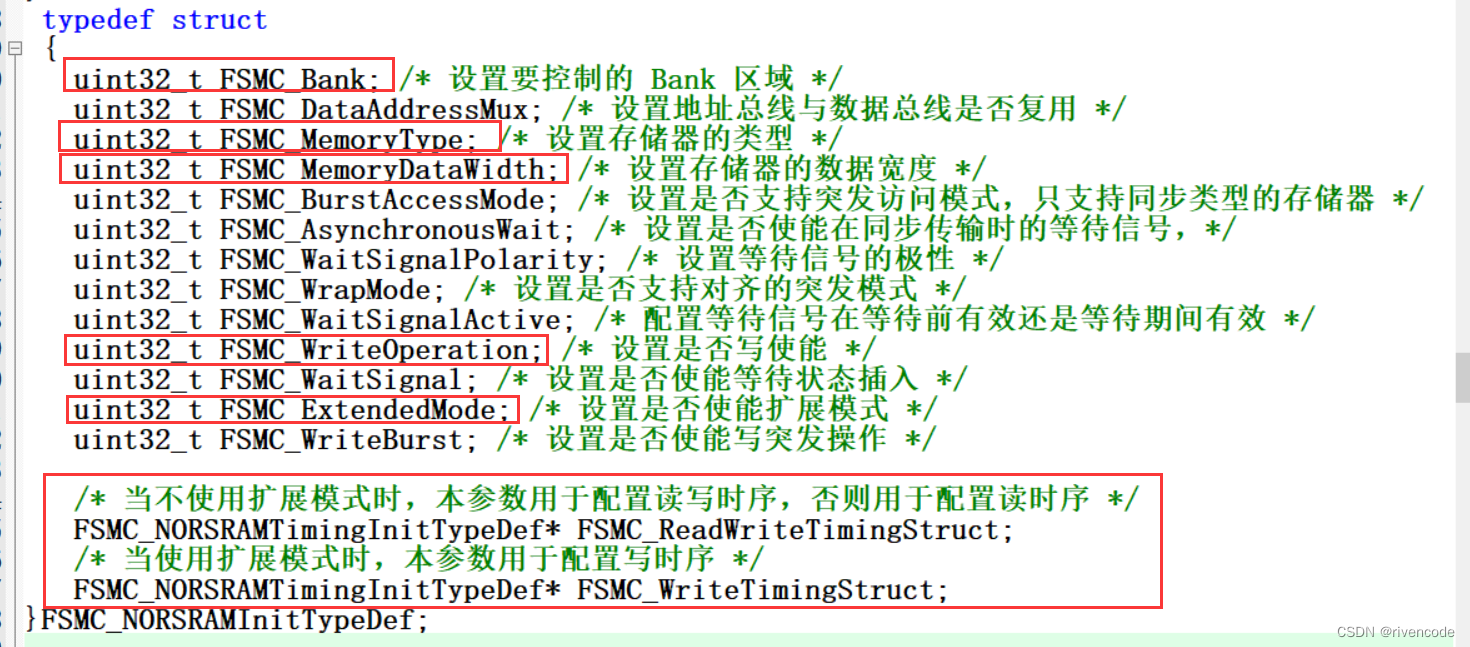

2.SRAM ��ʼ���ṹ��

����ס�IJ����õ���,������Ա�������Բ���

(1) FSMC_Bank

����Ա����ѡ�� FSMC ӳ��Ĵ洢����,���Ŀ�ѡ�����Լ���Ӧ���ں˵�ַӳ�䷶,��ʵ����ѡ���Ӧ�ļĴ�����

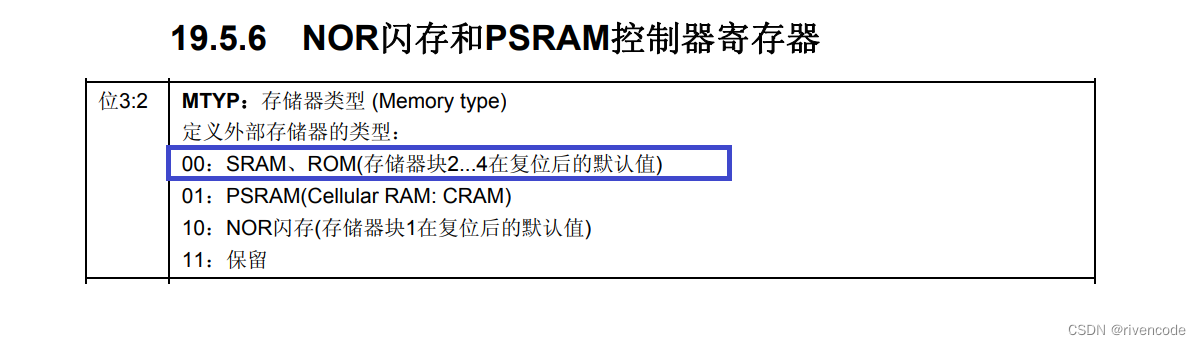

(2) FSMC_MemoryType

����Ա��������Ҫ���ƵĴ洢������,��֧�ֿ��ƵĴ洢������Ϊ SRAM��PSRAM�Լ� NOR FLASH(FSMC_MemoryType_SRAM/PSRAM/NOR)��

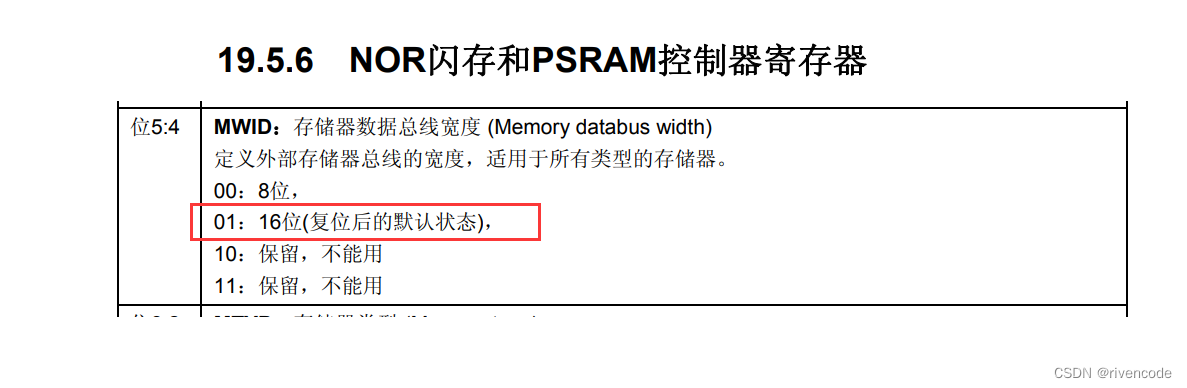

(3) FSMC_MemoryDataWidth

�� �� Ա �� �� �� �� Ҫ �� �� �� �� �� �� �� �� �� ��

��, �� ѡ �� �� �� �� 8 �� 16 λ(FSMC_MemoryDataWidth_8b /16b)��

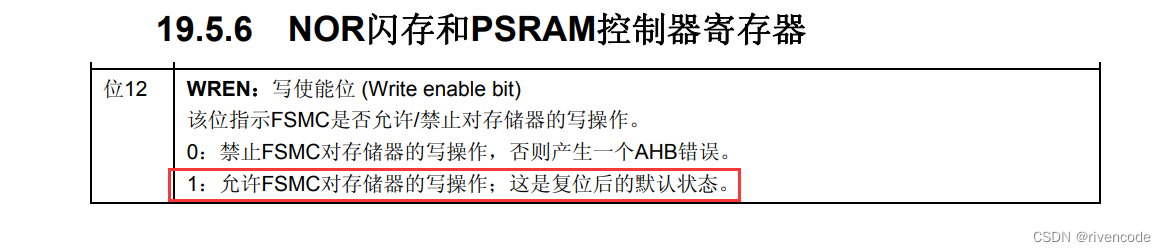

(4) FSMC_WriteOperation

�����Ա���������Ƿ�дʹ�� (FSMC_WriteOperation_ Enable /Disable),��ֹдʹ�ܵĻ� FSMC ֻ�ܴӴ洢���ж�ȡ����,����д�롣

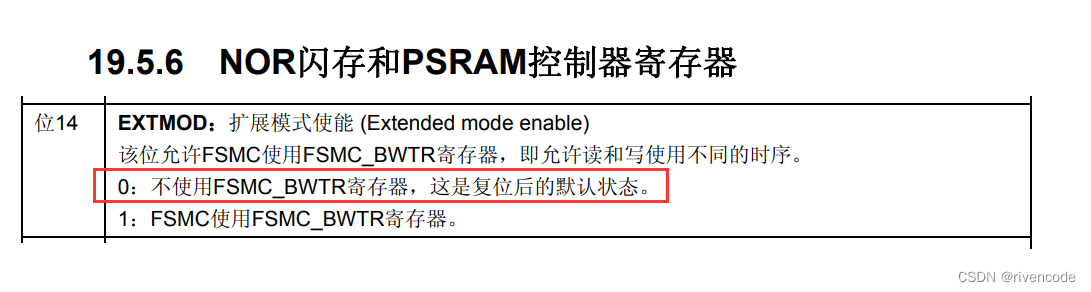

(5) FSMC_ExtendedMode

����Ա���������Ƿ�ʹ����չģʽ (FSMC_ExtendedMode_Enable/Disable),�ڷ���չģʽ��,�Դ洢����д��ʱ��ֻʹ�� FSMC_BCR �Ĵ����е�����,�������FSMC_ReadWriteTimingStruct �ṹ���Ա;����չģʽ��,�Դ洢���Ķ�дʱ����Էֿ�����,��ʱ��ʹ�� FSMC_BCR �Ĵ���,дʱ��ʹ�� FSMC_BWTR �Ĵ���������,������� FSMC_WriteTimingStruct �ṹ�塣

(6) FSMC_ReadWriteTimingStruct

�� �� Ա �� һ ���ṹ��ָ�����, �� ֵ ʱ ʹ �� �� һ С �� �� �� �� �� ʱ �� �� �� ��FSMC_NORSRAMInitTypeDef ����,����ʹ����չģʽʱ,��дʱ��ʹ�ñ���Ա�IJ������á�(���ṹ������ĵ�ַ��ֵ�������Ա�ͺ���)

(7) FSMC_WriteTimingStruct

ͬ����,����ԱҲ��һ��ʱ��ṹ���ָ��,ֻ�е�ʹ����չģʽʱ,�����ò���Ч,����д����ʹ�õ�ʱ��

����ij�Ա����û���õ�

(8) FSMC_DataAddressMux

����Ա�������õ�ַ���������������Ƿ��� (FSMC_DataAddressMux_Enable /Disable),�ڿ��� NOR FLASH ʱ,���Ե�ַ�������������߿��Է�ʱ����,�Լ���ʹ��STM32 �ź��ߵ�����(9) FSMC_BurstAccessMode

����Ա���������Ƿ�ʹ��ͻ������ģʽ (FSMC_BurstAccessMode_Enable/Disable),ͻ

������ģʽ��ָ����һ����ַ���������ʶ������,��ͻ��ģʽ��ÿ����һ�����ݶ���Ҫ����һ����ַ,���ڿ���ͬ�����͵Ĵ洢��ʱ����ʹ��ͻ��ģʽ��

(10) FSMC_AsynchronousWait

�� �� Ա �� �� �� �� �� �� ʹ �� �� ͬ �� �� �� ʱ ʹ �� �� �� �� �� ��

(FSMC_AsynchronousWait_Enable/Disable), �� �� �� ͬ �� �� �� �� NOR �� PSRAMʱ,�洢������ʹ�� FSMC_NWAIT ����֪ͨ STM32 ��Ҫ�ȴ���

(11) FSMC_WaitSignalPolarity����Ա�������õȴ��źŵ���Ч����,��Ҫ��ȴ�ʱ,ʹ�øߵ�ƽ���ǵ͵�ƽ(FSMC_WaitSignalPolarity_High/Low)��

(12) FSMC_WrapMode

����Ա���������Ƿ�֧�ְѷǶ���� AHB ͻ�������ָ�� 2 �����Բ���

(FSMC_WrapMode_Enable/Disable),�����ý���ͻ��ģʽ����Ч��

(13) FSMC_WaitSignalActive

�� �� Ա �� �� �� �� �� ͻ �� �� �� ģ ʽ ʱ, �� �� �� �� �� �� �� �� ��

״ ̬ ֮ ǰ �� һ �� �� �� �� �� �� Ч �� �� �� �� �� ״ ̬ �� �� �� Ч

(FSMC_WaitSignalActive_BeforeWaitState/DuringWaitState)��

(14) FSMC_WaitSignal

����Ա�������õ��洢������ͻ������ģʽʱ,�Ƿ�����ͨ�� NWAIT �źŲ���ȴ�״̬ (FSMC_WaitSignal_Enable/Disable)��

2.����Դ�����

void FSMC_SRAM_Init(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;

FSMC_NORSRAMTimingInitTypeDef readWriteTiming;

/*��ʼ��SRAM��ص�GPIO*/

SRAM_GPIO_Config();

/*ʹ��FSMC����ʱ��*/

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC,ENABLE);

/*-----------------------SRAM ʱ��ṹ��-----------------------*/

//��ַ����ʱ��(ADDSET)Ϊ1��HCLK 1/72M=14ns

readWriteTiming.FSMC_AddressSetupTime = 0x00;

//���ݱ���ʱ��(DATAST)+ 1��HCLK = 3/72M=42ns(��EM��SRAMоƬ)

readWriteTiming.FSMC_DataSetupTime = 0x02;

//ѡ��ƥ��SRAM��ģʽ

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A;

/*-----------------------�����Աδ�õ�-----------------------*/

//��ַ����ʱ��(ADDHLD)ģʽAδ�õ�

readWriteTiming.FSMC_AddressHoldTime = 0x00;

//��������ת������,�����ڸ���ģʽ��NOR����

readWriteTiming.FSMC_BusTurnAroundDuration = 0x00;

//����ʱ�ӷ�Ƶ,������ͬ�����͵Ĵ洢��

readWriteTiming.FSMC_CLKDivision = 0x00;

//���ݱ���ʱ��,������ͬ���͵�NOR

readWriteTiming.FSMC_DataLatency = 0x00;

/*-----------------------SRAM ��ʼ���ṹ��-----------------------*/

// ѡ��FSMCӳ��Ĵ洢����: Bank1 sram3

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM3;

//����Ҫ���ƵĴ洢������:SRAM����

FSMC_NORSRAMInitStructure.FSMC_MemoryType =FSMC_MemoryType_SRAM;

//�洢�����ݿ���:16λ

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

//�洢��дʹ��

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

// ��ʹ����չģʽ,��дʹ����ͬ��ʱ��

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;

//��дʱ������

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming;

//��дͬ��ʱ��,ʹ����չģʽʱ������ò���Ч

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming;

/*-----------------------�����Աδ�õ�-----------------------*/

//���õ�ַ���������������Ƿ���,������NOR

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

//�����Ƿ�ʹ��ͻ������ģʽ,������ͬ�����͵Ĵ洢��

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode =FSMC_BurstAccessMode_Disable;

//�����Ƿ�ʹ�ܵȴ��ź�,������ͬ�����͵Ĵ洢��

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait=FSMC_AsynchronousWait_Disable;

//���õȴ��źŵ���Ч����,������ͬ�����͵Ĵ洢��

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

//�����Ƿ�֧�ְѷǶ����ͻ������,������ͬ�����͵Ĵ洢��

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

//���õȴ��źŲ����ʱ��,������ͬ�����͵Ĵ洢��

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

//��ʹ�õȴ��ź�

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

//ͻ��д����

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure); //��ʼ��FSMC����

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM3, ENABLE); // ʹ��BANK

}

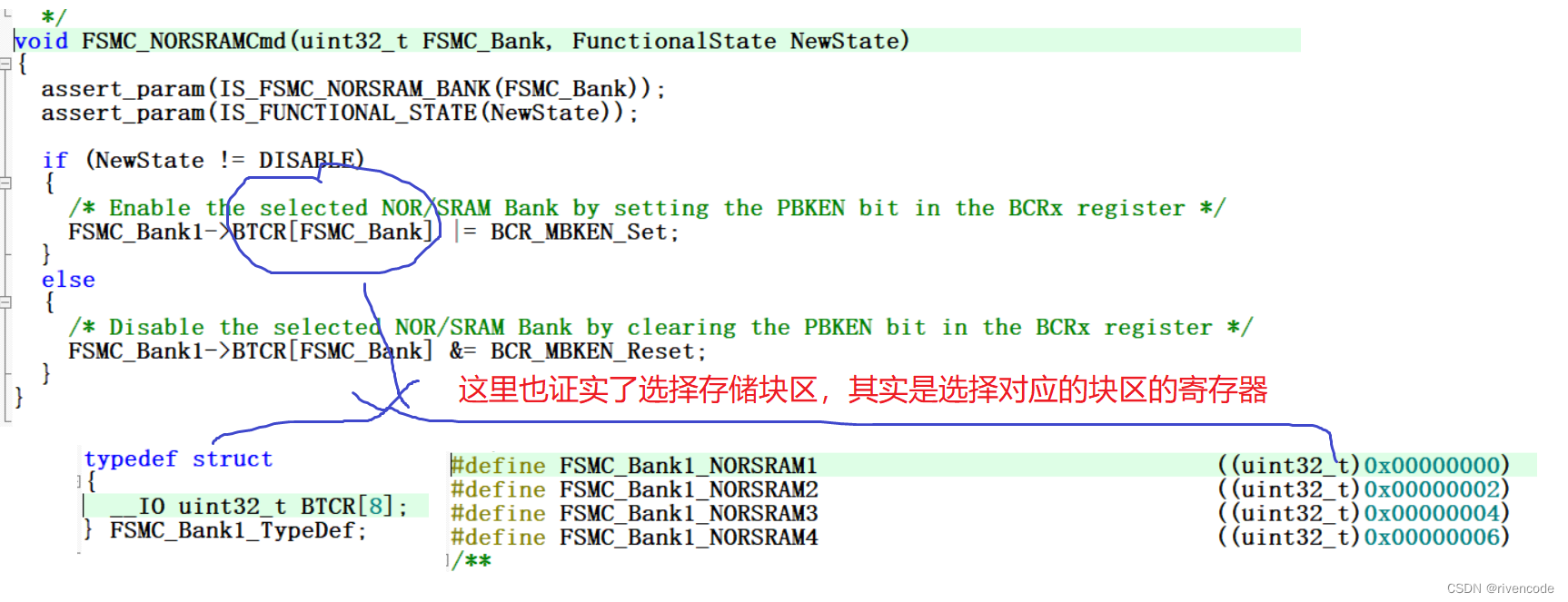

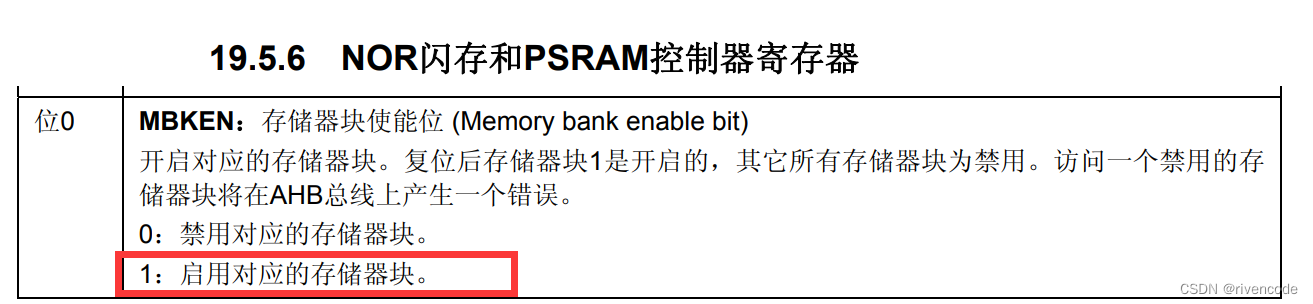

��ST�ٷ����ṩ�ĵļĴ�����������,��û�ж���FSMC_BCRx��FSMC_BTRx��FSMC_BWTRx����������ļĴ���,���ǽ����ǽ�����һЩ��ϡ���������:

FSMC_BCRx��FSMC_BTRx,��ϳ�BTCR[8]�Ĵ�����,���ǵĶ�Ӧ��ϵ����:

BTCR[0]��ӦFSMC_BCR1,BTCR[1]��ӦFSMC_BTR1

BTCR[2]��ӦFSMC_BCR2,BTCR[3]��ӦFSMC_BTR2

BTCR[4]��ӦFSMC_BCR3,BTCR[5]��ӦFSMC_BTR3

BTCR[6]��ӦFSMC_BCR4,BTCR[7]��ӦFSMC_BTR4

FSMC_BWTRx����ϳ�BWTR[7],���ǵĶ�Ӧ��ϵ����:

BWTR[0]��ӦFSMC_BWTR1,BWTR[2]��ӦFSMC_BWTR2,

BWTR[4]��ӦFSMC_BWTR3,BWTR[6]��ӦFSMC_BWTR4,

BWTR[1]��BWTR[3]��BWTR[5]����,û���õ���

����ṹ���ʼ��������ϼĴ���ȥ��Դ��ͺ������