����dz����תFPGA9------������

��������,������

����һ�������TFT,����Ϊ�Ǹ�Сcase,���뵽�������Сʱ������ ,���������ļ�ª������һ��,����,ʲô����?��Ȼ���벻����һ��OK,���Ի�ͷ������,��������ܹ������µ��˲�俴���Լ������õ�ɫ����,����ֻ����ô���ݵ�˲�䡣 ��ʵ���������ڼ�ª�İ�����,��������һ��,�����������ôһЩ,����ɫ�ʳ�����,����ʱ�����Բ��ȶ�,��ͣ������ɫ���ӽ���һ��һ���ġ�һֱ��Ϊ�п�����û���� DE �ź���� HSY/VSYʹ��,���� datasheet ������д�ſ���ʹ�ò��� DE �źŵ� HSY ģʽ�� �����Ӷ���������������������,ʵ�ں����Ρ� ��������������ʱ�������ؽ�ȥ������������ҽ�,��ôһ�����еط���·��,���ǵ�һ��Ӧ,Ҳ���Բ��� VCC ��GND,���ǿ��Կ϶��ġ� ���п�����I/0��ʲô�ط���·��,������һ��ϸ�ĵ���Ѱ,��������� CPLD �Ͻ� LCD_CLK �� l/0 ���ƺ���GND ��·�� ,�������I/0��ԭ���� BJ-EPM ��������һ���� SN74LS4245 �϶���Ϊ DQ�Ľӿ�������,������ӿ���ǰ����,���Ӻ���Ҳû�в��Թ�,ԭ��������GND ֮���·�� ��

Ҳ�ѹ�ԭ��ʱ���ȶ� ,������������֮������,���������ƺ�����,������Ϊʲô��?��Ȼ����ij���ͬ���������DSP��5V��3.3V������չ���߽ӿ�ʱʹ�� 74ALVC164245APW(���ļ�� 4245)�����⡣ ���4245��ֵ��ע��,DlR�Ӹߵ�ƽʱ������һ������ ,�ӵ͵�ƽʱ��������һ������ ���ڸ�CPLD,����4245ʱ���DIRһ������̬,��ô����DO����ʲô״̬?���˱�ij��ҵ�4245,Ҳ����һ����һ���̶���״̬�� ����϶����������4245���õ�LCDʱ���ź����� ,�ò����ۻ��㲻��,����,��!

���ۺϵ��ļĴ���

һ�������εķ�������,������������,һ��������д�����һ�δ���:

// ɫ���źŲ���

reg[23:0] vga_rgb; //ɫ����ʾ�Ĵ���

always @(posedge ck or negedge rst_n)

if(!rst_n) vga_rgb <= 24'd0;

else if (! valid) vga_rgb <= 24'd0;

else vga_rgb <= 24'hff_00_ff;

//r,g,b����Һ������ɫ��ʾ

assign lcd_r = vga_rgb[23:16];

assign lcd_g = vga_rgb[15:8];

assign lcd_b = vga_rgb[7:0];

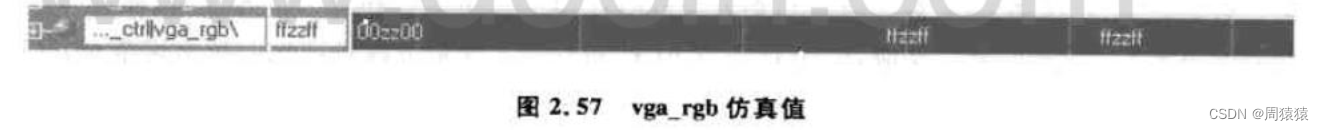

������,��δ������vga_rgb�Ĵ�����λ15~8�Dz����,ʼ��Ϊ0�� �������Ĵ����ڷ���ʱ,vga_Igb��ֵȴ������һЩ����, ��ͼ2.57��ʾ ��

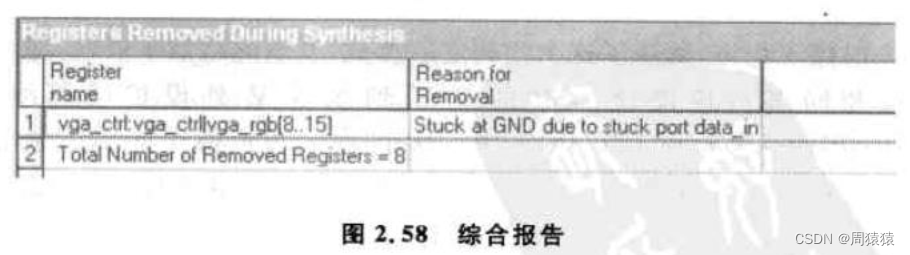

�ڴ����� ,�Ĵ���vga_rgb��λ15~8��Ȼʼ�ձ��ֵ͵�ƽ,���Ƿ�����ȴ�Ǹ���̬�� Ϊʲô��?��ͷ�����ۺϱ���,��ͼ2.58��ʾ:

˵�� vga_rgb[15:8] ���ۺϵ���,����ν removed registers,������� 8 λ�Ĵ��������� ��,����ʱҲ��ֻ���� 8��hzz ������ �� ��������ij�:

// ɫ���źŲ���

reg[23:0] vga_rgb; //ɫ����ʾ�Ĵ���

always @(posedge ck or negedge rst_n)

if(!rst_n) vga_rgb <= 24'd0;

else if (! valid) vga_rgb <= 24'd0;

else vga_rgb <= 24'hff_ff_ff;

//r,g,b����Һ������ɫ��ʾ

assign lcd_r = vga_rgb[23:16];

assign lcd_g = vga_rgb[15:8];

assign lcd_b = vga_rgb[7:0];

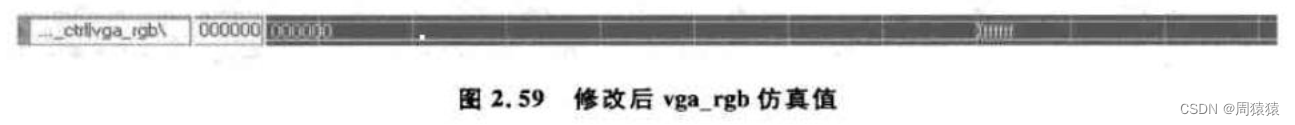

���� vga_rgb ������ 24 ���Ĵ��������ܳ��ֱ仯,Ҳ�Ͳ��ᱻ�ۺϵ�,�Ƿ�����Ƿ�������?��ͼ2.59��ʾ,�õ�Ԥ�ڵĽ���� ���,�ڴ���������Ǵ�ʼ����û�б仯���ź�ֵ�ܿ����á����ܡ����ۺϹ����Ż��ˡ�

Cyclone����ȫ��ʱ�Ӿ�������

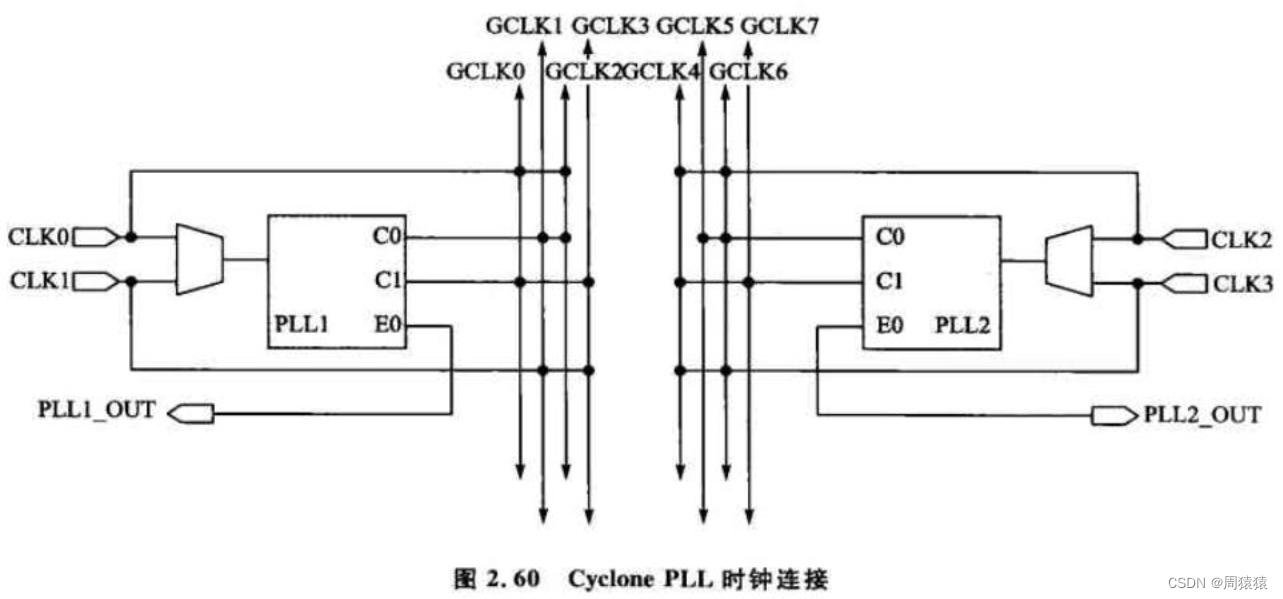

Cyclone ϵ�е������������� 2 ��PLL,ֻ�� EP1C3 �� 1�� PLL�� Cyclone ϵ��������ȫ��ʱ������������������ͼ 2. 60 ��ʾ �� CLKO/CLKl ������Ϊ PLLl ������,CLK2/CLK3 ������Ϊ PLL2(EP1C3 û��)�����ˡ� ��Ȼ��,�������������涨��ʱ�����������������Ϊ PLL ������,��ôֻ�ỻ�� Quartus ll �ı�����Ϣ��

����ͼ 2.60 �п��Կ��� PLL �������� 3 �����:C0,C1,E0�� C0 �� C1һ����Ϊ�ڲ�ʱ��ʹ��,�� E0 ֻ����Ϊ�ⲿ���ʹ�õ�ʱ��,Ҳ����˵��� E0 ����ֱ�����ӵ������ⲿ�������ϡ� ��������� FPGA �ڲ���ʹ�� E0 ��Ϊʱ��;��ôͬ��ֻ�ܻ��� Quartus II �ı�����Ϣ��

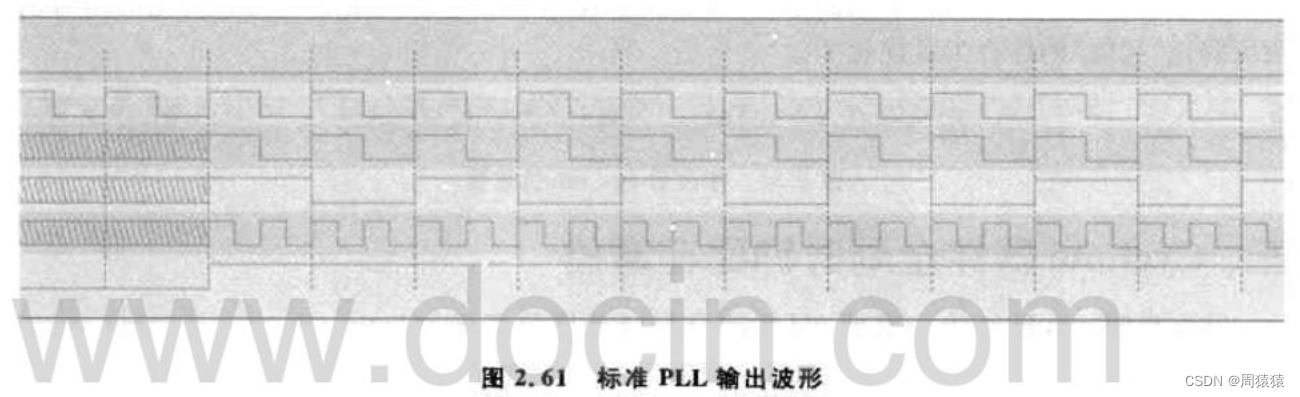

������һ�������һ��,�ȿ�ͼ 2.61:

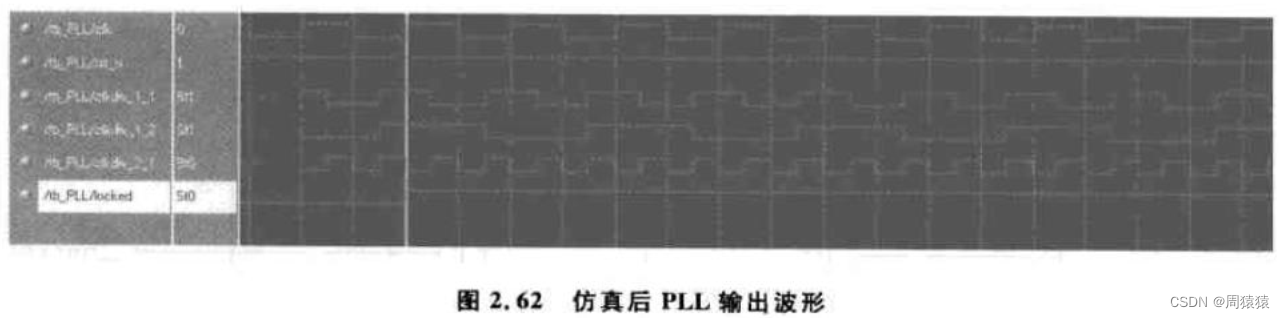

��2����������Ϊ PLL ���˵�ʱ�� clk,�����µ� 3 ������4 ������ 5�����ηֱ��� C0�� C1��E0,�����һ������ν�� lock �ź�(�ߵ�ƽ��ʾ PLL �����Ч) �� Ҳ���ǵ� PLL ��λ��ɻ���ʹ��(����Ҫ��λ����ʹ���ǿ��������� PLL ʱѡ���)���ɸ�ʱ�����ں� PLL ������Ż���Ч,��ô�� lock �����Ժ�� PLL ����������Ҫ�ġ� ͼ 2.61 �����ʱ�Ӻ������ʱ��֮���ƺ�û����λ��,�Ǻ������һ��״̬�� ����ʵ���� PLL ������ʱ�Ӻ������ʱ��֮ �����Ǵ�����λ��ġ����Կ��������IJ���,��ͼ 2.62 ��ʾ :

���,�� PLL ʱ����Դ��ԣ�������,ͳһʹ�� PLL���ʱ����Ϊ�ڲ�����ʱ��,����ʹ�� PLL ��������Ϊ�ڲ�ʱ��,������Ϊ�˷�ֹ�ڲ��ĸ���ʱ��֮����ֲ���������λ��,ͬʱҲ���� PLL ������ʱ�������ڲ����� clock network latency ���Ҫ�� PLL �����ʱ�������ڲ�����clock network lacency ��öࡣ

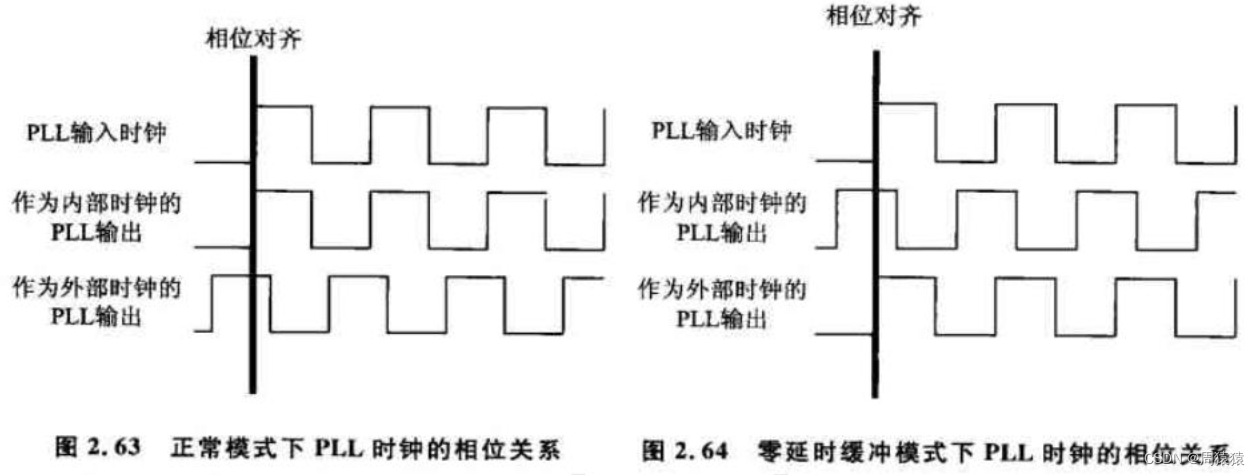

����ǵ���PLL������ʱ��ͬʱ��Ϊ�ڲ�����ʱ��,����Ǹ������ǵ���λ��ϵ����һ��ʱ�ӵĶ���,��ͼ2.63��ͼ2.64��ʾ��

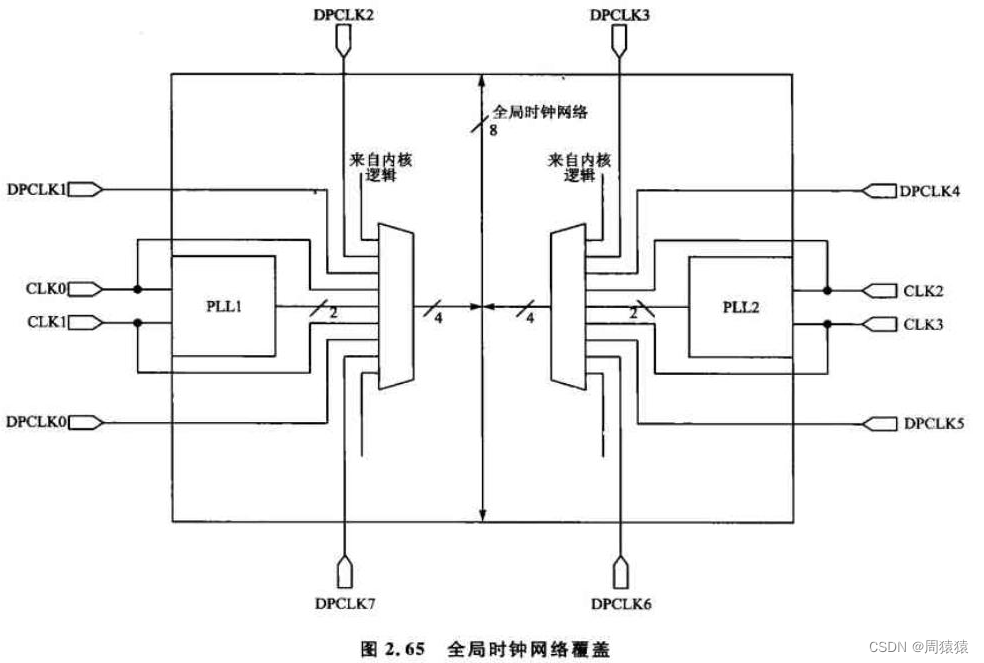

�����ٿ���Cyclone�������ڲ�ȫ��ʱ������ķ���,��ͼ2.65��ʾ,һ��8��ȫ��ʱ������,���Ҹ�4������PLLl�����C0��C1��CLK0/1�Լ�DPCLK0~3(���õ�ʱ������)�����ڲ���������ʹ����ߵ�4��ȫ��ʱ������;PLL2�����C0��C1��CLK2/3�Լ�DPCLK4 ~7(���õ�ʱ������)�����ڲ���������ʹ���ұߵ�4��ȫ��ʱ�����硣PLL�����Ϊ�ⲿʱ�ӵ�E0�Dz���(Ҳû�б�Ҫ)���䵽ȫ��ʱ������ġ�

���������˵,����ʹ��4��ȫ��ʱ��������ź���ʵ����,����֮�е���˭ʹ������ȫ��ʱ��������?�ⶼ�ǿ�������������ƿصġ���Ȼ��,������߲���������ʱ,�ۺϹ�����ݿ���������Ĭ�����������䡣

���ѡ��Setting�C>Fitter Setting�C>More Setting���Aut Global Clock, Quartus ii��ʵ��ʱ������ڲ�����ʵ������Զ�����ȫ��ʱ��,����˵˭ռ��ȫ��ʱ����������˵����(һ��ϵͳ��ʱ�Ӻ�λ�źŻ�ռ��ȫ��ʱ������)����Ȼ,Ҳ������Ϊ�ر���,Ȼ���Լ�������,��ʱ���Ե�Assignment Edit��Global Signals����з���,���ſ��Ե����뱨����鿴Fitter�C>Rescource Section�C>Global�����Ϣ��

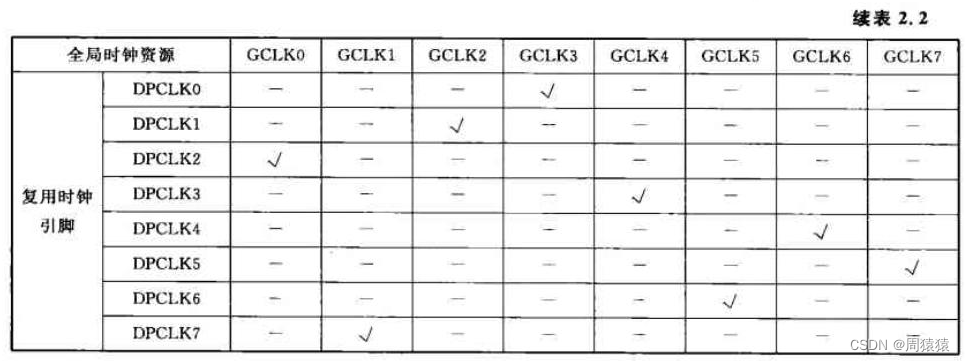

�����һ��ֵ��ע��ĵط�,�������κ�һ��ʱ���źŻ��߸�λ�źŶ����������ռ������һ��ȫ��ʱ�����硣 ��2. 2�г���ȫ��ʱ��������Դ����ϸ�������,����PLLl����� C0 ֻ��ʹ��GCLK1 ����CCLK2,C2 ֻ��ʹ��GCLK0 ����GCLK3��

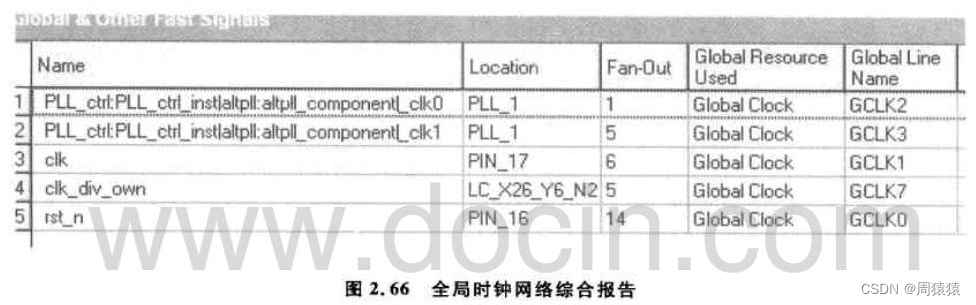

��һ��ʵ��������,��һ����CLK1���������ʱ���ź�clk,���ʱ���ź�clkͬʱ��PLL1������,���ڲ�������PLL1���C0��C1;ϵͳ������һ����λ�ź�rst_n������,�ڲ�������һ��ʱ��clk_divown,��AutoGlobal Clock����������µõ�����ͼ2.66��ʾ��ȫ��ʱ������ķ�������

PLL1��C0���䵽GCLK2,C1���䵽��GCLK3,PLL1������ʱ�Ӽ�clk���䵽��GCLK1,���Ƕ����䵽�˹涨��ȫ��ʱ�������ڡ�����,clk_div_own��rst_n������䡣

���������ȫ��ʱ������������ǵ�ʵ�����Ǵ´������,����һ�����ϵͳ,ʱ�ӽ���,���ȳ����źŲ������,��ô����ȫ��ʱ���źŵ��ƿؾ���Ҫ����С���ˡ�

M4Kʹ����

��ʹ��Cyclone��M4Kʱ������һ������,�������Ҫ����һ�����ݿ���Ϊ224λ�����Ϊ32��Signal-Port ROM��ԭ��������һ��ROMռ�õĴ洢�ռ�Ӧ��Ϊ224λX32= 7 168λ,�����������M4K(4096λX2=8192λ)Ҳ�㹻��,���Ƿ���Mega��Wizard����ʾ����Դ������7��M4K��ͦ���Ƶ�,���Dz鿴��datasheet��

datasheet ������һ�� M4K �������õ� ROM ���� RAM Ϊ 4 KbX1�� 2 KbX2 �� 1 KbX4�� 512 bX 8�� 512 b X 9 ��256 bX16�� 256 b X 18�� 128 bX 32 �� 128 bX 36�� ע������ô˵: Altera Quartus��II�Զ���������Ӷ�� M4K ��������������߸���� RAM/ROM ���á�

����������,Ӧ��˵һ�� M4K ���������� 36 λ��,����ٴ���,��ô�ͻ�ռ��������M4K ��,��������е� 224 λ����ʱ��Ҫ 7 �� M4K �� (7X 36=252 > 224 ,�� 6X36=216 < 224) ��

���ڵ��������ô�λ���������M4K������,���ǿ������Ҫ��������Ʋ��ɼ��!