自动收发串口转RS485设计注意事项

1. 传统的串口转RS485设计

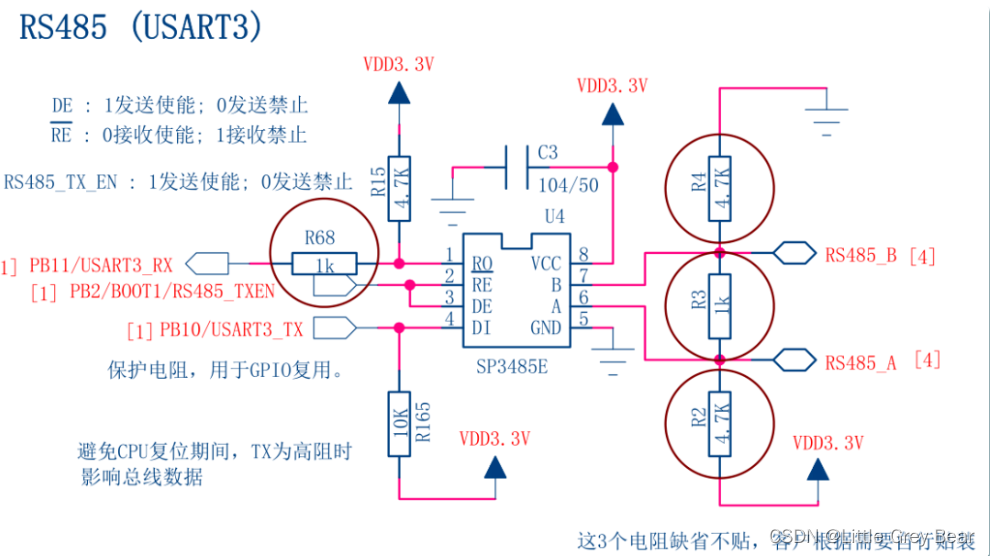

传统的485应用电路如下所示(懒得画了,找个现成的,此图截取自安富莱电子),RS#、DE分别是控制接收和发送,具体来说

RE#: 0接收使能,1接收禁止;

DE: 1发送使能,0发送禁止;

RS#、DE是反向逻辑,因此我们常将RS#、DE连在一起,当MCU要发送数据的时候,就将RS#/DE引脚拉高,当MCU发送完成后,就将引脚拉低,来等待外部485数据。

对于上图的R2和R4,我们一般都是要焊接的,R3一般用于远距离或抗干扰,平时的时候一般会选择120欧姆,或者不焊接。

这种设计的优势:这是485芯片厂商推荐的电路画法,稳定可靠,不需要增加硬件成本,且RS485的驱动能力比较高。

缺点:MCU除了提供RX、TX引脚外,还需要提供一个GPIO引脚,用于控制接收和发送,增加了编程的控制RS#、DE环节考量。

2. 自动收发串口转RS485设计

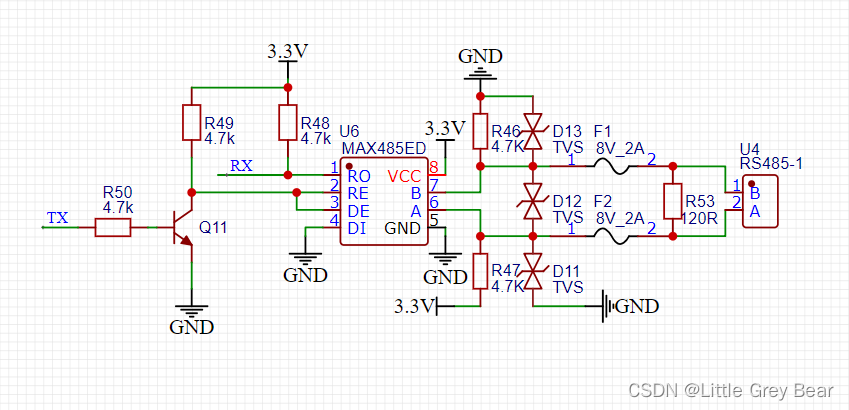

正是因为传统的串口转RS485设计增加了一个GPIO的消耗,因此网上有了一个取巧的设计,设计图如下:

这个图的R46和R47是绝对不可缺的。对于R48,若mcu的RX没有上拉输入功能,那这个电阻也是不可以少,终端120欧电阻一般不添加。

为什么R46和R47是绝对不可缺的,我们先分析一下它的工作原理:

- 当tx为高电平,RS#/DE引脚为低,此时RE#有效,此时485A和485B由于上下拉电阻的作用,485A为高,485B为低,485芯片处于发送高电平状态或者处于接收状态。

- 当tx为低电平,RS#/DE引脚为高,此时DE有效,485芯片处于发送状态,因为DI引脚接地,因此485芯片输出低电平。

现在会发现,当tx为高的时候,485输出电平是由485的AB相的上下拉电阻来完成的,串口的收发恰好可以和485的高低电平对应上,因此这个自动收发串口转RS485设计是可以使用的。

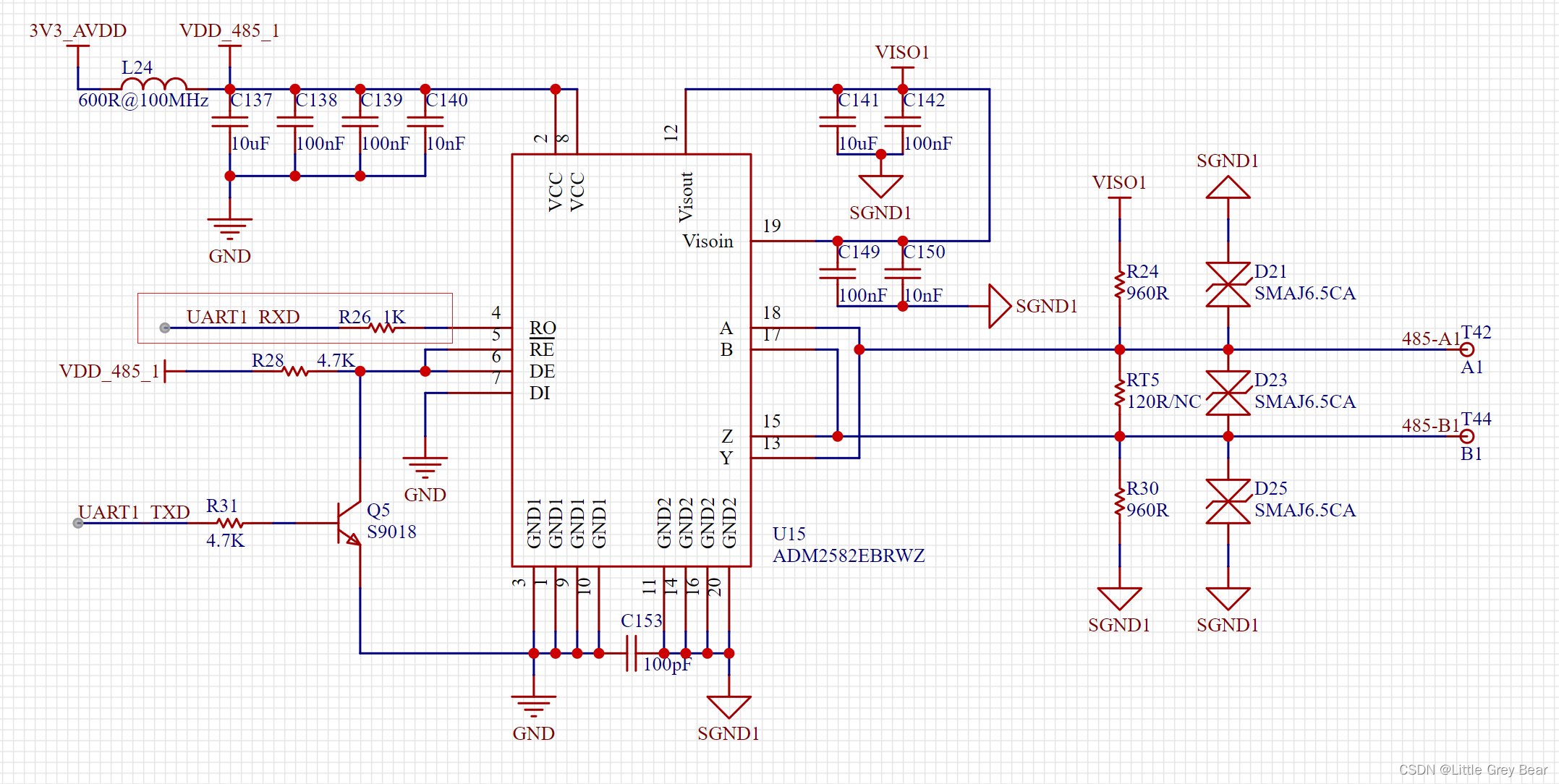

为什么说RX的上拉电阻R48不可缺少,公司曾将设计过这样一个电路,如下:

在描述一下这个电路板,这个rx和tx在pcb上的走线大约10厘米左右,应该对数据的传输也有些影响,但我认为距离不是主要因素,设计才是主要原因。

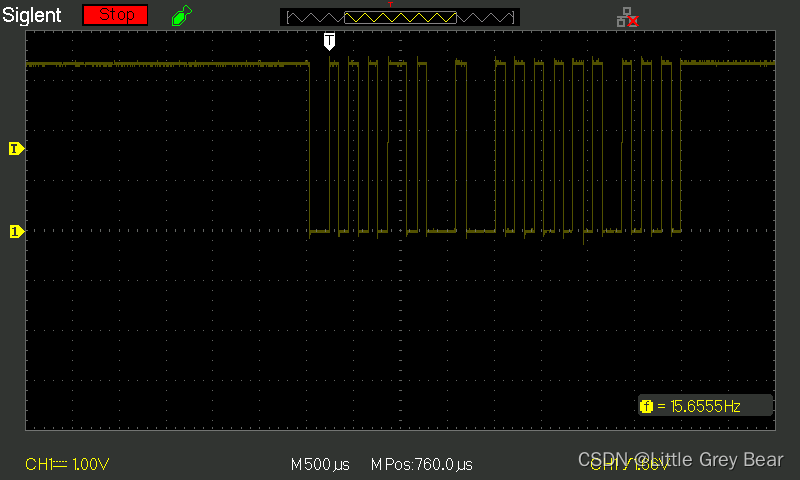

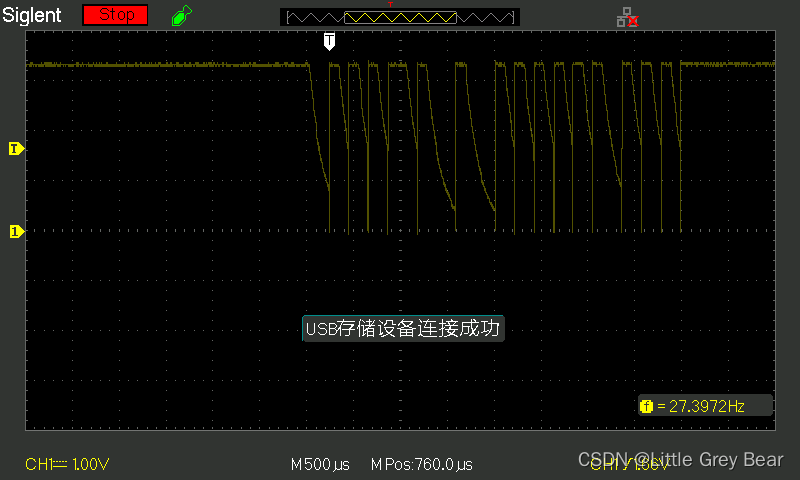

这个uart_rx没有接上拉电阻,当我用示波器分别触碰tx和rx的测试点,然后mcu发送数据,tx线电平如下:

发现很正常,也很规整,完全没有问题,但是当tx发送数据的同时,rx测试点竟然也有了电平变化,如下图:

这将导致我mcu发数据的时候会同时收到数据,有的时候收到的和发送的一致,有的时候是乱码。

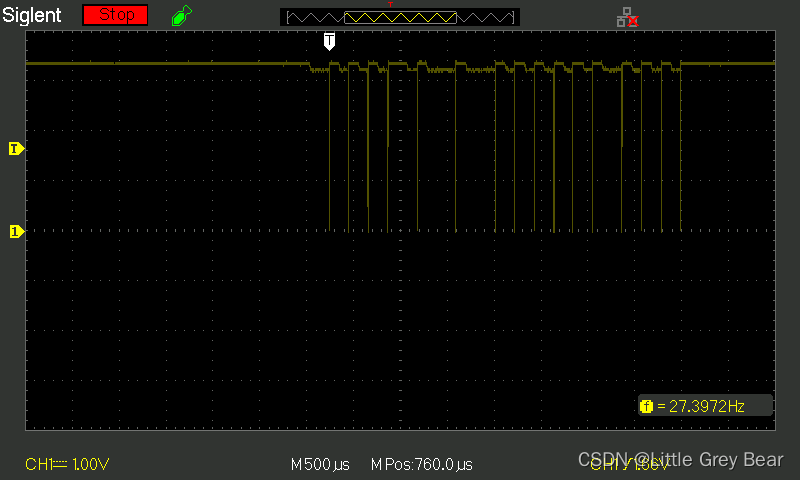

经过分析,我发现了问题,后来我在mcu配置的时候,将RX的GPIO配置成了上拉输入,后再测试,rx测试点波形如下:

发现还是有电平变化,但是很窄,因此也不会被串口误识别有输入,串口输入误判问题得到解决。

因此对于自动收发型电路,rx引脚的上拉电阻很重要,不可缺少,当然若MCU的rx支持上拉,这个电阻也可以忽略。

同时这个也进一步证明了这种自动收发型的RS485设计不适合高速的串口通信,同时抗干扰能力也比传统的差,至于是不是和你的项目需要自己去验证。

3. 自动收发串口转RS485设计优缺点

优点:最主要是节省IO,同时还捎带的降低了程序编写的工作量。

缺点:

-

通信速度慢:

三极管有电容效应,导致关断时间较长,导致RS#/DE从低到高电平变化出现比较大的斜坡.同时485输出高电平,是依靠上下拉来完成的,会导致上升沿不够迅速,因此上下拉的阻值选择也是影响速度的关键。

-

驱动能力弱:

由于当tx为高,485电平是由其上拉电阻完成的,因此弱提高驱动能力,就要减小电阻,由于485芯片驱动能力有限,电阻太小会导致tx为低的时候,485芯片无法将485总线拉低,因此总线上所有上拉电阻的并联值不应该小于375欧。还用当接入120欧的终端电阻的时候,AB两相的电压差由终端电阻和上下拉分压得到,会导致AB两相的电压差变小,因此自动收发串口转RS485设计不太适合添加终端电阻。