6.1.基础功能与新特性

6.1.1.运行模式

? ? ? ? 目前Intel处理器体系结构上可分为IA-32,IA-32e。32位处理器采用IA-32,64位采用IA-32e。

? ? ? ? 1.实模式

? ? ? ? 它为处理器提供Intel 8086处理器的运行环境,并追加了保护模式和系统管理模式的切换扩展。

? ? ? ? 2.保护模式

? ? ? ? 他是32位处理器的主要运行模式,为软件运行提供丰富的功能,严格的安全性检测及向后兼容性。

? ? ? ? 3.系统管理模式

? ? ? ? 是32位处理器的标准功能,提供一种对操作系统透明的机制来执行电源管理和OEM的特殊功能。一旦切换至SMM模式,处理器将进入一个隔离的地址空间运行。

? ? ? ? 4.虚拟8086模式

? ? ? ? 是处理器为保护模式提供的一种准运行模式,允许处理器在保护模式下执行8086软件和多任务环境。

? ? ? ? 5.IA-32e模式

? ? ? ? 是64位处理器的主要运行模式,共包含两种子模式:兼容模式和64位模式。64位模式为处理器提供64位的线性地址空间并支持超过64GB的物理地址寻址,而兼容模式可使大部分保护模式的应用程序无需修改运行于64位处理器中。

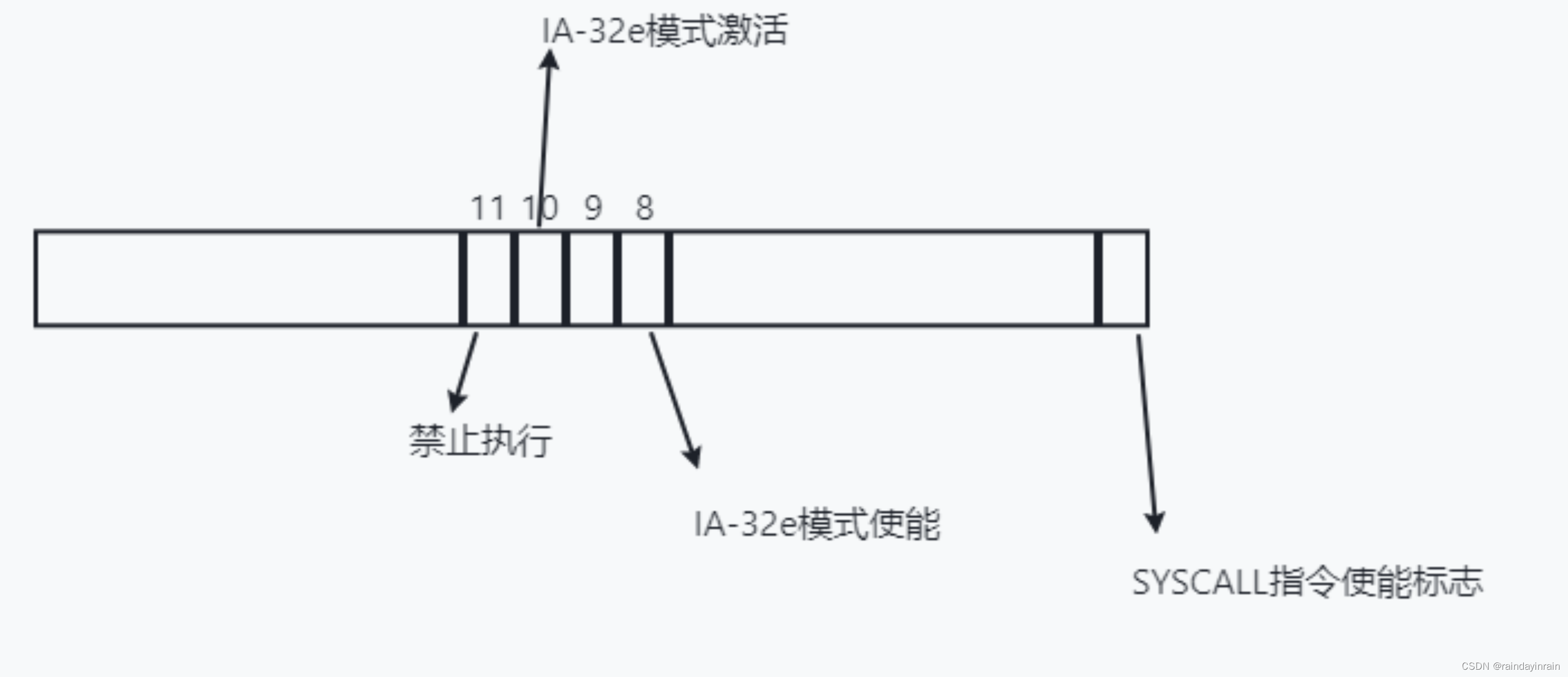

? ? ? ? LME是IA32_EFER寄存器的第8位

? ? ? ? 通过IA32_EFER寄存器的LMA(第10位)可判断处理器是否运行在IA-32e模式。

? ? ? ? 当处理器运行于IA-32e模式,代码段描述符的L标志位可确定处理器运行于64位模式还是兼容模式。

6.1.2.通用寄存器

????????

| 名称 | 特殊功能描述 |

| EAX | 用于累加操作或保存计算结果 |

| EBX | 作为DS数据段寄存器的段内偏移指针 |

| ECX | 字符串和循环操作的计数器 |

| EDX | I/O地址指针 |

| ESI | 作为DS数据段寄存器的段内偏移指针(源地址指针) |

| EDI | 作为ES数据段寄存器的段内偏移指针(目标地址指针) |

| ESP | 栈指针 |

| EBP | 栈帧(段内偏移指针) |

? ? ? ? 在IA-32e体系结构的64位运行模式下,虽然通用寄存器的操作数默认是32位宽,但它们有能力支持64位宽的操作数。Intel公司在64位运行模式里加入了8个新的通用寄存器,因此处理器可使用RAX,RBX,RCX,RDX,RDI,RSI,RBP,RSP,R8~R15这16个通用寄存器,其中的R8~R15寄存器只在64位模式下有效。所有这些寄存器都可访问其内部的字节,字,双字,四字。某些指令需借助REX指令前缀加以修饰才可将操作数扩展至64位。

? ? ? ? 非64位模式下,高32位处于未定义状态。

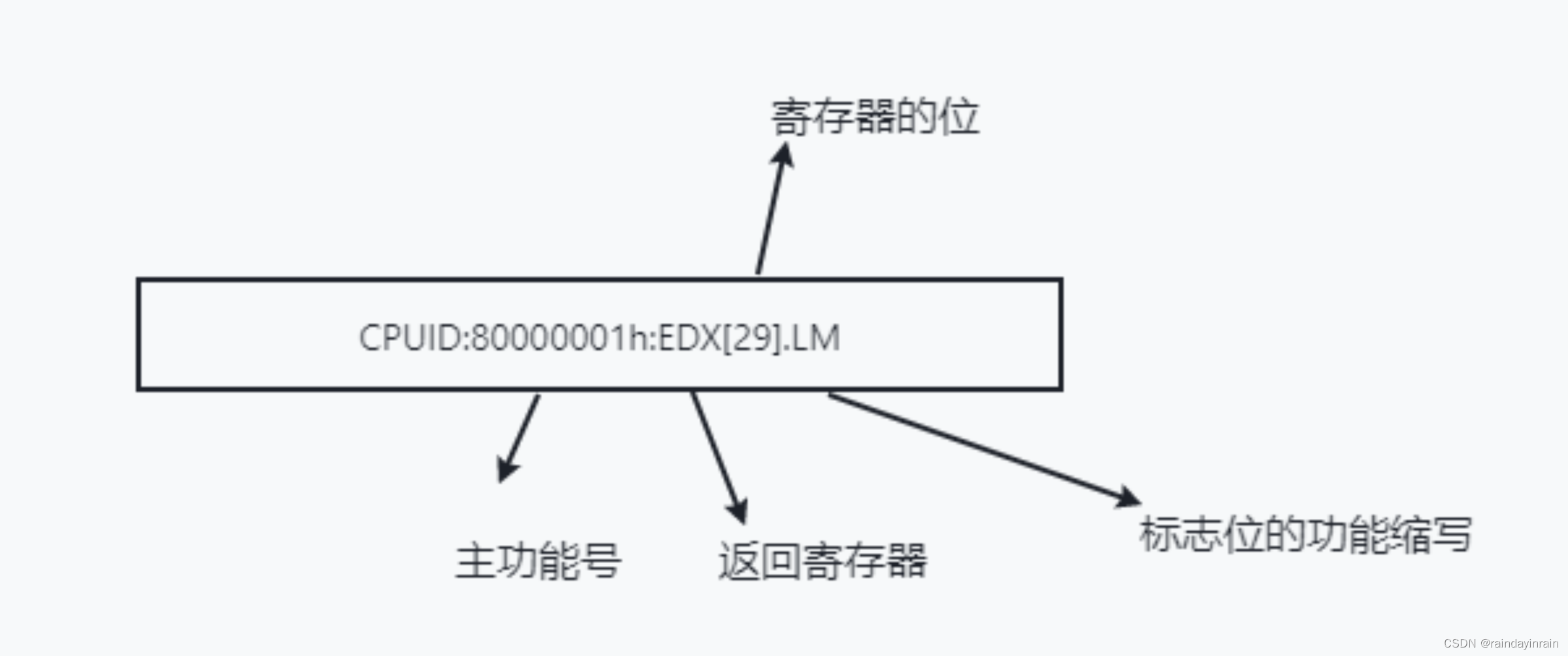

6.1.3.CPUID指令????????

? ? ? ? 用于鉴别处理器信息及检测处理器支持的功能。

? ? ? ? 通过EFLAGS标志寄存器的ID标志位(位于EFLAGS寄存器的第21位)可检测出处理器是否支持CPUID指令。如支持,则软件可自由操作ID标志位。

? ? ? ? CPUID用EAX作为输入,对一些复杂的功能,可能需ECX提供辅助信息。

? ? ? ? 当CPUID指令执行结束后,会使用EAX,EBX,ECX,EDX寄存器保存执行结果。64位下,这些信息依然是32位的。

? ? ? ? CPUID可查询两类信息:基础信息,扩展信息。

? ? ? ? ?

?

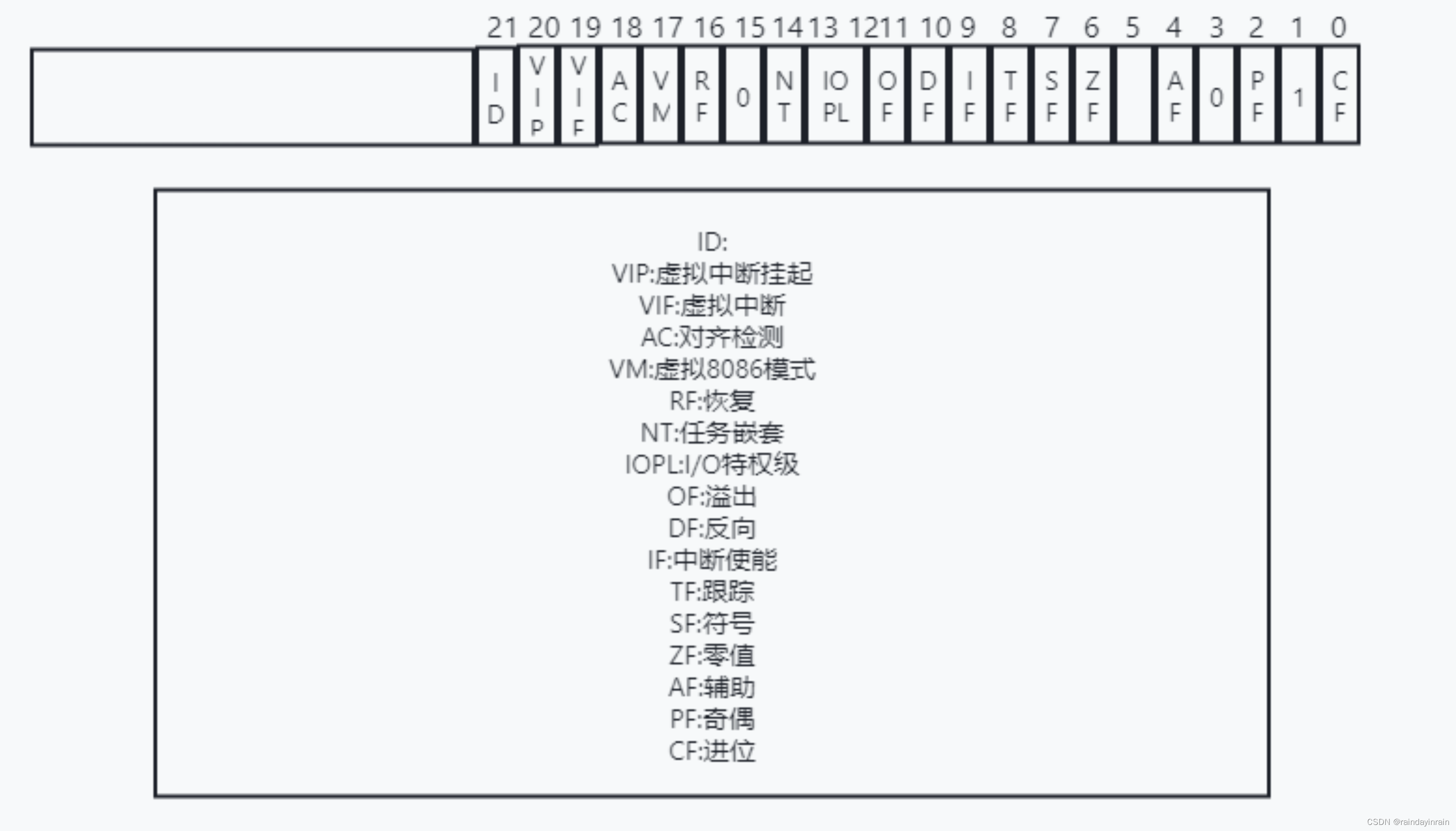

6.1.4.标志寄存器EFLAGS

???????? ?

?

? ? ? ? 任务切换时,处理器会把EFLAGS标志寄存器值保存到任务状态段TSS内,将目标任务状态段TSS内的值更新到EFLAGS中。

?????????1.状态标志

????????

| 缩写 | 全称 | 名称 | 位置 | 功能描述 | |

| 0 | 1 | ||||

| CF | Carry Flag | 进位 | 0 | 反映出无符号整型计算结果的溢出状态,亦可用于多倍精度计算 | |

| 未发生进位或借位 | 发生进位或借位 | ||||

| PF | Parity Flag | 奇偶 | 2 | 计算结果的奇偶校验 | |

| 奇数个1 | 偶数个1 | ||||

| AF | Auxiliary Carry Flag | 辅助 | 4 | 用于BCD算术运算 | |

| 未发生进位或借位 | 进位或借位 | ||||

| ZF | Zero Flag | 零值 | 6 | 反映出计算结果是否为0 | |

| 计算结果为1 | 计算结果为0 | ||||

| SF | Sign Flag | 符号 | 7 | 反映出有符号数运算结果的正负值 | |

| 正值 | 负值 | ||||

| OF | Overflow flag | 溢出 | 11 | 反映出有符号加减计算结果的溢出状态 | |

| 未发生溢出 | 发生溢出 | ||||

? ? ? ? 2.方向标志

? ? ? ? DF是EFLAGS中第10位。

? ? ? ? 3.系统标志和IOPL区域

????????

| 缩写 | 全称 | 位置 | 功能描述 |

| TF | Trap | 8 | 使能单步调试 |

| IF | InterruptEnable | 9 | 使能中断 |

| IOPL | I/O Privilege Level Field | 12,13 | 访问I/O端口地址的最低特权级 |

| NT | Nested Task | 14 | 允许任务嵌套调用 |

| RF | Resume | 16 | 允许调试异常 |

| VM | Virtual-8086 Mode | 17 | 使能Virtual-8086模式 |

| AC | Alignment Check of Access Control | 18 | 数据对齐检测 |

| VIF | Virual Interrupt | 19 | IF中断使能标志位的虚拟镜像 |

| VIP | Virtual interrupt pending | 20 | 中断挂起 |

| ID | Identification | 21 | 检测CPUID指令 |

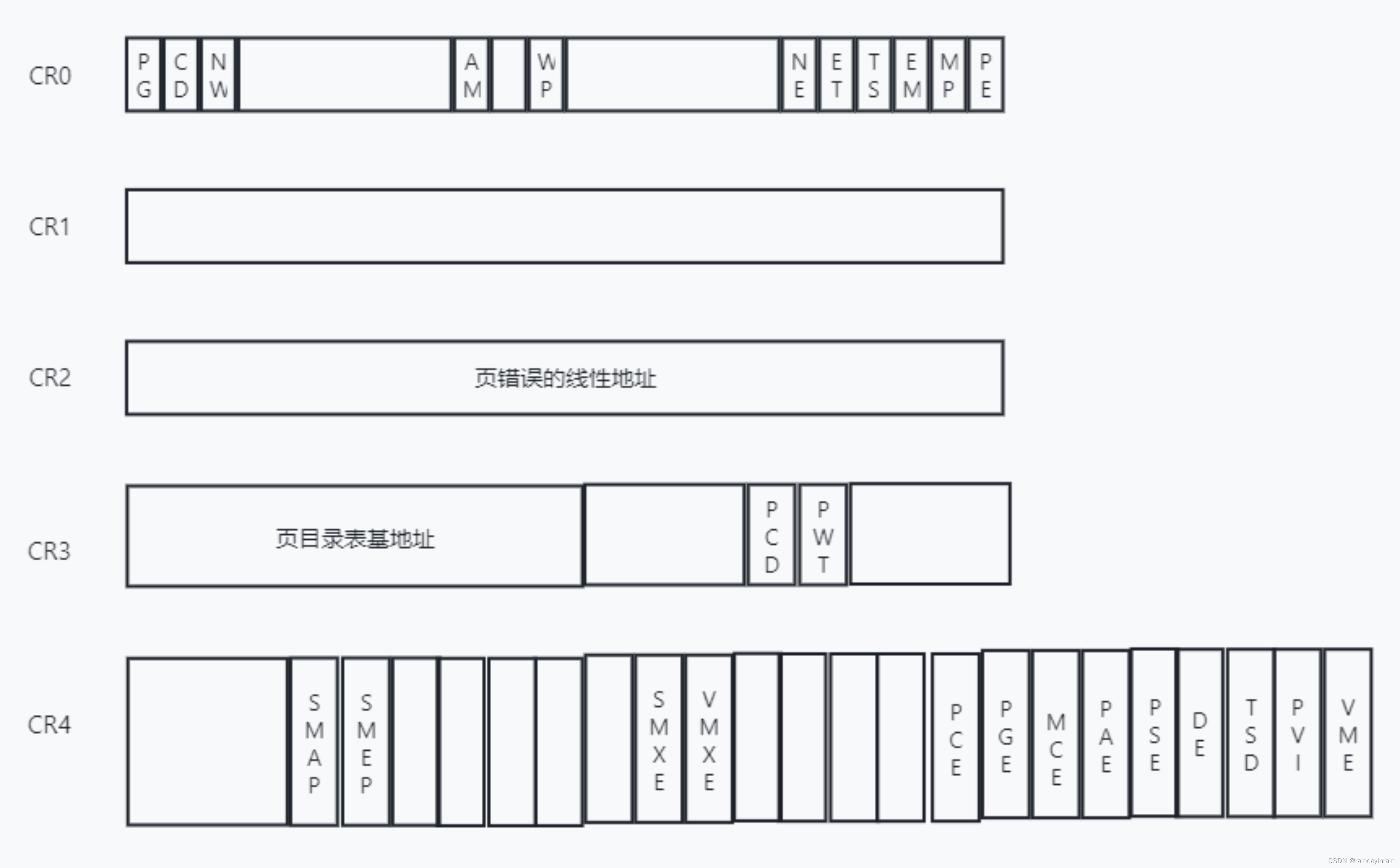

6.1.5.控制寄存器

? ? ? ? CR0,CR1,CR2,CR3,CR4,CR8

| 寄存器 | 功能描述 |

| CR0 | 控制处理器的状态和运行模式 |

| CR1 | 保留 |

| CR2 | 引起#PF异常的线性地址 |

| CR3 | 记录页目录的物理基地址和属性 |

| CR4 | 体系结构扩展功能的使能标志位 |

| CR8 | 读写访问的任务优先级寄存器 |

?

? ? ? ? ?如果在CR0.PE=0时,置位CR0.PG会触发#GP异常。

| CD | NW | 缓存和读写策略 |

| 0 | 0 | 标准缓冲模式,提供最高效的缓存策略 |

| 0 | 1 | 无效设置 |

| 1 | 0 | 处理器不缓存数据 |

| 1 | 1 | 缓存,不保持内存与缓存的一致性 |

| 位 | 缩写 | 读写 | 功能描述 |

| 0 | SCE | R/W | SYSCALL/SYSRET指令的使能标志位(64位模式有效) |

| 1:7 | -- | -- | 保留 |

| 8 | LME | R/W | 使能IA-32e模式 |

| 9 | 保留 | ||

| 10 | LMA | R | 当IA32_EFER_LMA=1表明IA-32e模式已开启 |

| 11 | NXE | R/W | 开启页访问限制功能(PAE模式可用) |

| 12:63 | -- | -- | 保留 |

6.1.6.MSR寄存器组

? ? ? ? MSR寄存器组可提供性能监测,运行轨迹跟踪,调试及其他处理器功能。在用MSR寄存器组之前,应通过CPUID.01h:EDX[5]来检测处理器是否支持MSR寄存器组。

? ? ? ? 每种处理器家族有自己的MSR寄存器组,使用MSR寄存器组前需根据处理器家族信息选择相应的MSR寄存器组。

? ? ? ? 处理器可用RDMSR和WRMSR对MSR寄存器组进行访问,访问过程借助ECX寄存器索引寄存器地址,再由EDX:EAX组成的64位寄存器保持访问值。

6.2.地址空间

? ? ? ? 虚拟地址空间:逻辑地址,有效地址,线性地址等。

6.2.1.虚拟地址

? ? ? ? 1.逻辑地址

? ? ? ? 书写格式为Segment:Offset。

? ? ? ? 2.线性地址

? ? ? ? 逻辑地址-->线性地址

6.2.2.物理地址

? ? ? ? 物理地址空间中不仅包含物理内存,还有硬件设备。

? ? ? ? 开启分页机制下,线性地址需经过页表映射才能转换成物理地址;否则,线性地址将直接映射为物理地址。

? ? ? ? 1.I/O地址

? ? ? ? 必须借助特殊的IN/OUT指令才能访问。I/O地址空间由65536个可独立寻址的I/O端口组成,寻址范围0~FFFFh,其中的端口地址F8h~FFh保留使用。

? ? ? ? 2.内存地址

6.3.实模式

6.3.1.实模式概述

? ? ? ? 采用段寻址方式进行地址访问,直接访问物理地址。此模式下通用寄存器的位宽只有16位。就算借助段寻址方式,通常实模式也只能寻址1MB的物理地址空间。

6.3.2.实模式的段寻址方式

? ? ? ? 段基地址加段内偏移地址的形式进行地址寻址,书写格式为Segment:Offset。其中段基地址值Segment保存在段寄存器中,段内偏移地址值Offset可保存在寄存器内或用立即数代替。

Linear Address = Segment << 4 + Offset

? ? ? ? 实模式的寄存器位宽只有16位,,这样段长度无法超过64KB.

6.3.3.实模式的中断向量表

? ? ? ? 实模式下,中断/异常借助中断向量表将中断/异常向量号与处理程序关联。

? ? ? ? 中断向量表有256项,每项占4B,头2B是offset,后2B是segment。

? ? ? ? 计算机启动后,BIOS会在物理地址0处,创建中断向量表。运行中修改或保存此表,用LIDT或SIDT。

6.4.保护模式

6.4.1.保护模式概述

? ? ? ? 采用全新的分段管理机制和分页管理机制来代替实模式仅基于段的寻址方式。

? ? ? ? 新的分段机制中扩大了处理器的寻址能力和权限检测,还进一步引入了分页机制将原本线性的内存地址空间分页化,立体化,以便于处理器对内存片段的组织和管理。

? ? ? ? 处理器先经过分段管理机制将逻辑地址转换成线性地址后,才能使用分页管理机制进一步把线性地址转换成物理地址。

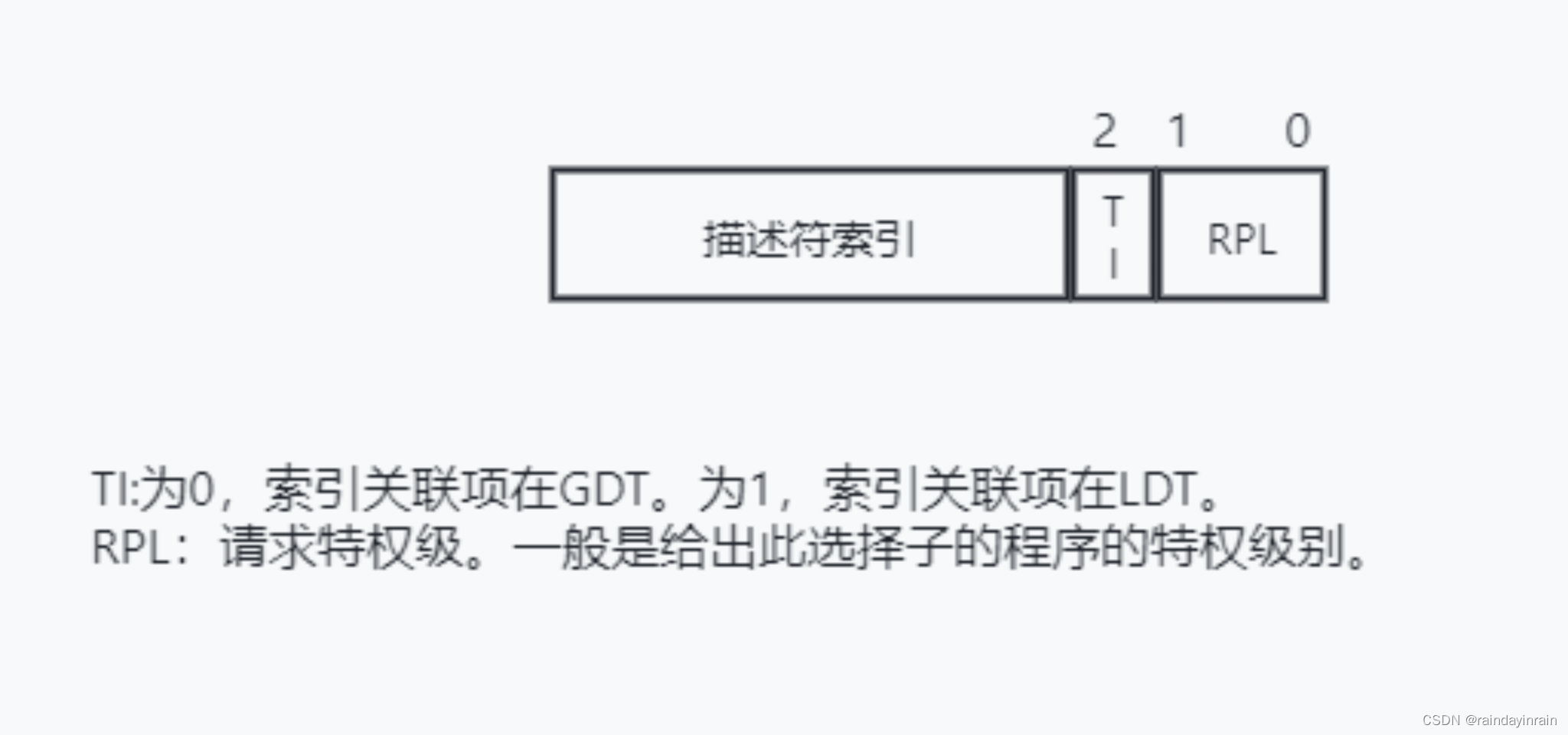

? ? ? ? 保护模式同样采用逻辑地址编址方式。不过此时段寄存器保存的是段选择子。处理器根据段选择子从段描述符表中索引出与之对应的段描述符并将其加载到段寄存器内,段寄存器从加载的段描述符中取得段的基地址。

? ? ? ? 特权级。0、1、2、3、

? ? ? ? 随着特权级而来的,还引入了CPL,DPL和RPL。

? ? ? ? 1.CPL

? ? ? ? 当前特权级保存在CS或SS段寄存器的第0和第1位中。通常,CPL是正在执行的代码段特权级。

? ? ? ? 2.DPL

? ? ? ? 表示段描述符或门描述符的特权级,它保存于段描述符或门描述符的DPL区域内。处理器访问段描述符或门描述符时,处理器会对比描述符中的DPL值,段寄存器的CPL值及段选择子的RPL值。????????

? ? ? ? 3.RPL

? ? ? ? 是段选择子的重载特权级,用于确保程序有足够的权限去访问受保护的程序,它保存于段选择子的第0和第1位。即使程序有足够权限去访问目标段,但如RPL权限不足,依然无法访问。故,RPL数值大于CPL时,以RPL参与目标特权级比较。反之亦然。?

? ? ? ? 段选择子只是一个16位的段描述符索引值。

? ? ? ? 保护模式下的段寄存器无法直接加载段描述符,需用段选择子索引将目标段描述符加载到段寄存器的缓存区。

? ? ? ? 将Index * 8作为偏移量,从描述符表中取得目标描述符,并对CPL,RPL及DPL进行检测。如检测通过,处理器便将目标描述符加载到段寄存器的缓存区内。

? ? ? ? 这些段寄存器的缓存区域记录着段描述符的基地址,限长,属性信息。

? ? ? ? 虽然系统可定义8192个段描述符,但同一时刻只能使用6个段(CS,SS,DS,ES,FS,GS)。

? ? ? ? 保护模式下的段寄存器共包含两个区域:可见区域和不可见区域。当段选择子被处理器加载到段寄存器的可见区域后,处理器会自动将段描述符载入到段寄存器的不可见区域。

? ? ? ? 在多核处理器系统中,当描述符表发生改变时,软件有义务重新将段描述符加载到段寄存器。如段寄存器没更新,处理器可能仍沿用缓存区中的段描述符数据。?

? ? ? ? 在加载段选择子到段寄存器的过程中,处理器会根据段选择子的Index值,从GDTR/LDTR寄存器指向的描述符表中索引段描述符。GDTR/LDTR寄存器是一个48位的伪描述符,其中保存着全局描述符表或局部描述符表的首地址和长度。

? ? ? ? 为避免3特权级的对齐检测错误,伪描述符应按双字进行地址对齐。

? ? ? ? 1.全局描述符表

? ? ? ? 它本身不是一个段描述符,而是一个线性地址空间中的数据结构。使用GDT前,需用LGDT汇编指令将其线性基地址和长度加载到GDTR寄存器中。由于段描述符长度为8B,则GDT线性基地址按8B边界对齐可使处理器的运行效果最佳。

? ? ? ? 2.局部描述符表

? ? ? ? 是一个LDT段描述符类型的系统数据段,处理器需使用GDT的一个段描述符来管理它。处理器用LLDT汇编指令可将GDT表内的LDT段描述符加载到LDTR寄存器。LDTR寄存器会保存LDT段的选择子,线性基地址,长度。

? ? ? ? 局部描述符表可有0个或多个。

6.4.2.保护模式的段管理机制

? ? ? ? 保护模式的段管理机制是一套健全,独立,基于逻辑地址寻址方式的管理机制,其中不乏涉及段的执行权限,属性等检测信息。

? ? ? ? 保护模式可不开启分页管理机制,但进入保护模式就意味着开启了段管理机制。

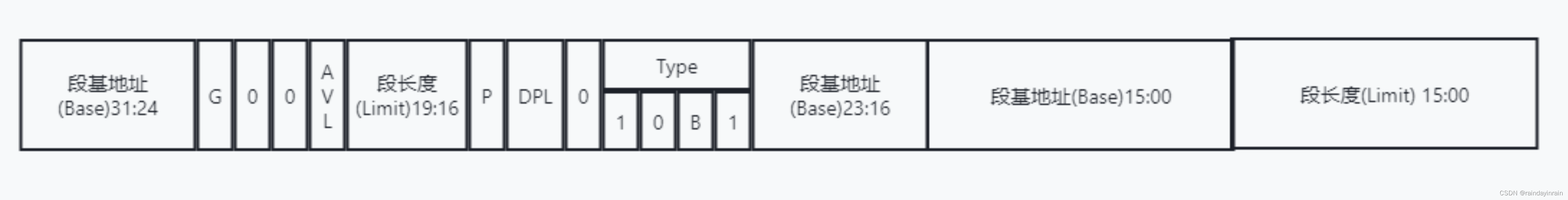

| 缩写 | 功能描述 |

| L | 保护模式下,此位保留使用,设为0即可。 |

| AVL | 此位被系统软件使用,通过设为0。 |

| 段基地址(Base) | 是段的起始地址。建议按16B对齐。 |

| D/B | 用于标识代码段的操作数位宽,或栈段的操作数位宽及上边界【32位代码/数据段为1,16位代码/数据段为0】 1.可执行代码段 有效地址和操作数的默认宽度。 1-》32位地址,32位或8位操作数 0-》16位地址,16位或8位操作数 前缀66h可调整默认操作数,前缀67h可调整有效地址宽度 2.栈段 栈指针的默认操作数 1-》32位栈指针ESP 0-》16位栈指针SP 3.向下扩展的数据段 指定上边界位宽。 1-》上边界是FFFFFFFFh 0-》上边界是FFFFh |

| DPL | 描述符特权级 |

| G | 1->以4KB为颗粒度;0-》以字节为颗粒度 |

| 段长度 | G位为1时,段长度为4KB~4GB;G位为0时,段长度为1B~1MB |

| P | 1-》段已在内存 |

| S | 1-》代码段、数据段 0-》系统段 |

| Type | 指定段、门描述符的类型,对S标志位做进一步解释 |

? ? ? ? 1.代码段描述符

? ? ? ? 如段描述符的S与Type的最高位被置位,则这个段描述符的类型为代码段描述符。

| Type区域 | 功能 | |||

| 43 | 42 | 41 | 40 | |

| 1 | C | R | A | |

| 1 | 0 | 0 | 0 | 非一致性,不可读,未访问 |

| 1 | 0 | 0 | 1 | 非一致性,不可读,已访问 |

| 1 | 0 | 1 | 0 | 非一致性,可读,未访问 |

| 1 | 0 | 1 | 1 | 非一致性,可读,已访问 |

| 1 | 1 | 0 | 0 | 一致性,不可读,未访问 |

| 1 | 1 | 0 | 1 | 一致性,不可读,已访问 |

| 1 | 1 | 1 | 0 | 一致性,可读,未访问 |

| 1 | 1 | 1 | 1 | 一致性,可读,已访问 |

- ? ? ? ? A

? ? ? ? 记录代码段是否已被访问过。A为1表示已被访问过,A为0表示未被访问过。处理器只负责置位此标志位,只能借助程序手动将其复位。

- ? ? ? ? R

? ? ? ? 如想读取程序段中的数据需置位此标志位。

- ? ? ? ? C

? ? ? ? 代码段可分为一致性代码段,非一致性代码段。一个低特权级的程序(代码段)可执行或跳转至一个高特权级(或相同特权级)的一致性代码,并在执行高特权级代码段的过程中保持低特权级的CPL不变。如程序想要跳转至一个不同特权级的非一致性代码段,除非使用调用门或任务门,否则会触发#GP异常。所有的数据段都是非一致性的,意味着它们不能被低特权级的程序访问。

? ? ? ? 2.数据段描述符

? ? ? ? 如果段描述符的S处于置位状态,Type最高位为0,则这个段描述符的类型为数据段描述符。

| Type区域 | 功能 | |||

| 43 | 42 | 41 | 40 | |

| 0 | E | W | A | |

| 0 | 0 | 0 | 0 | 向上扩展,只读,未访问 |

| 0 | 0 | 0 | 1 | 向上扩展,只读,已访问 |

| 0 | 0 | 1 | 0 | 向上扩展,可读写,未访问 |

| 0 | 0 | 1 | 1 | 向上扩展,可读写,已访问 |

| 0 | 1 | 0 | 0 | 向下扩展,只读,未访问 |

| 0 | 1 | 0 | 1 | 向下扩展,只读,已访问 |

| 0 | 1 | 1 | 0 | 向下扩展,可读写,未访问 |

| 0 | 1 | 1 | 1 | 向下扩展,可读写,已访问 |

- ? ? ? ? E

? ? ? ? 为1表示向下扩展,为0表示向上扩展。通常下数据段向上扩展。

- ? ? ? ? W

? ? ? ? 为1时进行读写访问

? ? ? ? 为0时只能进行读访问

- ? ? ? ? A

? ? ? ? 记录数据段是否被访问过

? ? ? ? 3.系统段描述符

? ? ? ? 如段描述符的S处于复位状态, 则这个段描述符的类型为系统段描述符。

| Type区域 | 功能 | |||

| 43 | 42 | 41 | 40 | |

| 0 | 0 | 0 | 0 | 保留 |

| 0 | 0 | 0 | 1 | 16位TSS段描述符(有效的) |

| 0 | 0 | 1 | 0 | LDT段描述符 |

| 0 | 0 | 1 | 1 | 16位TSS段描述符(使用中) |

| 0 | 1 | 0 | 0 | 16位调用门描述符 |

| 0 | 1 | 0 | 1 | 任务门描述符 |

| 0 | 1 | 1 | 0 | 16位中断门描述符 |

| 0 | 1 | 1 | 1 | 16位陷阱门描述符 |

| 1 | 0 | 0 | 0 | 保留 |

| 1 | 0 | 0 | 1 | 32位TSS段描述符(有效的) |

| 1 | 0 | 1 | 0 | 保留 |

| 1 | 0 | 1 | 1 | 32位TSS段描述符(使用中) |

| 1 | 1 | 0 | 0 | 32位调用门描述符 |

| 1 | 1 | 0 | 1 | 保留 |

| 1 | 1 | 1 | 0 | 32位中断门描述符 |

| 1 | 1 | 1 | 1 | 32位陷阱门描述符 |

? ? ? ? 本节先介绍LDT段描述符,TSS描述符,调用门描述符三种系统段描述符。

? ? ? ? 1.LDT段描述符

? ? ? ? LDT可在各程序或任务间起到隔离作用。操作系统使用其他方法同样可以起到程序间的隔离作用,如为每个任务创建独立的页表结构等。

? ? ? ? 2.TSS描述符

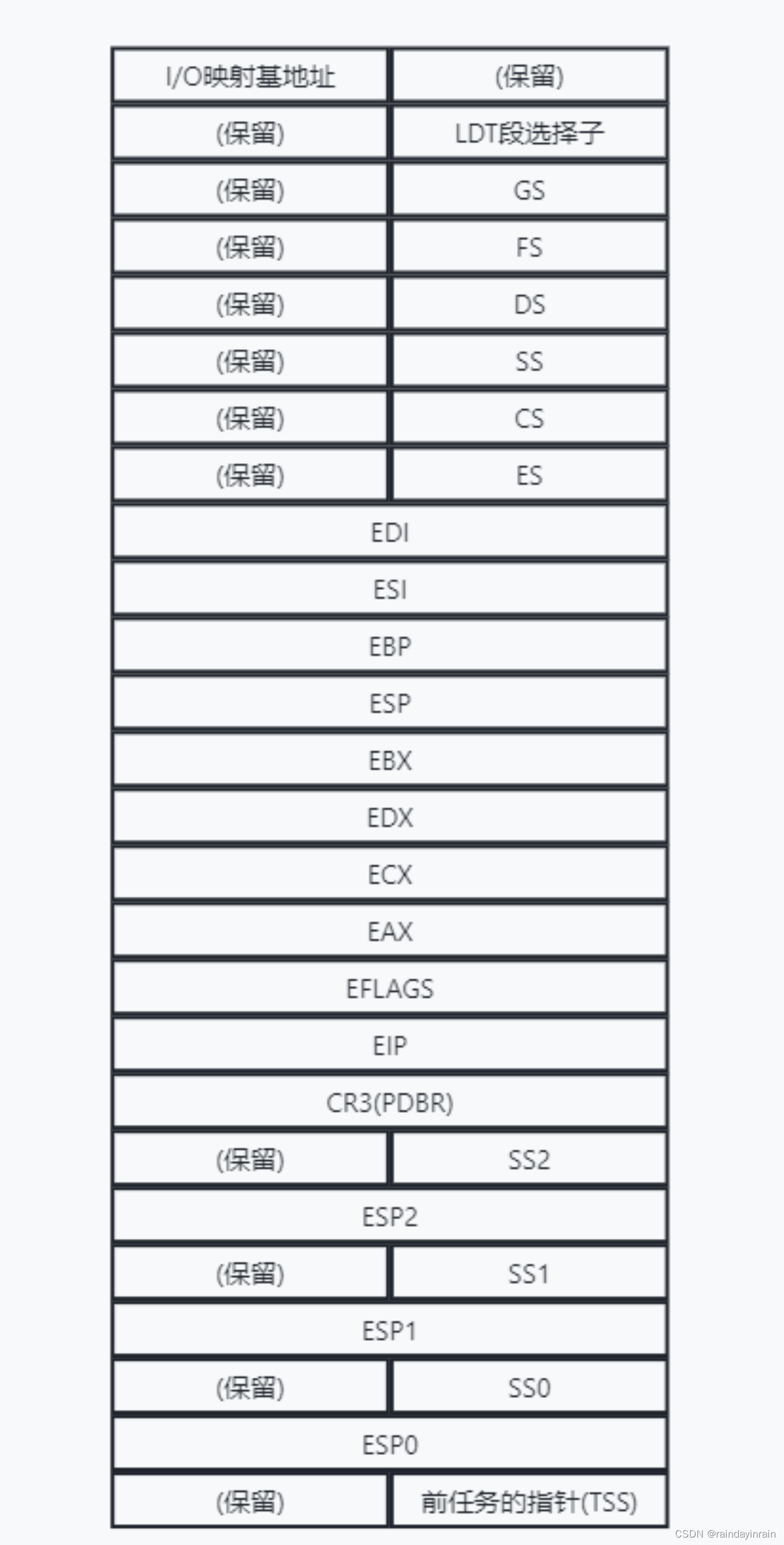

? ? ? ? 用于保存任务的处理器状态信息。处理器需借助TSS描述符才能对任务状态段进行访问和管理。

? ? ? ? B标志位指示任务是否处于忙状态,一个处于忙状态的任务表明它正在运行或已经挂起。

? ? ? ? TSS描述符只能保存在GDT内。

? ? ? ? 任务寄存器(TR)与LDTR结构相似?,不过TR保存的是TSS段选择子及TSS描述符信息。

? ? ? ? 试图将TSS段选择子加载到段寄存器会触发#GP异常;访问一个TI为1的TSS段选择子会触发#GP异常或TS异常。

? ? ? ? TSS段,主要用于任务切换(或特权级切换)时,保存处理器的寄存器状态,及切换至对应的特权级栈空间,从而使得任务返回时能还原执行现场。

? ? ? ? TSS被分为两部分:动态区域,静态区域。任务在切换过程中挂起时,处理器会将执行现场保存在动态区域内。

? ? ? ? 上述是32位TSS结构说明图

| 处理器执行环境 | 功能描述 |

| 通用寄存器 | EAX,ECX,EDX,EBX,ESP,EBP,ESI和EDI寄存器值 |

| 段选择子 | 保存在ES,CS,SS,DS,FS和GS寄存器中的段选择子 |

| EFLAGS标志寄存器 | EFLAGS标志寄存器值 |

| EIP指令寄存器 | EIP指令指针寄存器值 |

| 上一个任务(TSS段选择子) | 前一个任务的段选择子(在使用调用,中断或异常进行任务切换时被设置,使用IRET指令可切换会原任务) |

? ? ? ? ?上述是TSS的动态区域功能说明表

? ? ? ? 当任务在切换过程中挂起时,处理器只会读取静态区域的数据,不会更新(改变)静态区域中的数值。

| 处理器执行环境 | 功能描述 |

| LDT段选择子 | 局部描述符表LDT的段选择子 |

| CR3控制寄存器 | CR3寄存器值(页目录的物理基地址) |

| 栈指针(特权级0~2) | 目标特权级的栈空间(栈段选择子和段内偏移地址) |

| T标志位 | 任务切换时的调试标志位(T=1会触发调试异常) |

| I/O位图基地址 | I/O许可位图和中断重映射位图在TSS段中的起始地址 |

? ? ? ? TSS的静态区域功能说明表

? ? ? ? 此处的栈空间是静态的,不会因任务切换而发生改变,但SS和ESP寄存器值将会随着任务的切换而被更新。

? ? ? ? 对于处理器级的任务切换而言,它只能在满足以下四种条件之一时才会发生。

- ? ? ? ? 当前程序通过JMP或CALL指令跳转至GDT中的TSS描述符时,任务切换将会发生。

- ? ? ? ? 当前程序通过JMP或CALL指令跳转至GDT或LDT中的任务门段描述符时,任务切换将会发生。

- ? ? ? ? 如果一个IDT表项使用任务门描述符来保存中断或异常处理程序,则在触发中断或异常时任务切换将会发生。

- ? ? ? ? 如当前任务的EFLAGS.NT标志位被置位,那么在执行IRET指令时任务切换将会发生。

? ? ? ? 除上述4种硬件级任务切换方法外,程序还可使用软件逻辑来实现任务切换。如采用独立页表空间切换方式(通过切换页表及JMP指令来切换任务)的Linux系统内核,它只借助TSS的静态区域为特权级提供栈空间,而任务的执行现场将通过手动方式保存于栈或PCB(进程控制结构体)中。

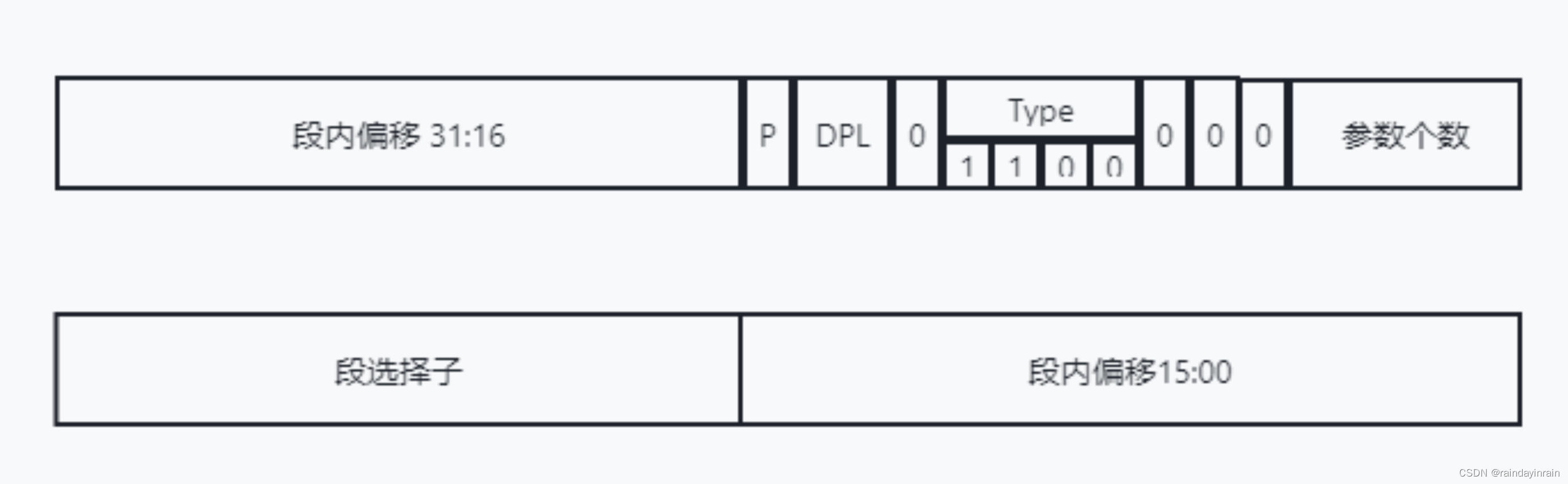

? ? ? ? 3.调用门描述符

? ? ? ? 调用门可让不同特权级间的程序实现受控切换,通常用于受特权级保护的操作系统或程序中。

? ? ? ? 调用门的一个显著特点是借助CALL指令穿过调用门可访问更高特权级(CPL>=DPL)的代码段。如果目标代码段是非一致性的,则栈切换会发生。一致性代码不改变CS的CPL。JMP指令只能穿过相同特权级(CPL=DPL)的非一致性代码段,但CALL与JMP却都可以访问更高特权级的一致性性代码段。

| 位名 | 功能描述 |

| 段选择子 | 指定段选择子 |

| 段内偏移 | 段内偏移量(指定程序入口地址) |

| DPL | 描述符特权级 |

| P | 指定调用门描述符是否有效 |

| 参数个数 | 发生栈切换时需复制的参数数量 |

? ? ? ? ?上图是调用门描述符的位功能说明表。除了上述系统描述符外,还有陷阱门,中断门,任务门等描述符较为常用。它们均可作为中断描述符表项使用。

6.4.3.保护模式的中断/异常处理机制

? ? ? ? 处理器捕获中断/异常后,会强制挂起当前程序(或任务)转而执行中断/异常处理程序,因此可将中断/异常看成一种服务或函数进行处理。当处理程序执行完毕,处理器会唤醒被挂起的工程或任务,使程序不失连续性地执行,就像从没发生过中断/异常一样。

? ? ? ? 中断可在程序执行任务时触发,可以来自一个外部硬件设备请求,也可 来自INT n指令。异常只能在检测到处理器执行故障时触发,处理器可检测的异常种类有很多。

? ? ? ? 中断异常用向量号标识。向量号的数值范围是0~255,其中0~31号向量被Intel处理器作为异常向量号或保留使用(不要使用保留的向量号),剩余32~255号向量将作为中断向量号供用户使用。

? ? ? ? IDT的前32项用于索引异常处理程序,其他项用于索引中断处理程序。用户可自由为外部硬件设备指派中断向量号,这也是外部硬件设备与处理器的主要通信方式。

? ? ? ? IDT借助门描述符将中断/异常向量号与处理程序关联起来。IDT是一个门描述符数组(每个门描述符占8B),其中第一个表项是有效的,并非NULL描述符。IDT不能包含超过256个门描述符。

? ? ? ? IDT可保存在线性地址的任务位置,但为了使处理器达到最佳缓冲性能,尽量将IDT按8B边界对齐。

? ? ? ? 处理器借助IDTR寄存器可定位出IDT的位置,但在使用IDT前,必须用LIDT指令(SIDT指令用于保存IDTR寄存器值)将IDT的线性基地址(32位)和长度(16位)加载IDTR寄存器中,LIDT指令只能在CPL=0时执行。通常IDT创建于操作系统初始化过程。

? ? ? ? IDT的表项是由门描述符组成,可使用陷阱门,中断门,任务门三类门描述符。这三种门描述符与上节的调用门描述符极其相似。

? ? ? ? 1.陷阱门描述符和中断门描述符

? ? ? ? 位图结构上,与调用门描述符相似。

????????