本篇文章,介绍的是timing exception

Using Timing Exception

有一些path不存在,也不需要PT去计算,因为我们会告诉工具不要去计算这些path。

关于Timing Exception 主要有以下命令:

set_false_path 移除掉不用PT去分析的path

set_multicycle_path 允许超过一个clock的path

set_max_delay 允许最大delay

set_min_delay 允许最小delay

report_exceptions 验证在design中的任何timing exceptions

reset_path restore default timing constraints on sepcified paths 清除所有的constraint

timing exception place from 和to 在deseign中的timing points

合法的start 点和end 点有:

start点:

输入端口和寄存器的clk pin

end 点:

输出端口和寄存器的data pin

start点和end点同时指定:

clock object(直接指定时钟)

另外还可以指定中间点 ,通过-through 选项,但是该选项非常浪费PT的计算时间。

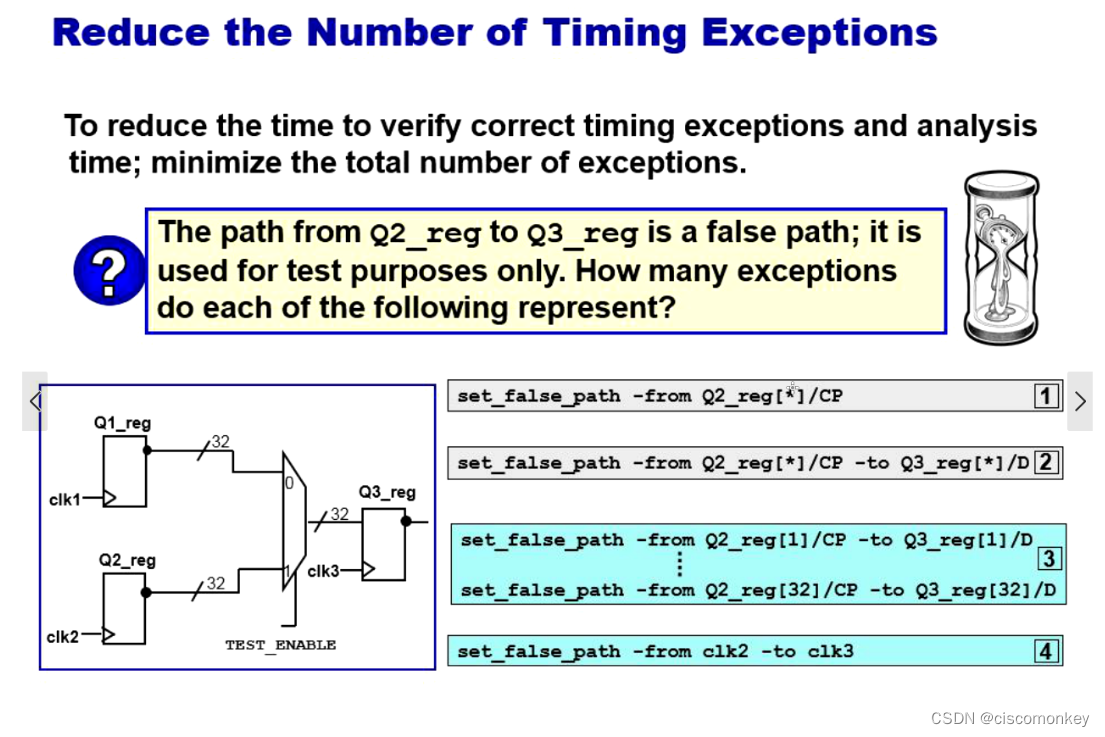

如上图所示,对于第一个Q2_reg[*]/CP 假如说有32个reg,那么就是

Q2_reg[1] 到所有的fan_out、以及Q2_reg[2]到所有的fan_out 一直到Q2_reg[32]到所有的fan_out

对于第二种类,Q2_reg[*]到Q2_reg[ ] 可以表示reg1到reg1-32,然后是reg2-reg1-32 直到reg32-reg1-32 ,相当于3232种path

对于第三类写法,也就限定了只有32条

对于第四种写法,包含了所有的clk2到clk3

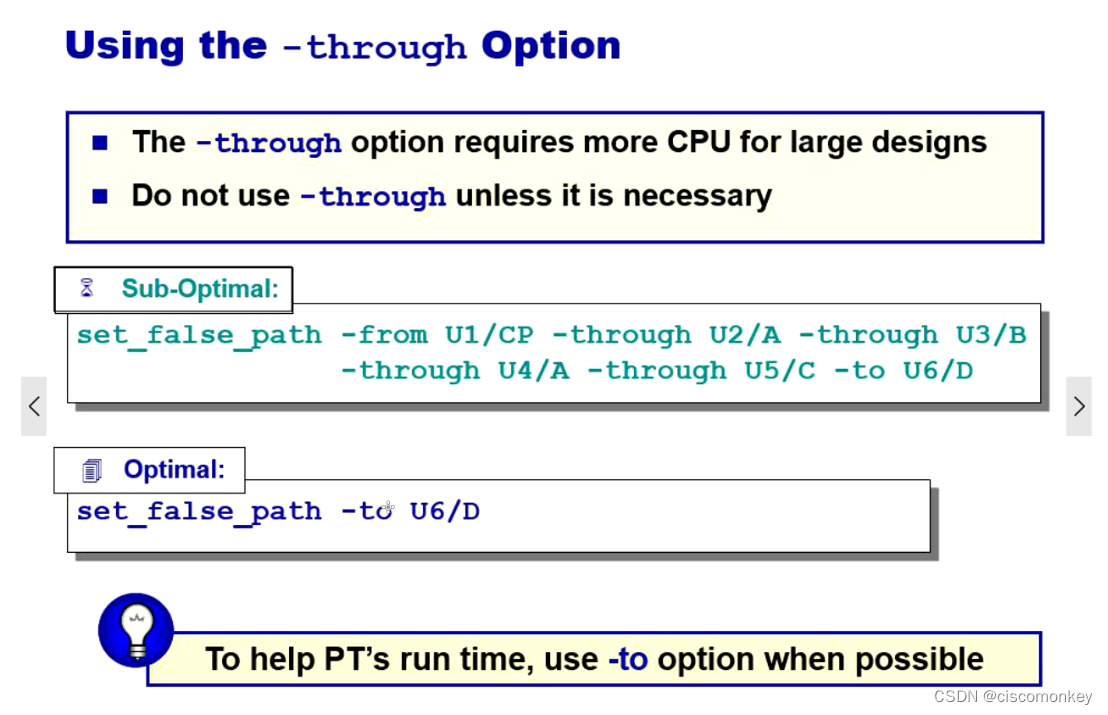

如上图所示,尽量不要使用-through,当然像上面sub-optimal中所示,

如果又把-from,又把-through,又把-to写出来,当然是最好不过,尽量不要纯粹的去写-through

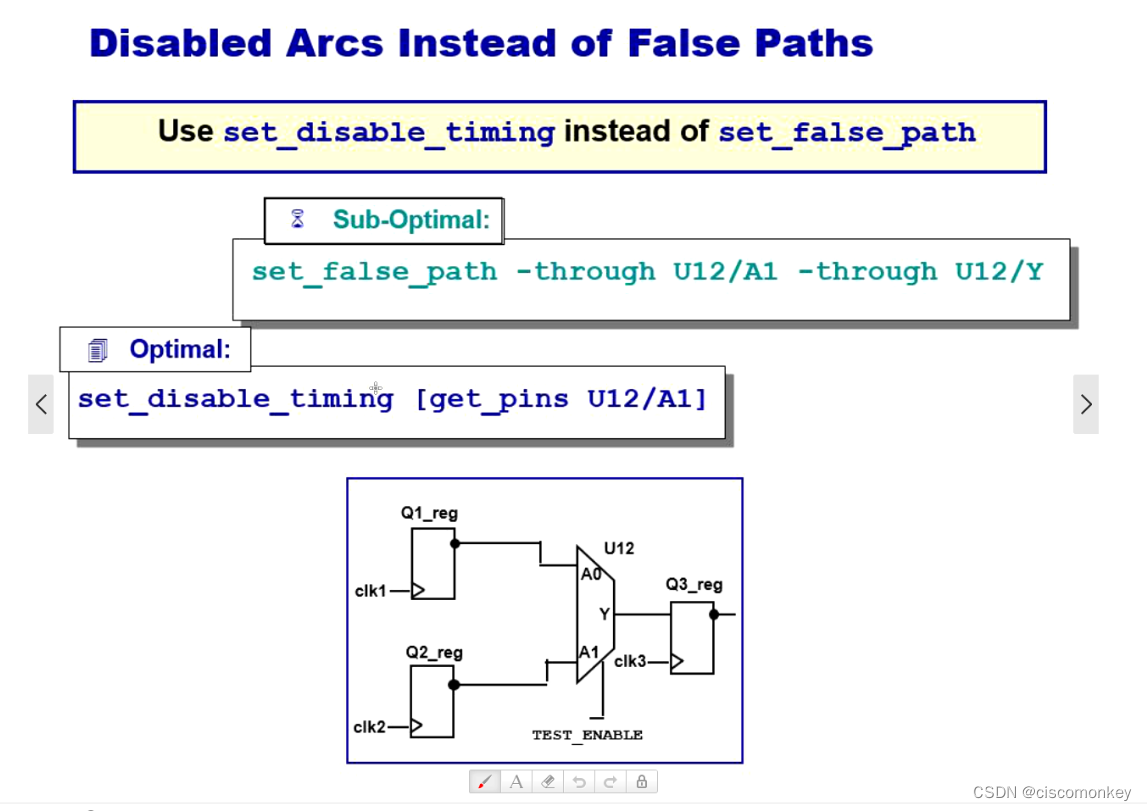

如上图所示,如果你实在没有办法,假如说你使用set_false_path 无法把-from和-to 一一例举出来。

那么此时,你可以使用set_disable_timing

如上图所示,你可以把经过U12/A1的所有的path都设置为falth path。

对于哪些path,我们需要设置为falth path

对于一些logic不存在的路径、两个异步时钟之间

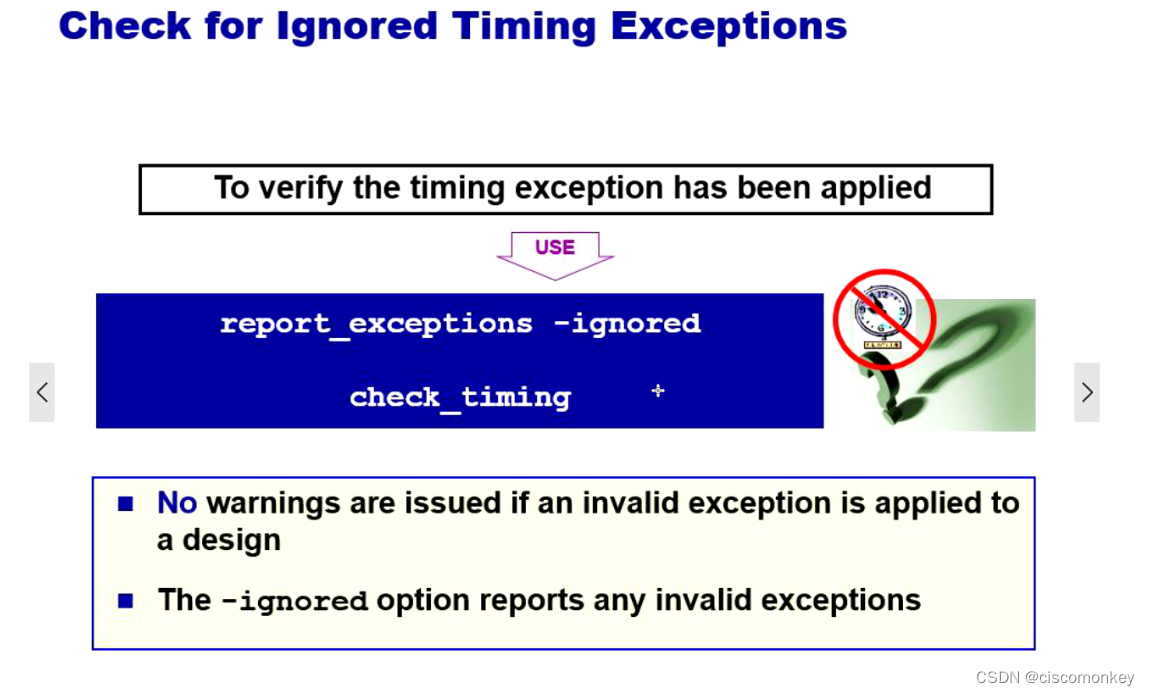

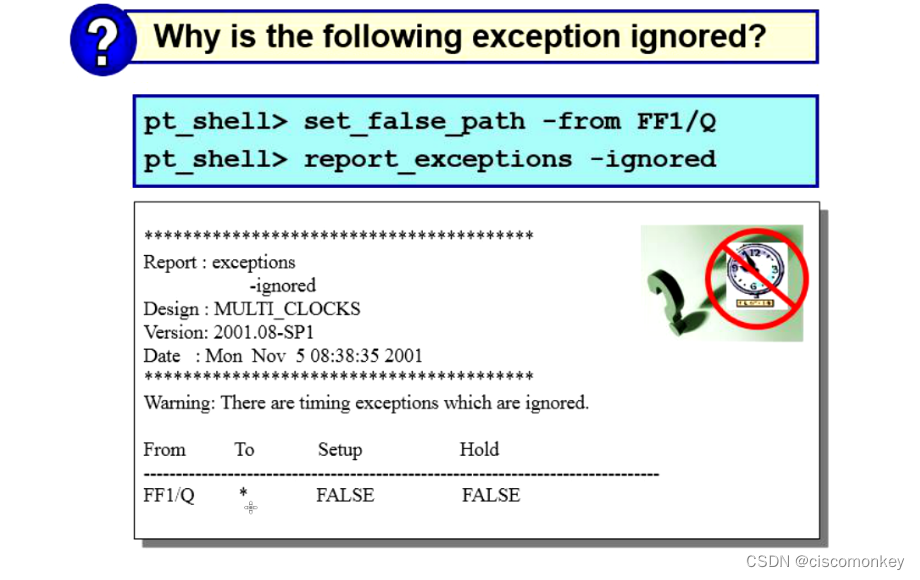

使用report_exception可以写出所有的你写过的exception

如上图所示,当我把来源于FF1/Q都设置为falth path,然后报告出来,我们就可以看到,只要是来源于FF1/Q的全部都设置为了falth path。

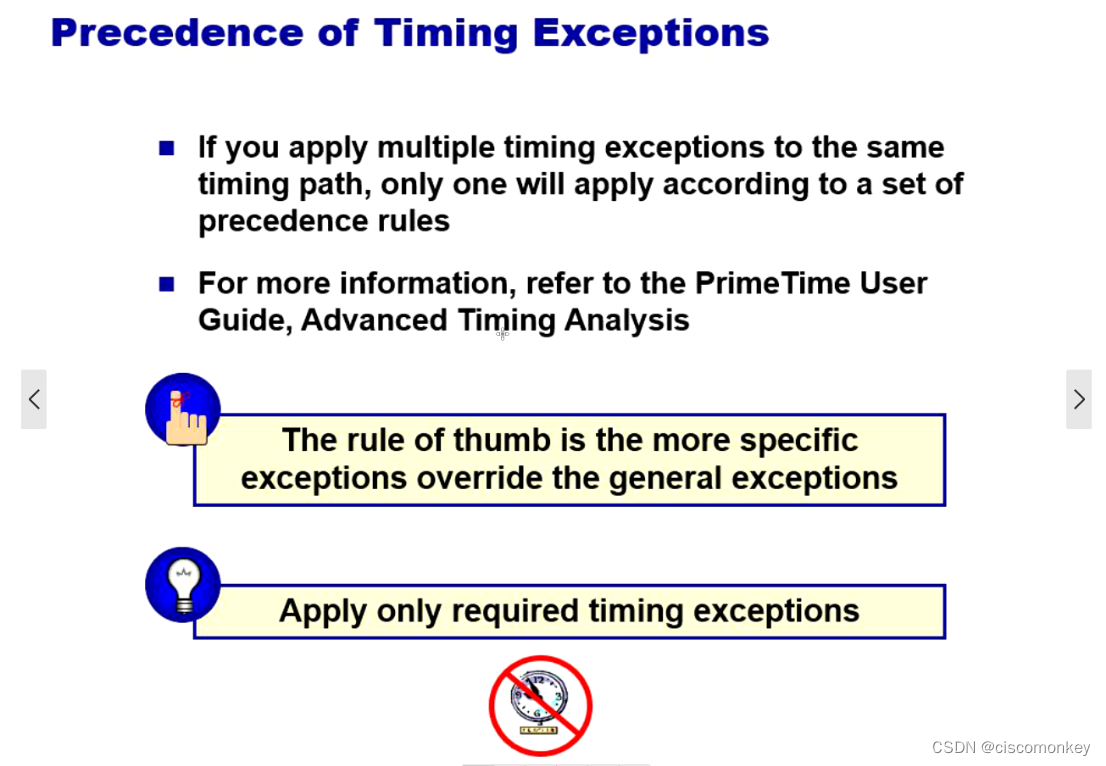

timing exception的优先级:如果在同一条path上面都设置有falth path,那么原则是,这条timing exception 谁覆盖得越多,就谁优先,工具也会优先处理。

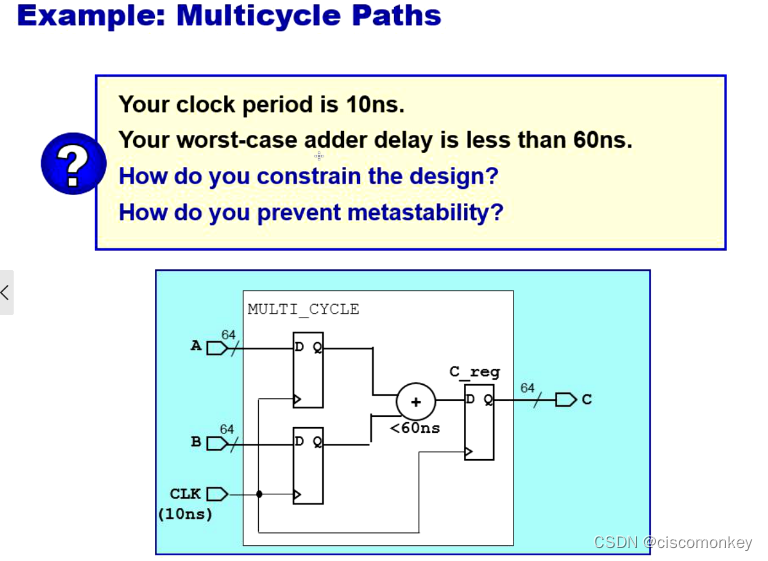

multicycle path

如上图所示,像加法器类似的,肯定是在一个周期内是做不出来的。

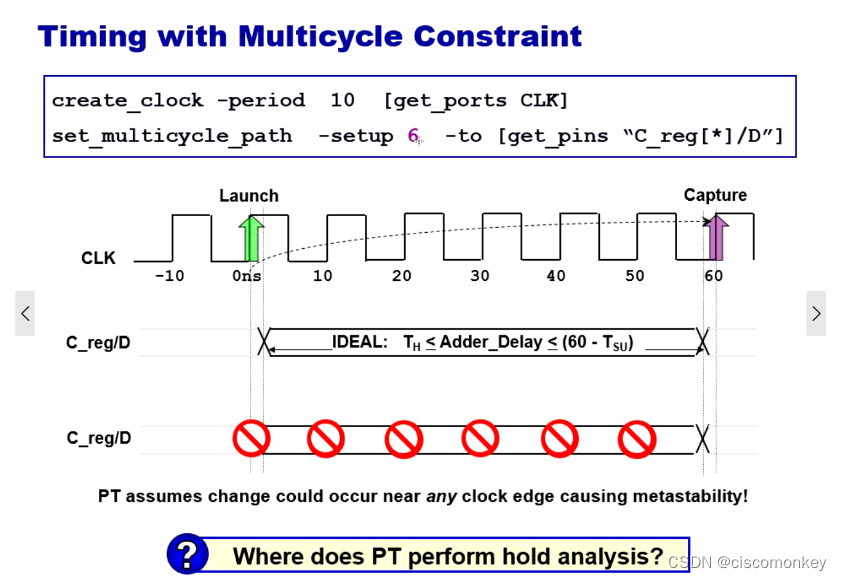

如上图,延迟了多少个周期,-setup 6 就相当于 延迟了6个周期,类似于时钟是原来的1/6

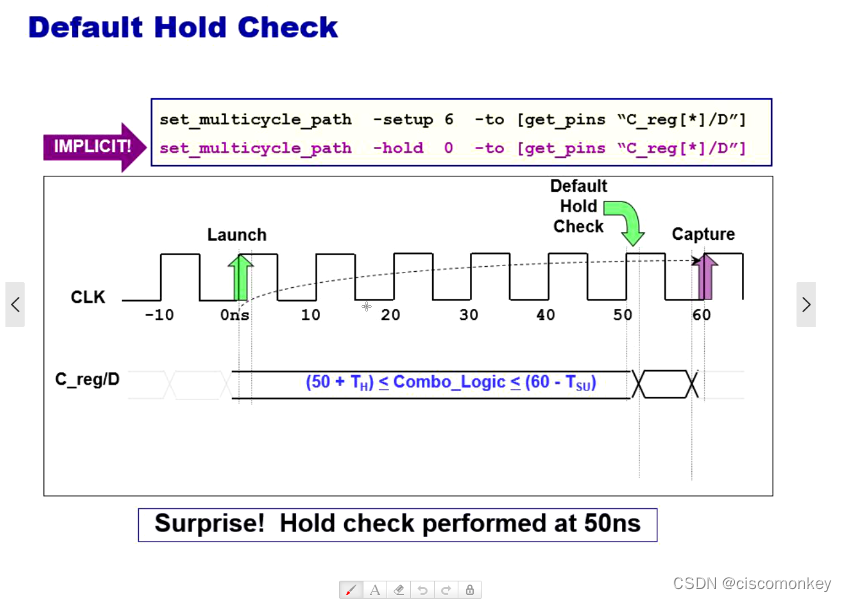

上图,如果不去设置hold,那么hold check 在50ns。所以上面紫色的命令可以不设置,也会在50ns的地方check

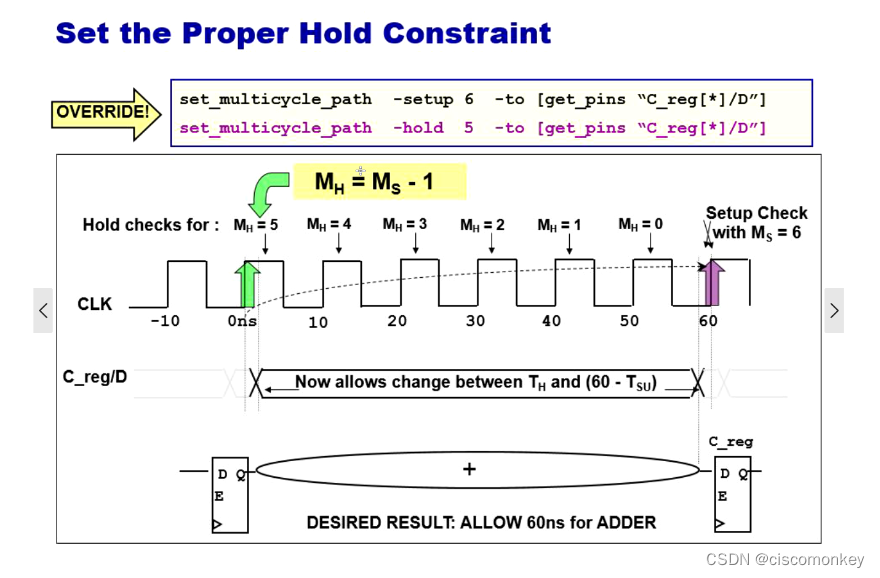

如上图,如果把hold设置为5,那么hold的值将在0ns,也就是说允许数据在0ns~60ns时刻发生数据改变的,这个才是符合预期的。