概览

? ? ? ? 本章节的CSI-2实现案例,假设接口由D-PHY单向的时钟和数据加上forward Escapde Mode以及可选的去斜(deskew)功能组成。案例如下图所示:

实现案例框图和覆盖范围说明?

? ? ? ? 本示例中,分层的架构由以下几个部分描述:

- ? ? ? ? D-PHY实现方案细节

- ? ? ? ? 多Lane数据合并细节

- ? ? ? ? 协议层细节

? ? ? ? 本示例只使用RAW8数据类型做为参考,因此不会有封包/解封包或字节时钟(byte clock)/像素时钟(pixel clock)时序等相关参考设计方案,因为这种类型的实现方案中不需要它们。

? ? ? ? 示例也没有错误恢复机制或错误处理细节的相关内容,因为本章节主要目的是展示从数据流的视角来看的实现方案。

CSI-2发送器细化框图

CSI-2发送器框图?

CSI-2接收器细化框图

CSI-2接收器框图

D-PHY实现细节

? ? ? ? 实现方案的PHY层有如下顶层结构:

D-PHY层框图?

模块可被划分为:

CSI-2发送器侧(Transmitter side):

- ? ? ? ? Clock lane(Transmitter)

- ? ? ? ? Data1 lane(Transimitter)

- ? ? ? ? Data2 lane(Transmitter)

CSI-2接收器侧(Receiver side):

- ? ? ? ? Clock lane(Receiver)

- ? ? ? ? Data1 lane(Receiver)

- ? ? ? ? Data2 lane(Receiver)

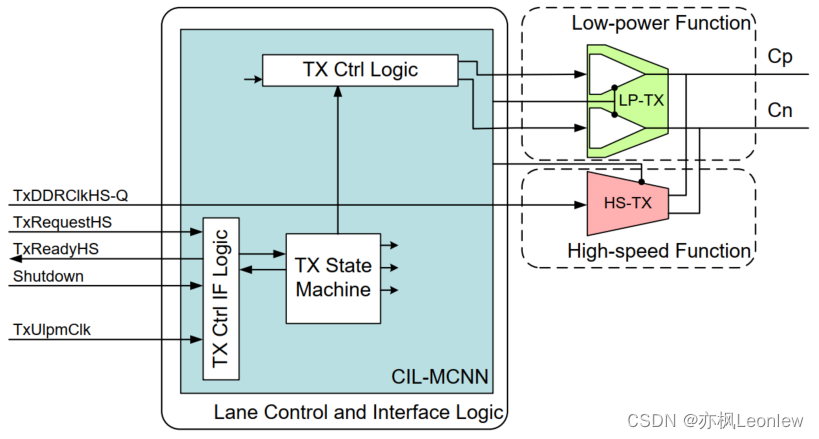

CSI-2时钟Lane发送器

?CSI-2 Clock Lane Transmitter

? ? ? ? 构建CSI-2时钟Lane发送器的D-PHY模块有:

- ? ? ? ? LP-TX,用于低功耗功能(Low-power function)

- ? ? ? ? HS-TX,用于高速功能(High-speed function)

- ? ? ? ? CIL-MCNN,用于Lane控制和接口逻辑

? ? ? ? 到CSI-2时钟Lane发送器的PPI接口信号有:

- ? ? ? ? TxDDRClkHS-Q(Input):高速传输DDR时钟(Quadrature)信号

- ? ? ? ? TxRequestHS(Input):高速传输Request信号。此信号高有效,用来让Lane模块开始传输HS时钟。

- ? ? ? ? TxReadyHS(Output):高速传输Ready信号。此信号高有效,用来指示时钟Lane在传输HS时钟。

- ? ? ? ? Shutdown(Input):关闭Lane模块。此信号高有效,用来强制Lane模块进入“shutdown”,禁用所有活动。所有线路驱动器,包括终结器(原文terminators,这里我不太了解,各位自行判断),都在Shutdown被置位的时候关闭。当Shutdown为高时,所有PPI输入信号都会被忽略,并且所有PPI输出都会被驱动到默认的无效状态。Shutdown是电平触发信号,不依赖于任何时钟。

- ? ? ? ? TxUlpmClk(Input):时钟Lane上的Transmit Ultra Low-Power Mode信号。此信号高有效,被置有效时会让时钟Lane模块进入Ultra Low-Power模式。Lane模块会保持这种极低功耗状态,直到TxUlpmClk被置为无效。

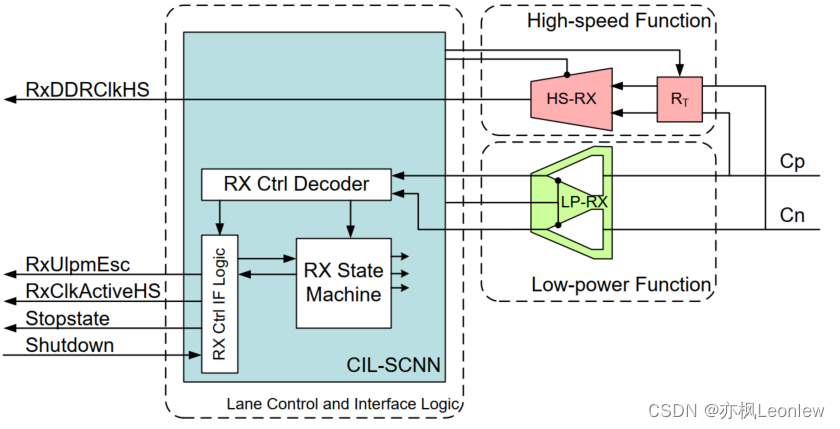

CSI-2时钟Lane接收器

?CSI-2 Clock Lane Receiver

? ? ? ? 构建CSI-2时钟Lane接收器的D-PHY模块有:

- ? ? ? ? LP-RX,用于低功耗功能(Low-power function)

- ? ? ? ? HS-RX,用于高速功能(High-speed function)

- ? ? ? ? CIL-MCNN,用于Lane控制和接口逻辑

? ? ? ? 到CSI-2时钟Lane接收器的PPI接口信号有:

- ? ? ? ? RxDDRClkHS(Output):高速接收DDR时钟信号,用来采样所有数据lane中的数据。

- ? ? ? ? RxClkActiveHS(Output):高速接收有效信号(High-Speed Reception Active)。此信号高有效,用来指示时钟Lane正在接收有效时钟。该信号是异步的。

- ? ? ? ? Stopstate(Output):Lane是否处于Stop状态。此信号高有效,用来指示Lane模块当前是否处于Stop状态。该信号是异步的。

- ? ? ? ??Shutdown(Input):关闭Lane模块。此信号高有效,用来强制Lane模块进入“shutdown”,禁用所有活动。所有线路驱动器,包括终结器(原文terminators,这里我不太了解,各位自行判断),都在Shutdown被置位的时候关闭。当Shutdown为高时,所有PPI输出都会被驱动到默认的无效状态。Shutdown是电平触发信号,不依赖于任何时钟。

- ? ? ? ? RxUlpmEsc(Output):Escape Ultra Low Power(Recieve)模式。此信号高有效,用来指示Lane模块是否已经进入到了Ultral Low Power模式。Lane模块会在此信号有效时保持这种模式,直到在Lane互连电路中检测到了一个Stop状态。

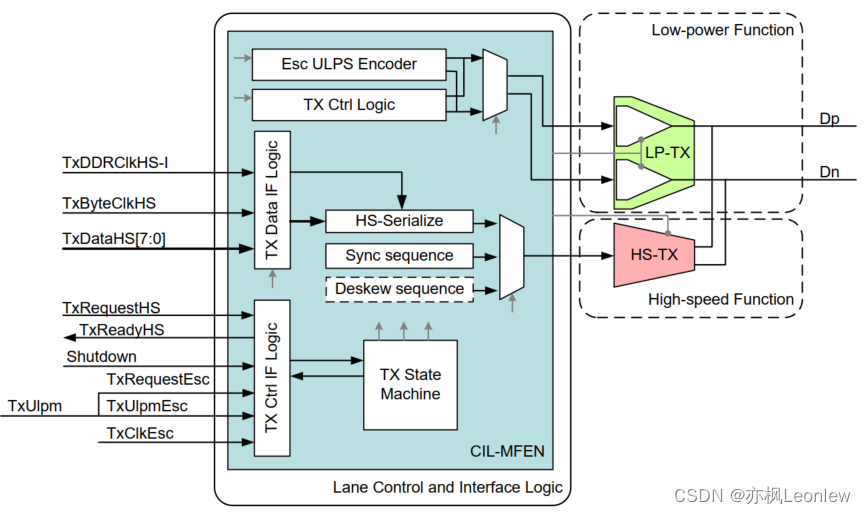

CSI-2数据Lane发送器

?CSI-2 Data Lane Transmitter

? ? ? ? 构建CSI-2数据Lane发送器的D-PHY模块有:

- ? ? ? ? LP-RX,用于低功耗功能(Low-power function)

- ? ? ? ? HS-RX,用于高速功能(High-speed function)

- ? ? ? ? CIL-MCNN,用于Lane控制和接口逻辑。对于可选的去斜(deskew)校准特性的支持,数据Lane发送器会传送一个去斜序列(deskew sequence)。去斜序列传输通过何种方式启用,超出了规范所讨论的范围。

? ? ? ? 到CSI-2数据Lane发送器的PPI接口信号有:

- ? ? ? ? TxDDRClkHS-I(Input):高速发送DDR时钟(同相位,in-phase)。

- ? ? ? ? TxByteClkHS(Input):高速发送Byte时钟。用来同步高速传输时钟域里的PPI信号。推荐用于发送的数据Lane模块共享一根TxByteClkHS信号。TxByteClkHS的频率必须是精确地HS bit速率的1/8。

- ? ? ? ? TxDataHS[7:0](Input):高速发送Data信号。要发送的8 bit高速数据。连接到TxDataHS[0]的信号首先被发送。数据在TxByteClkHS的上升沿的时候被寄存。

- ? ? ? ? TxRequestHS(Input):高速发送Request信号。TxRequestHS的一次低到高的转换会让Lane模块发起一个Start-of-Transmission序列。TxRequestHS一次高到低的转换会让Lane模块发起一个End-of-Transmission序列。此信号高有效,高电平时也能指示协议层正在驱动着TxByteDataHS上要发送的合法数据。在同一个TxByteClkHS时钟的上升沿上,当TxRequestHS和TxReadyHS同时有效时,Lane模块会接受(accept)数据。协议总是在TxRequestHS有效的时候提供合法的发送数据。一旦被置为有效,TxRequestHS会保持高电平,直到所有数据都被接受(accpet)了。

- ? ? ? ? TxReadyHS(Output):高速发送Ready信号。此信号高有效,用来指示TxDataHS被Lane模块所接受(accepted)即将会被串行发送出去。TxReadyHS在TxByteClkHS的上升沿有效。在TxReadyHS有效期间,合法的数据要被提供。

- ? ? ? ? Shutown(Input):关闭Lane模块。此信号高有效,用来强制Lane模块进入“shutdown”,禁用所有活动。所有线路驱动器,包括终结器(原文terminators,这里我不太了解,各位自行判断),都在Shutdown被置位的时候关闭。当Shutdown为高时,所有PPI输出都会被驱动到默认的无效状态。Shutdown是电平触发信号,不依赖于任何时钟。

- ? ? ? ? TxUlpmEsc(Input):Escape Mode Transmit Unltra Low Power。此信号高有效,和TxRequestEsc信号一起被置位,让Lane模块进入极低功耗(Ultra Low Power)模式。Lane模块会保持这种模式,直到TxRequestEsc被置为无效。

- ????????TxRequestEsc(Input):此信号高有效,和TxUlpmEsc一起被置位,用来请求进入到Escape Mode。一旦进入Esacape Mode, Lane会一直处于Escape Mode,直到TxRequestEsc被置为无效。TxRequestEsc只会在TxRequestHS为低的时候,被协议置位。

- ? ? ? ? TxClkEsc(Input):Escape Mode Transmit Clock。这个时钟直接被用于产生escape序列。这个时钟的周期决定了低功耗信号的符号时间。

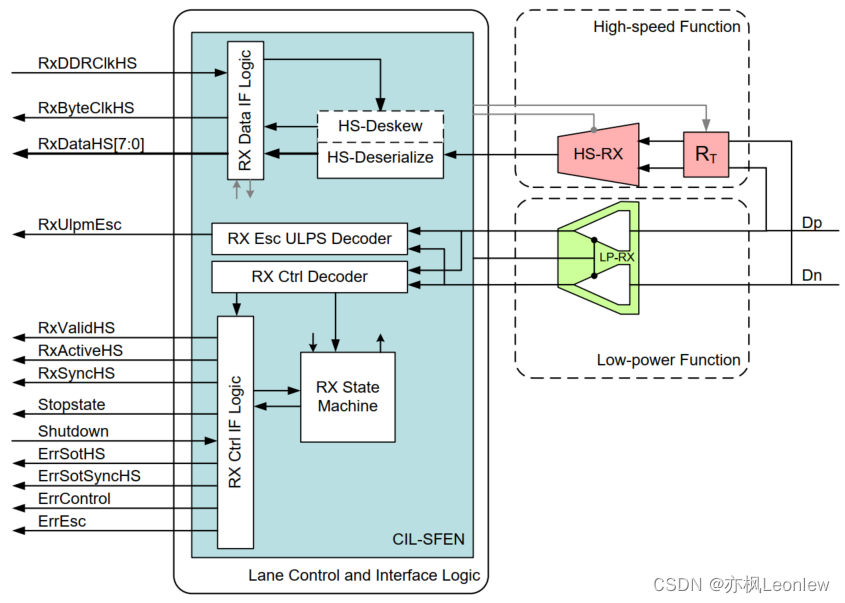

CSI-2数据Lane接收器

CSI-2 Data Lane Receiver?

?构建CSI-2数据Lane接收器的D-PHY模块有:

- ? ? ? ? LP-RX,用于低功耗功能(Low-power function)

- ? ? ? ? HS-RX,用于高速功能(High-speed function)

- ? ? ? ? CIL-MCNN,用于Lane控制和接口逻辑。可选的去斜(deskew)校准功能,支持数据Lane接收器检测被发送的去斜校准模式(pattern),并且执行和RxDDRClkHS时钟相关的数据去斜优化。

? 到CSI-2数据Lane接收器的PPI接口信号有:

????????RxDDRClkHS(Input):高速接收DDR时钟信号,用来采样所有数据lane中的数据。这个信号由CSI-2时钟Lane接收器所提供。

? ? ? ? RxByteClkHS(Output):高速接收Byte时钟信号。此信号用来同步在高速接收时钟域内的信号。RxByteClkHS信号是通过接收到的RxDDRClkHS整除来产生的。

? ? ? ? RxDataHS[7:0](Output):高速接收Data信号。Lane模块接收的8 bit高速数据。连接到RxDataHS[0]的信号首先被接收。数据在RxByteClkHS上升沿的时候被传输。

? ? ? ? RxValidHS(Output):高速接收Data Valid信号。此信号高有效,用来指示Lane模块正在驱动着RxDataHS输出上的合法数据到协议层。没有“RxReadyHS”信号,协议层会在RxValidHS有效的时候,在每一个RxByteClkHS的上升沿的时候去抓取RxDataHS信号。协议没有提供降低接收数据速度的功能(throttle)。

? ? ? ? RxActiveHS(Output): 高速接收Active信号。此信号高有效,用来指示Lane模块正在从Lane互联电路中接收高速传输信息。

? ? ? ? RxSyncHS(Output):接收器同步Observed信号。此信号高有效,用来指示Lane模块已经看到了一个合适的同步事件。在一个典型的高速传输中,当RxActiveHS首次被置位时,一次高速传输的开始点,RxSyncHS会保持高电平,时间是一个RxByteClkHS周期。这个信号如果丢失,会用ErrSotSyncHS来报告。

? ? ? ? RxUlpmEsc(Output):Escape Ultra Low Power (Receive)模式。此信号高有效,置位后用来指示Lane模块已经进入了极低功耗模式。Lane模块会保持在这种模式中,此时RxUlpmEsc有效,直到在Lane互联电路上检测到了一个Stop状态。

? ? ? ? Stopstate(Output):Lane处于Stop状态。此信号高有效,用来指示Lane模块正处于Stop状态。此信号是异步的。

? ? ? ? Shutdown(Input):关闭Lane模块。此信号高有效,用来强制Lane模块进入“shutdown”,禁用所有活动。所有线路驱动器,包括终结器(原文terminators,这里我不太了解,各位自行判断),都在Shutdown被置位的时候关闭。当Shutdown为高时,所有PPI输出都会被驱动到默认的无效状态。Shutdown是电平触发信号,不依赖于任何时钟。

? ? ? ? ErrSotHS(Output):Start-of-Transmission(SoT)Error信号。如果高速SoT前导序列出错,但此时仍然能够达到适当的同步,这个错误信号置位的时间为RxByteClkHS的一个周期。这种错误被认为是前导序列的一个“软错误”,载荷数据的信任度会降低。

? ? ? ? ErrSotSyncHS(Output):Start-of-Transmission同步Error信号。如果高速SoT前导序列出错,并且不能期望得到一个适当的同步。这个错误信号置位的时间为RxByteClkHS的一个周期。

? ? ? ? ErrControl(Output):控制错误。这个信号在一个错误的line state序列被检测到的时候置位。

? ? ? ? ErrEsc(Output): Escape Entry Error。如果接收到了一个无法识别的escape entry命令,这个信号会被置位,并且会保持为高,直到下一个line state里的变化发生。接收器支持的escape entry命令只有ULPS。