应用概述

本文概述了如何在系统中使用RFSoC 射频数据转换器的多块同步功能。

文章目录

多块同步(MTS)

RFSoC 具有非常灵活的时钟和数据接口,可在同一器件中实现多种不同的应用。 每个 RF-ADC/RF-DAC 块都有自己独立的时钟和数据基础设施,允许每个块以单独的采样率和 PL 数据字宽驱动。 单个 tile 中的转换器共享时钟和数据基础设施,因此采样率和延迟是固定的。 但是,某些应用可能需要多个块,甚至多个RFSoC 才能一起使用。 对于这些应用程序,跨图块匹配转换器延迟至关重要。 多块同步 (MTS) 功能可用于实现相对和确定的多块和多设备对齐。

详细说明

在任何具有多个独立转换器和时钟结构的系统中,都有几个潜在的延迟不确定性来源,例如时钟分频器相位、NCO 相位、FIFO 延迟、时钟偏移和数据偏移。 分立转换器已标准化 JESD204B SYSREF 方案的同步使用,因此,RFSoC 已使用 SYSREF 实施了一个互补的简化方案。

RFSoC 中的转换器集成消除了用于数据通信的串行收发器链路。 然而,为了为 PL 设计提供灵活的时钟和数据字数,每个 RF-ADC 和 RF-DAC 都包含独立的FIFO。 这些 FIFO 允许在 PL 时钟域和转换器采样时钟域之间传输数据,但这会导致不确定的延迟,也必须使用 SYSREF 进行测量和校正。

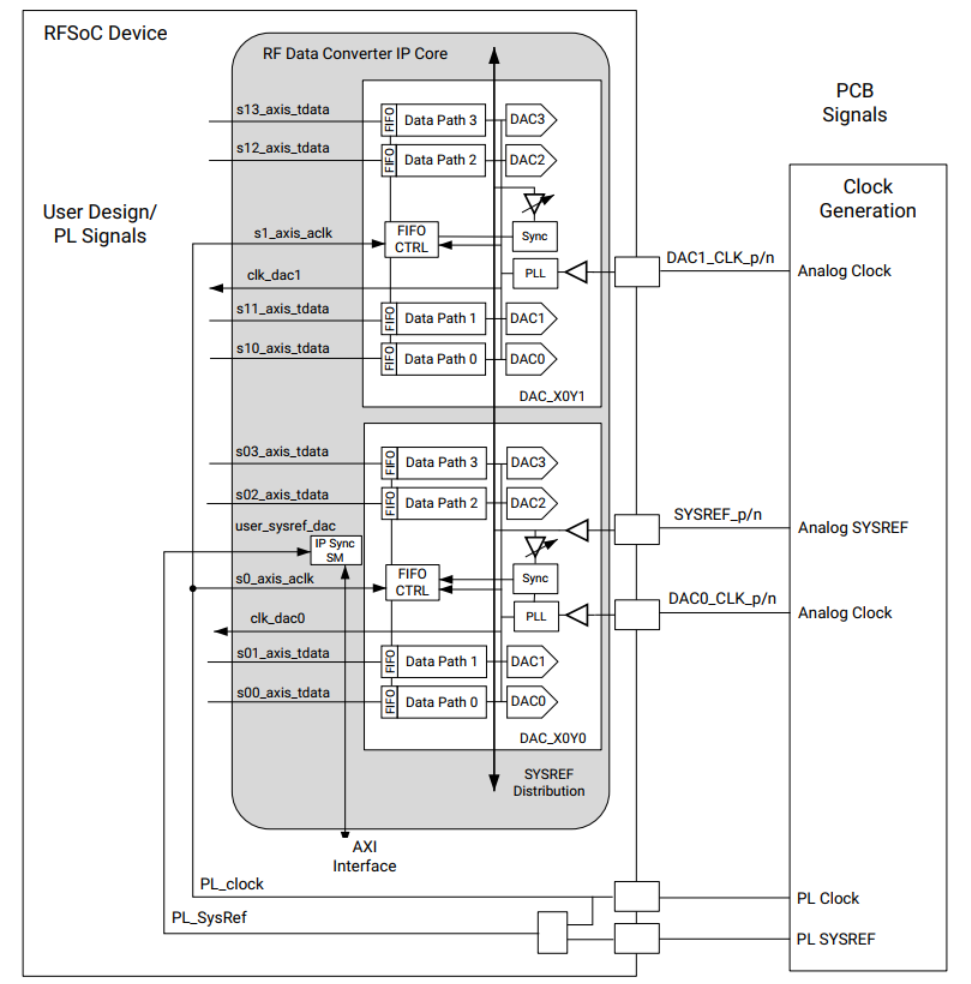

RFSoC RF 数据转换器和 RFdc 驱动程序 API 解决方案提供了一种易于使用的集成方式来同步给定设备中的每个 Tile。 上图显示了一个示例系统,其中包含要同步的多个图块。 以下适用于上图:

- 该方法同样适用于任何数量的RF-ADC 或RF-DAC 块。

- 每个器件的单个模拟SYSREF 输入在内部分配给所有RF-ADC 和RF-DAC。

- 每个块都有一个内部模拟SYSREF 延迟调整,通过允许在片上优化SYSREF 建立/保持时间来降低PCB 要求。

- 每个区块有一个模拟时钟输入; 这些显示为 DAC0_CLK 和 DAC1_CLK。

- PL 用户设计和块的公共时钟显示为PL 时钟(PL_clock)。

- PL 的SYSREF 显示为PL SYSREF (PL_SysRef)。 如果 RF-ADC (user_sysref_adc) 和 RF-DAC (user_sysref_dac) 都在同步组中,则有一个单独的 PL SYSREF。

- 同步状态机包含在内核中,它与RFdc 驱动程序API 一起实现同步解决方案。

- 对于RF-DAC 多块同步(MTS),RF-DAC 块主控始终用作所有其他RF-DAC 块同步的参考块。 因此,RF-DAC tile 0 必须是用于 RF-DAC 的 MTS 应用中的活动 tile。

- 同样,RF-ADC 主模块始终用作所有其他 RF-ADC 模块同步的参考模块。 因此,RF-ADC tile 0 必须是用于 RF-ADC 的 MTS 应用中的活动 tile。

- 如果需要禁用 SYSREF 链中存在的块,则应在第 1 代和第 2 代设备中将其断电至上电序列中的状态 3 和第 3 代设备中的状态 6。 这可确保 SYSREF 仍沿链传播。

- 在PCB 设计期间应考虑并调整每个转换器的封装flight时间偏差。

同步步骤

在高层次上,执行的同步步骤如下:

-

启用所有时钟和 SYSREF 发生器:模拟和数字时钟都必须在同步开始之前运行并锁定。对时钟的任何更改都需要重新同步。

-

SYSREF 模拟捕捉:通过自动调整用于建立/保持的内部 SYSREF 可编程延迟,确保安全地捕获 SYSREF。 这是针对每个图块完成的,并且需要多个周期性 SYSREF 脉冲,以便可以确定最佳延迟值。 因此,MTS 进程需要一个周期性的 SYSREF 时钟。

-

时钟分频器复位:当所有块都安全地捕获 SYSREF 时,随后的 SYSREF 边沿用于同步所有分频器相位。

-

FIFO 延迟测量和调整:模拟 SYSREF 和 PL_Sysref 信号用于测量通过每个 FIFO 的延迟。使用所有图块的测量值来调整延迟,使其匹配。

-

将数字特征与 SYSREF 动态更新事件同步:当启用会影响瓦片对齐的数字特征时,必须使用 SYSREF 动态更新事件初始化/更新相关的数字功能块。 这些数字特性包括精细混频器/NCO、QMC 和粗延迟。

步骤 2、3 和 4 由 IP 内核和 RFdc 驱动程序 API 自动处理。

当 API 用于修改影响 FIFO 时钟速率或宽度的数字设置时,必须重新启动同步过程。 在 MTS 过程中涉及的任何瓦片断电或重新启动后,同步过程也必须重新启动。

确定性多图块同步 API 使用

多片API 使用保证了每组中图块之间的对齐。 但是,通过 Tile 的总延迟可能会因与 FIFO 读取时钟周期相关的字数除以读取字数而变化。 对于总延迟必须恒定的应用程序,可以启用 API 中的 Target_Latency 设置。 此设置将所有小于目标的延迟调整为目标值; 任何大于目标的测量值都会导致错误消息,而 MTS 仍然通过忽略 Target_Latency 来对齐所有瓦片。

为防止出现此错误,必须首先通过运行 XRFdc_MultiConverter_Sync 并将目标设置为 -1 来确定用户 FIFO 和 tile 配置的 Target_Latency 值。 返回的延迟值(加上一些余量)必须设置为未来运行的目标值。

要应用的余量值是根据采样时钟指定的。 对于 RF-ADC 块,该值必须是 FIFO 读取字数乘以抽取因子的倍数,对于 RF-DAC 块,该值可以是常数 16。设置目标延迟的示例如下 如下:

XRFdc_MultiConverter_Init (&DAC_Sync_Config, 0, 0, 0); // Initialize DAC MTS Settings

DAC_Sync_Config.Tiles = 0x3; // Tiles to sync bit-mask: DAC tiles 0 and 1

DAC_Sync_Config.Target_Latency = 296; // Target latency - measured value (280 + 16 margin)

SYSREF 信号要求

SYSREF 信号是系统的时序参考,因此必须正确处理以确保它不会降低同步性能。 该信号具有以下要求。

-

SYSREF 信号必须是高质量、自由运行、低抖动的方波,以使其能够被模拟采样时钟一致地捕获。

-

SYSREF 频率必须满足以下要求:

-

如果同步具有不同采样频率的 RF-ADC 和 RF-DAC 块,则频率必须是以下的整数约数:GCD(DAC_Sample_Rate/16, ADC_Sample_Rate/16)

-

SYSREF 还必须是对其进行采样的所有 PL 时钟的整数约数。 这是为了确保始终同步采样周期性 SYSREF。

-

小于 10MHz

-

-

SYSREF 在传递给内核之前必须被 PL 安全捕获: PL_SysRef 到 PL_clock 的建立/保持必须作为用户设计的一部分进行处理。可以使用 PCB 上的时钟生成来促进这一点。

-

模拟 SYSREF 和 PL SYSREF 必须是相同的频率并且具有恒定的相位关系。 如果需要确定性延迟,模拟 SYSREF 和 PL SYSREF 必须在复位到复位周期内保持相同的相位差。

-

对于 MTS 同步,包括分频器相位同步和 FIFO 延迟同步,模拟 SYSREF 和 PL SYSREF 在 MTS 过程期间必须是连续时钟。 它可以是交流耦合或直流耦合。SYSREF 信号可以在 MTS 程序完成后关闭。 请注意,它们应该在 MTS 函数调用之前打开并稳定下来。

-

如果模拟 SYSREF 用于跨多个RFSoC 同步 DUC/DDC 混频器 NCO 的相位,则它必须进行直流耦合,并具有生成单个或多个脉冲波形的能力。

SYSREF 频率计算示例

A D C S a m p l e R a t e = 3.93216 G H z D A C S a m p l e R a t e = 4.91520 G H z G C D ( A D C S a m p l e R a t e / 16 , D A C S a m p l e R a t e / 16 ) = 61.44 M H z I n t e g e r ? S u b ? ? ? M u l t i p l e ? A N D ? < ? 10 ? M H z ? = ? 7.68 M H z ADC_{SampleRate} = 3.93216 GHz\\ DAC_{SampleRate} = 4.91520 GHz\\ GCD(ADC_{SampleRate}/16 , DAC_{SampleRate}/16) = 61.44 MHz\\ Integer\ Sub\ -\ Multiple\ AND\ <\ 10\ MHz\ =\ 7.68 MHz ADCSampleRate?=3.93216GHzDACSampleRate?=4.91520GHzGCD(ADCSampleRate?/16,DACSampleRate?/16)=61.44MHzInteger?Sub???Multiple?AND?<?10?MHz?=?7.68MHz

这些等式生成满足 RFADC/ 要求的 SYSREF 频率 RF-DAC 内部时钟。 SYSREF 信号也被 PL 同步捕获; 因此,SYSREF 频率也必须是驱动 IP 接口的 PL 时钟或与 PL SYSREF 交互的任何其他时钟的约数。

PL SYSREF 捕获

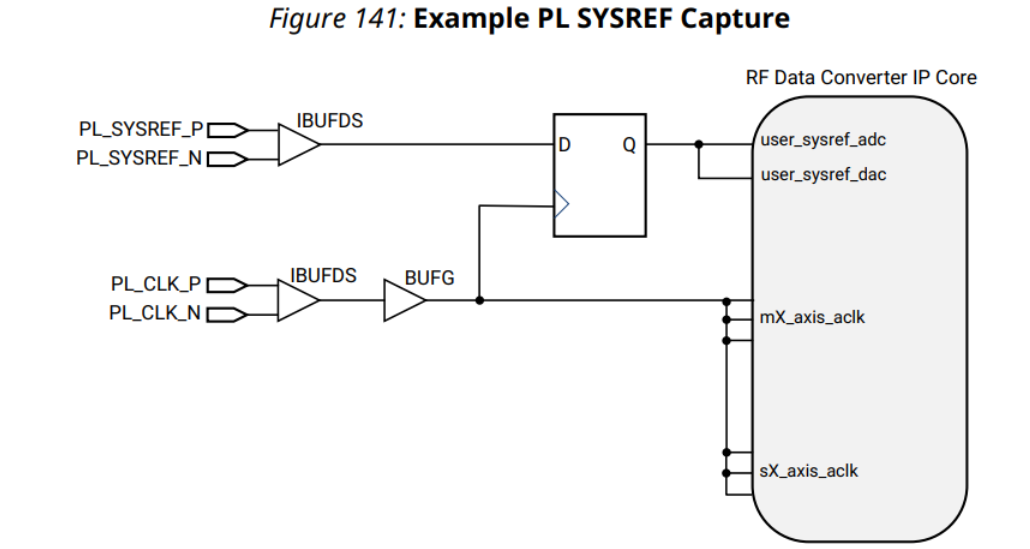

为保证 Tile 之间的有效同步,在器件逻辑中可靠地捕获 PL SYSREF 输入非常重要。 PL SYSREF 和 PL 时钟输入必须是符合器件时钟和存储规则的差分信号。 PL 时钟输入必须在专用时钟引脚上。 RF 数据转换器内核的 AXI4-Stream 时钟必须从 PL 时钟输入生成,而不是从内核本身的时钟输出生成。 下图显示了一个示例 PL SYSREF 捕获电路,其中 RF-ADC 和 RF-DAC 以相同的 AXI4-Stream 时钟频率运行。

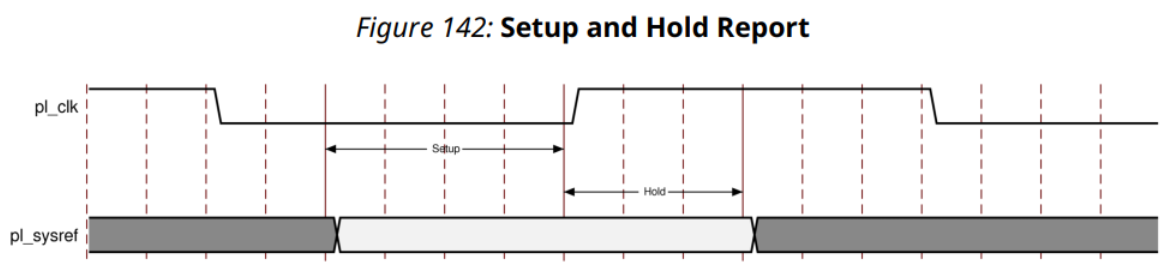

可在 Vivado IDE 中使用 report_datasheet 命令计算器件引脚上 PL SYSREF 输入所需的建立和保持时间。 下图显示了具有 500 MHz PL 时钟的 -1 速度等级器件的示例计算。

| Reference Clock | Input Port | Setup (ns) to Clk (Edge) | Hold (ns) to Clk (Edge) |

|---|---|---|---|

| pl_clk | pl_sysref_n | 0.965 ? | 0.285 ? |

| pl_clk | pl_sysref_p | 0.965 ? | 0.285 ? |

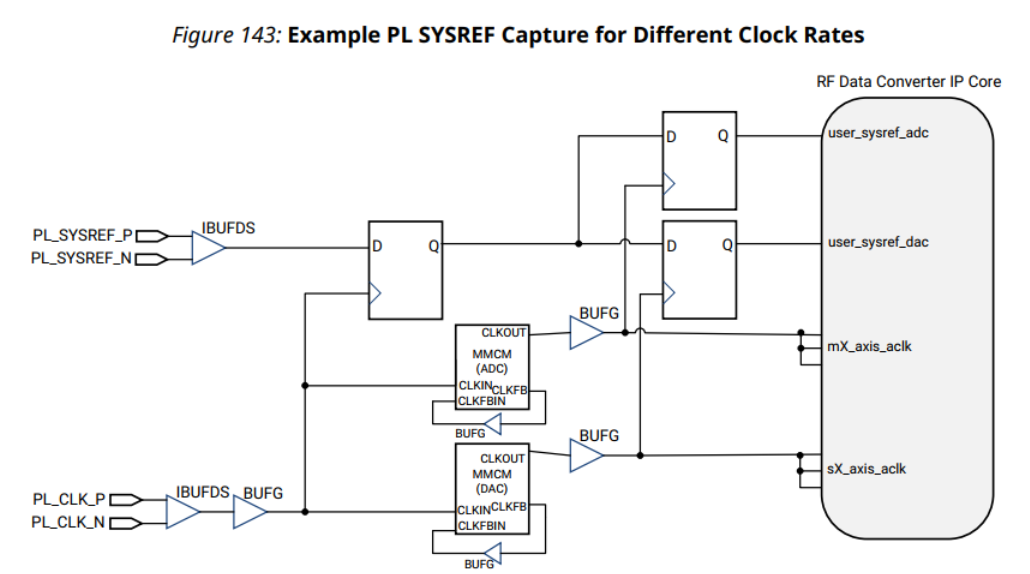

在上面的示例中,PL SYSREF 必须延迟到至少在 PL 时钟的上升沿之后 0.285 ns 到达,以确保满足保持要求。 对于每个新设计,或当设计发生更改时,应运行 report_datasheet 步骤以重新评估设置和保持要求。 如果 RF-ADC 和 RF-DAC 在不同的 AXI4-Stream 时钟频率下工作,则可以使用下图所示的电路来捕获 PL SYSREF。

在这里,时钟网络去偏斜 MMCM 用于将 PL 时钟的频率合成到所需的速率。 如果需要跨多个芯片的 MTS,PL 时钟必须是 RF-ADC 和 RF-DAC AXI4-Stream 时钟的公倍数或约数(前提是它与整数值相关(例如,1/8、1 /4、1/2、1x、2x、4x、8x))。 此外,PL SYSREF 频率必须是系统中所有时钟的公共约数。

数字特征同步

同步完成后,时钟的公共状态在所有瓦片之间共享。 使用动态更新事件的数字数据路径功能也可以使用相同的同步基础设施。这方面的一个例子是构成 DDC 和 DUC 链中精细混频器功能的 NCO。NCO 设置可以使用 SYSREF 在多个块和多个RFSoC 上同时应用。 每个 NCO 都支持频率和相位的动态设置,并将更改应用于 SYSREF 或其他更新事件。

同样,有一个选项可以在 SYSREF 或其他更新事件上重置 NCO 的相位。对于单块同步,块事件可用于同步块内的 NCO。对于多图块同步,应使用 SYSREF 事件。

模拟同步

模拟 SYSREF 捕获/接收

RF-DAC tile 0 中的模拟 SYSREF 接收器设计用于捕获输入引脚的上升沿并生成同步脉冲,该同步脉冲以平衡的方式在内部分配给所有 RF-DAC 和 RF - ADC 用于 MTS 功能和动态更新事件触发功能的瓦片。MTS 功能需要一个连续的模拟 SYSREF 时钟,该时钟在 MTS 程序调用期间生成连续的同步脉冲序列。 另一方面,动态更新事件触发功能仅使用事件触发后检测到的第一个上升沿(请求事件更新)。 使用相应的 API 函数调用完成的布防应该在没有看到任何同步脉冲生成的情况下完成。否则,一些块将被锁定在新的更新值中,而其他块则不会。

因此,事件的排序和模拟 SYSREF 波形必须遵循以下指导,才能正确操作这两个功能中的每一个。 为简化某些时钟设计的实现,API 函数调用 XRFdc_MTS_Sysref_Config 可用于启用和禁用模拟 SYSREF 接收器,从而提供一种使 SYSREF 同步脉冲间隙的方法。 请注意,此 API 函数不是定时函数,因此不容易跨多个设备同步。 因此,API XRFdc_MTS_Sysref_Config 并非仅用于在多个设备之间同步 SYSREF 的第一个上升沿。

模拟 SYSREF 交流和直流耦合

模拟 SYSREF 支持交流和直流耦合。 在交流耦合模式下,模拟 SYSREF 接收器在输出模拟 SYSREF 时钟的关闭状态和时钟的初始开启期间对噪声毛刺很敏感。 在这些时间期间,由于毛刺,接收器的不可预测性会产生同步脉冲。 因此,您必须在启用 SYSREF 接收器之前让时钟稳定下来,以避免错误触发事件。

如果模拟 SYSREF 发送器在关闭时保持在已知的逻辑状态,则在直流耦合模式下运行有可能避免这些毛刺状态。 具有脉冲功能的时钟输出,例如 TI LMK04826 时钟器件,能够按需生成可预测的脉冲。 如果需要跨多个设备使用模拟 SYSREF 的动态更新事件,则需要这样做; 所有准备更新的设备都需要相同的上升沿。

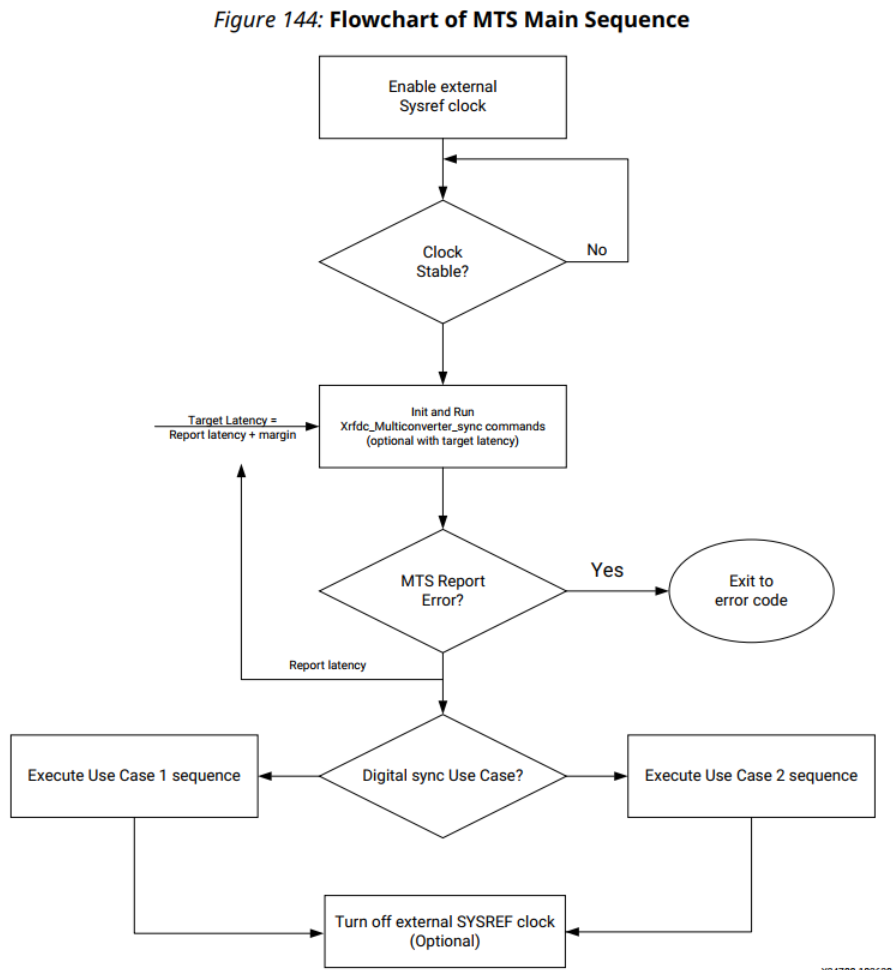

MTS Sequencing

为 AC 或 DC 耦合的单个或多个设备执行同步的主序列。以下流程图显示了执行同步的主序列。

以下步骤更详细地反映了主序列流程图并提供了 API 使用示例:

-

在连续时钟模式下启用 PL SYSREF 和模拟 SYSREF 时钟。

-

等待时钟稳定,通常以微秒 (μs) 为单位,具体取决于所使用的时钟设备。

-

如果不需要或未知确定性延迟,则以目标延迟运行 RF-ADC 和/或 RF-DAC MTS API 函数,并将目标延迟设置为 -1。 下面给出了一个同步 DAC tile 0 和 1 的示例:

int status_dac;

XRFdc_MultiConverter_Sync_Config DAC_Sync_Config; // Declare DAC MTS Settings struct

XRFdc_MultiConverter_Init (&DAC_Sync_Config, 0, 0, 0); // Initialize DAC MTS Settings

DAC_Sync_Config.Tiles = 0x3; // Tiles to sync bit-mask: DAC tiles 0 and 1

DAC_Sync_Config.Target_Latency = 296; // Target latency = 280 (measured value) + 16 (margin), set to -1 if unknown

status_dac=XRFdc_Multiconverter_Sync(RFdcInstPtr,XRFDC_DAC_TILE,&DAC_Sync_Config); // Run Multi-Tile-Sync for the DAC Group

- 等待API返回值完成。

if (status_dac!=XRFDC_MTS_OK) {Execute error code;} and Report details on synchronization (optional)

for(i=0; i<4; i++) {

if((1<<i)&DAC_Sync_Config.Tiles) {

XRFdc_GetInterpolationFactor(RFdcInstPtr, i, 0, &factor);

xil_printf(" DAC%d: Latency(T1) =%3d, Adjusted Delay (T%d) =%3d\n", i, DAC_Sync_Config.Latency[i], factor, DAC_Sync_Config.Offset[i]);

}

}

-

根据用例同步数字功能(混频器设置、NCO 相位复位、QMC 和/或粗略延迟):

-

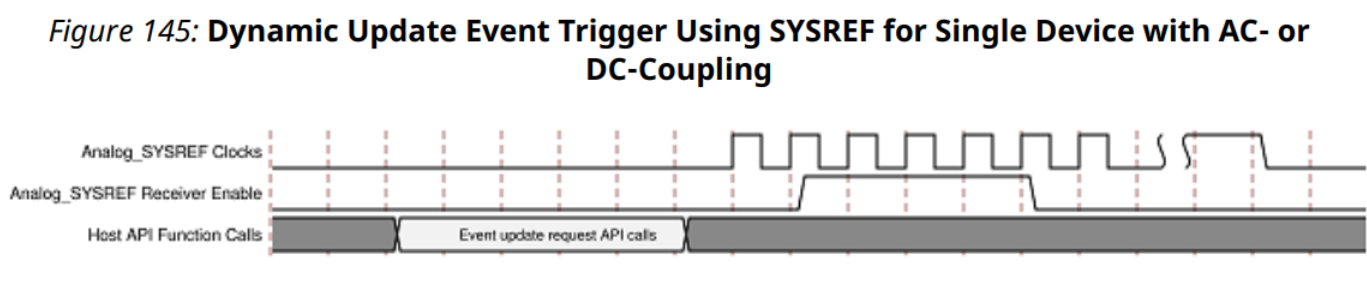

用例 1:具有交流或直流耦合的单器件 SYSREF。

-

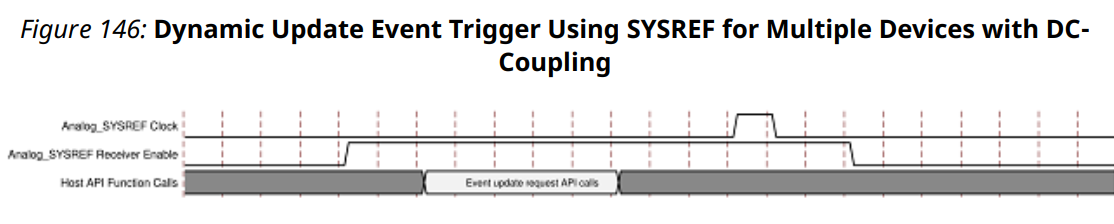

用例2:具有直流耦合的多个设备SYSREF。

-

-

可以禁用外部 PL SYSREF 和模拟 SYSREF 时钟(可选)。

用例 1:使用带有 AC 或 DC 耦合的单个设备的 SYSREF 同步数字功能

- 使用 API 命令禁用模拟 SYSREF 接收器。

SysRefEnable = 0

status_dac|=XRFdc_MTS_Sysref_Config(&InstancePtr, &DACSyncConfigPtr,&ADCSyncConfigPtr, SysRefEnable)

-

启动混频器设置、NCO 相位复位、QMC 和/或粗略延迟。

XRFdc_Mixer_Settings Mixer_Settings; // declare mixer settings struct u32 Type = XRFDC_DAC_TILE; u32 Tile_Id ; u32 Block_Id ; u32 Mixer_Settings.EventSource = XRFDC_EVNT_SRC_SYSREF;// it is assumed other Mixer settings have been previously assigned in the user code for (Tile_Id = 0; Tile_Id < 4; Tile_Id++ ) { for (Block_Id = 0; Block_Id < 4; Block_Id++ ) { XRFdc_SetMixerSettings(&RFdcInst, Type, Tile_Id, Block_Id,&Mixer_Settings); status_dac |= XRFdc_ResetNCOPhase(&RFdcInst,Type,Tile_Id,Block_Id); //note that Coarse mixer and QMC could also be part of this for loop. } } -

等待 API 调用成功返回,确保所有寄存器写入均已完成。

if (status_dac!=XST_SUCCESS) {Execute error code;}

- 在连续模式下启用模拟 SYSREF 时钟并确保该时钟稳定。

- 使用 API 命令启用模拟 SYSREF 接收器。

SysRefEnable = 1

status_dac|=XRFdc_MTS_Sysref_Config(&InstancePtr, &DACSyncConfigPtr, &ADCSyncConfigPtr, SysRefEnable)

- 等待足够长的时间以确保检测到上升沿,此时将开始更新。

- 使用 API 命令禁用模拟 SYSREF 接收器。

SysRefEnable = 0

status_dac|=XRFdc_MTS_Sysref_Config(&InstancePtr, &DACSyncConfigPtr, &ADCSyncConfigPtr, SysRefEnable)

- 禁用外部模拟 SYSREF 时钟(可选)。

用例 2:使用带有直流耦合的多个器件的 SYSREF 同步数字功能

需要直流耦合和脉冲 SYSREF 时钟。

-

将时钟发生器设备编程为使用脉冲 SYSREF 模式; 置于空闲状态(不产生脉冲)。

-

等待模拟时钟稳定。

-

为所有涉及的设备启用模拟 SYSREF 接收器(此时应该没有检测到脉冲)。

// Execute XRFdc_MTS_Sysref_Config on all devices (for loop is pseudo code). for (Device_Id = 0; Device_Id < NumberOfDevices; Device_Id++ ) { SysRefEnable = 1 status_dac|=XRFdc_MTS_Sysref_Config(&InstancePtr, &DACSyncConfigPtr,&ADCSyncConfigPtr, SysRefEnable) } -

在所有设备上执行命令以启动混频器设置、NCO 相位重置、QMC 和/或粗略延迟(for 循环是伪代码)。

for (Device_Id = 0; Device_Id < NumberOfDevices; Device_Id++ ) {

status_dac |=XRFdc_SetMixerSettings(&RFdcInst, Type, Tile_Id, Block_Id,&Mixer_Settings);

status_dac |= XRFdc_ResetNCOPhase(&RFdcInst,Type, Tile_Id,Block_Id);

//note that Coarse mixer and QMC could also be part of this for loop.

}

- 等待 API 调用成功返回,以确保所有寄存器写入都已完成。

if (status_dac!=XST_SUCCESS) {Execute error code;}

-

从模拟 SYSREF 向所有相关设备发出一个同步脉冲。

-

等待足够长的时间以确保检测到上升沿; 此时更新开始。

-

使用 API 命令禁用模拟 SYSREF 接收器。

for (Device_Id = 0; Device_Id < NumberOfDevices; Device_Id++ ) {

SysRefEnable = 0

status_dac|=XRFdc_MTS_Sysref_Config(&InstancePtr, &DACSyncConfigPtr,&ADCSyncConfigPtr, SysRefEnable)

}

使用实时信号门控模拟 SYSREF(第 3 代)

在前面的 MTS 实现部分中,某些 API 用于门控模拟 SYSREF 信号,或者当某些动态事件(即 NCO 频率)时需要一次性模拟 SYSREF 信号 需要同时更新。

在第 3 代中,引入了两组实时信号 dacX_sysref_gate 和 adcX_sysref_gate,用于片上模拟 SYSREF 门控。对于单芯片用例,这些实时信号可以替代 SYSREF 门控 API。 对于跨多个 RFSoC 的 MTS,所有相关的 SYSREF 门控信号都应首先断言以门控模拟 SYSREF 输入,等待所有更新被启用,然后同时解除断言。 因此,模拟 SYSREF 的下一个上升沿将触发准备好的动态更新。 在此设计中,所有相关的 SYSREF 门控信号必须在RFSoC 的内部和外部进行良好对齐。 通过这种设计,SYSREF 时钟可以是交流或直流耦合的。