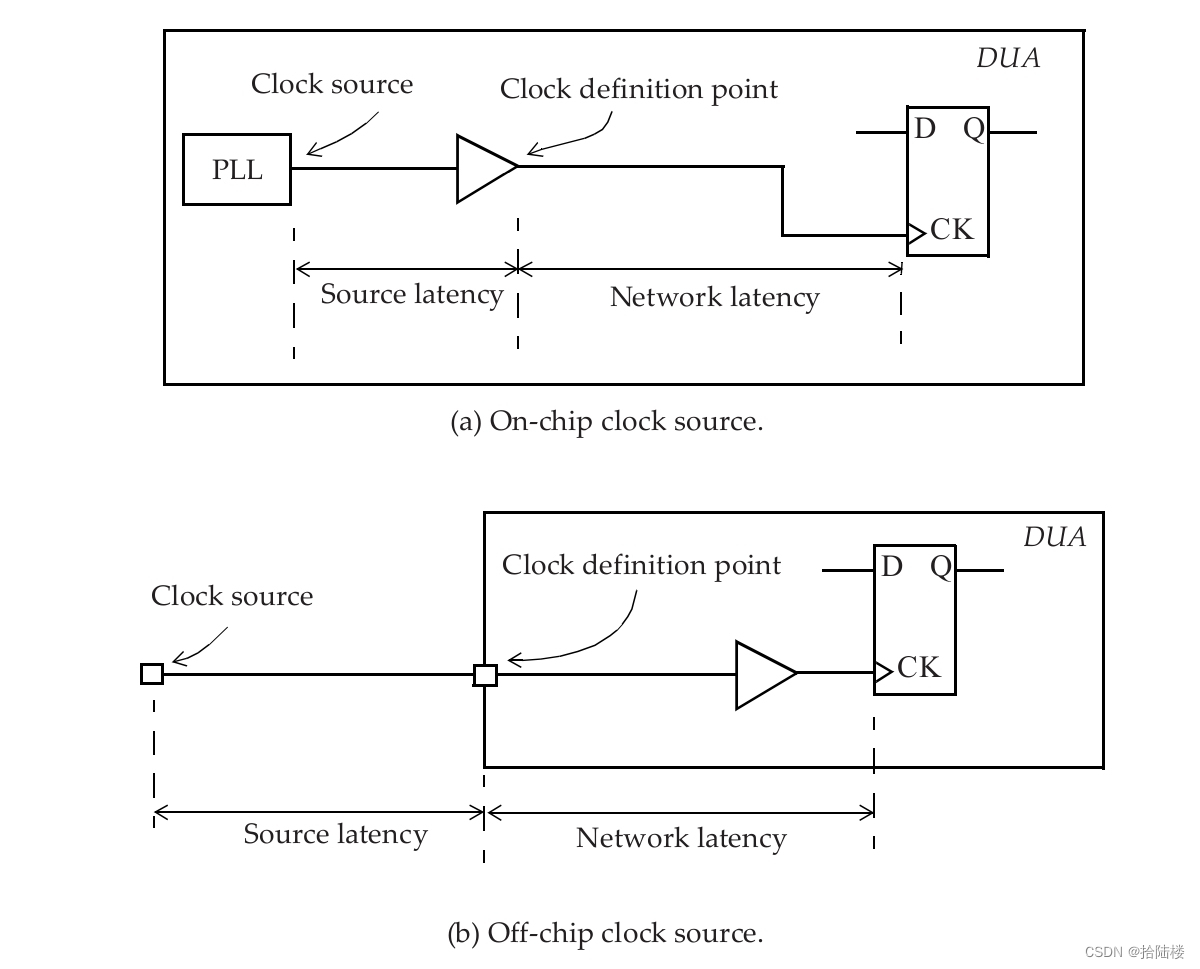

clock latency分为两类:source latency和network latency,其中network latency指的是时钟定义点(create_clock)到flip flops的clock pin的延迟,而source latency(也叫insertion delay)是从时钟源头到时钟定义点的延迟,source latency可以是片上(on-chip)延迟,也可以是片外(off_chip)延迟,如下图。flip flops的clock pin上总的clock latency就是source latency与network latency的和。

source latency与network latency一个很重要的区别在于,一但经过了时钟树综合(CTS)构建了真实的时钟树,使用set_clock_latency定义network latency就是可以忽略的了,但是即便经过了时钟树综合,source latency也是依然存在的,此时,clock latency就等于source latency加从时钟定义点到flip flops clock pin的真实延迟。

示例:

#在CTS前指定network latency

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

#指定source latency

set_clock_latency 0.8 -source [get_clocks CLK_CFG]

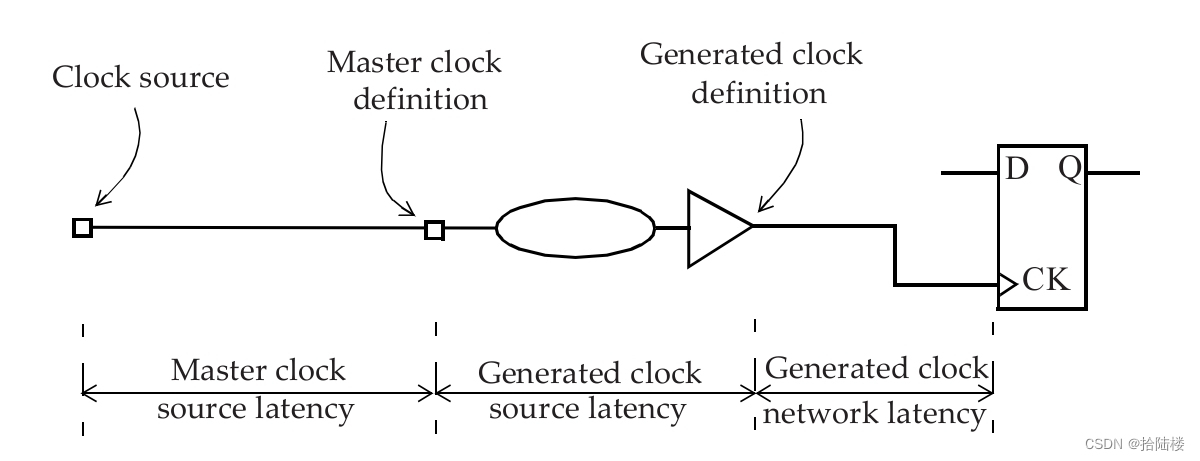

对于generate clock而言,source latency指的是它的master clock时钟定义点到generate clock时钟定义点的延迟,一个flip flops的clock pin上总的clock latency等于master clock的source latency加generate clock的source latency加generate clock的network latency,如下图。

?一个generate clock可以把另一个generate clock当做它的源时钟,也就是说,存在有generate clock的generate clock,但是,一个generate clock只能走一个master clock。

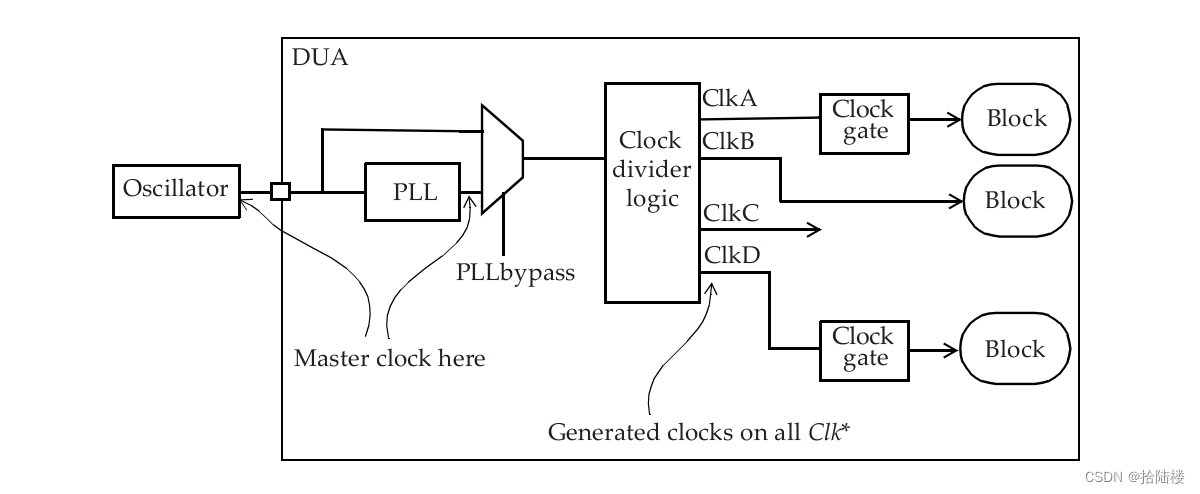

如下图是一个典型的generate clock使用场景。

晶振(oscillator)位于片外,生成一个低频时钟,该时钟被芯片上PLL当做参考时钟生成了一个高频时钟,这个PLL时钟输入到一个时钟分频电路中,产生我们需要么时钟。

上图中能够看到一些时钟的分支上存在时钟门控(clock gate),它被用来关闭设计中不活跃部分的时钟分支,可以在需要时节省功耗。PLL也在输出端连接了一个多路选择器,以便在需要时跳过PLL。

在参考时钟进入芯片的输入引脚,为参考时钟定义了一个master clock,第二个master clock定义在PLL的输出端,这两个clock没有相位关系,所以第二个时钟不是第一个时钟的generate clock,而多数情况下,所有分频电路产生的generate clock的master clock都是PLL输出的时钟。

?