介绍

在ubuntu下利用.sh脚本语言,实现VScode +GTwave +xvlog联调

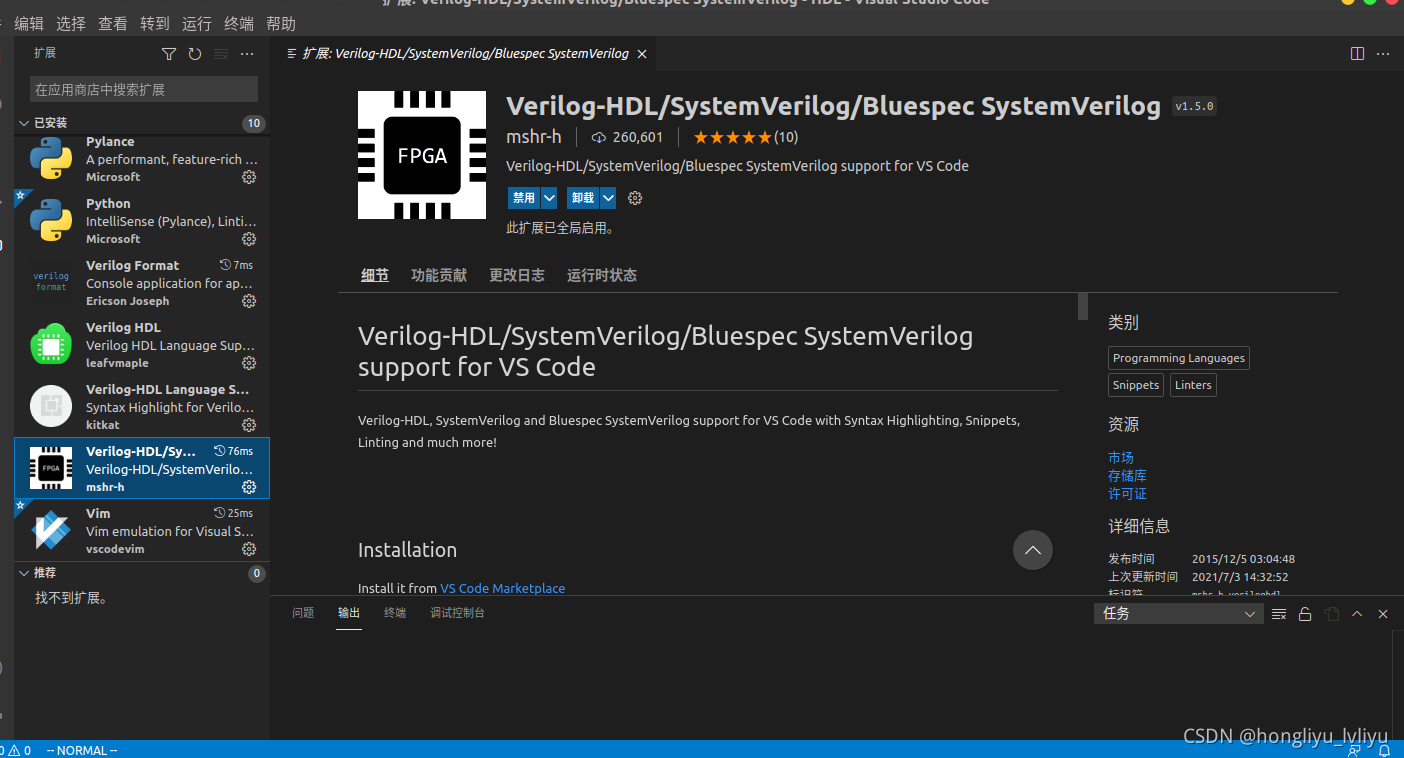

配置 VScode

首先在VScode的应用商店里头,配置verilog的插件:

这个插件的功能是

- 高亮代码

- 自动补全

- 自动纠错

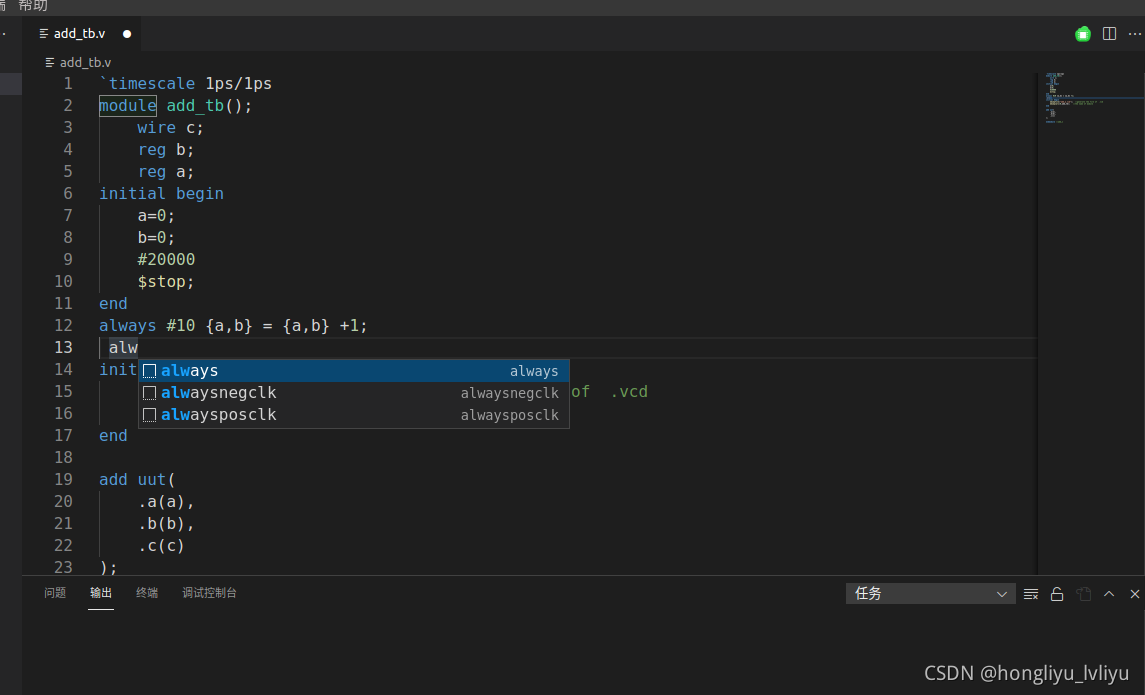

可以看到代码已经被高亮了,当输入always的时候,代码会自动补全

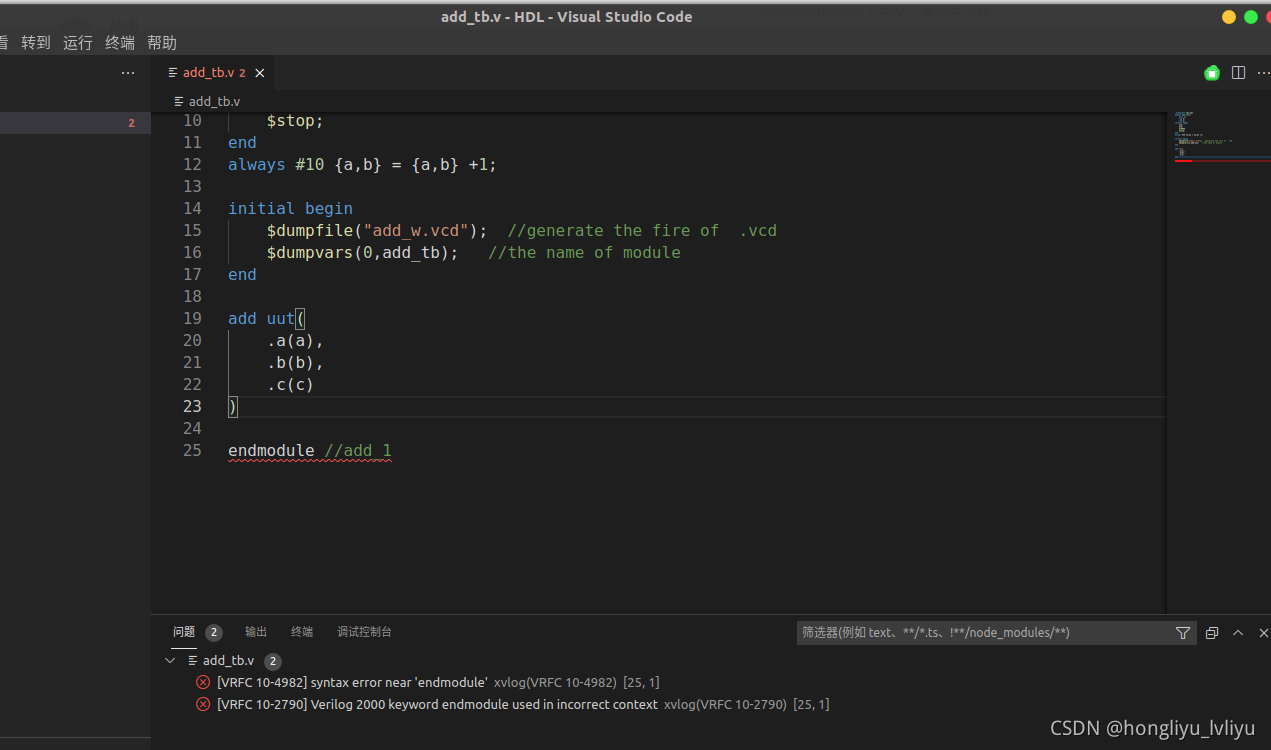

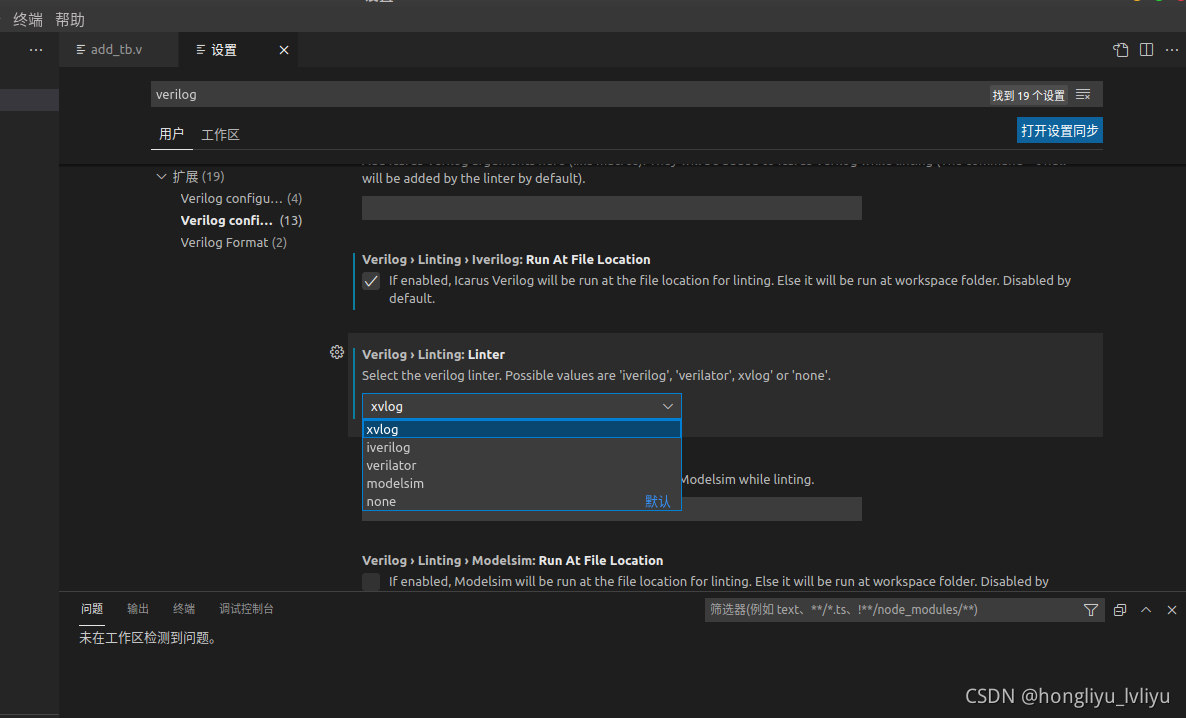

按下ctrl+s保存的时候,就会自动纠错,我这边使用的是xvlog 来纠错,因为安装了vivado,于是将xvlog 添加到环境变量中,然后在vscode的设置里进行配备就ok了

也可以使用iverilog,以下是配置界面:

xvlog的环境变量添加方法,使用export语句,将路径添加到.bashrc文件中

当然也可以使用iverilog

使用如下代码安装

sudo apt-get install iverilog

安装GTwave

直接在终端输入

sudo apt-get install gtkwave

使用.sh 脚本语言进行连调,

下面给出一个小的4位加法器.v文件和testbench:

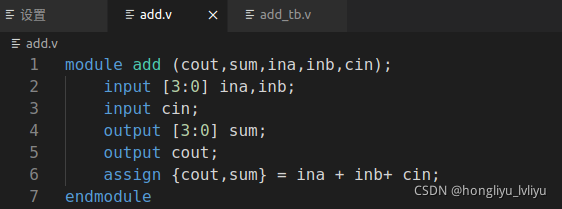

add.v

module add (cout,sum,ina,inb,cin);

input [3:0] ina,inb;

input cin;

output [3:0] sum;

output cout;

assign {cout,sum} = ina + inb+ cin;

endmodule

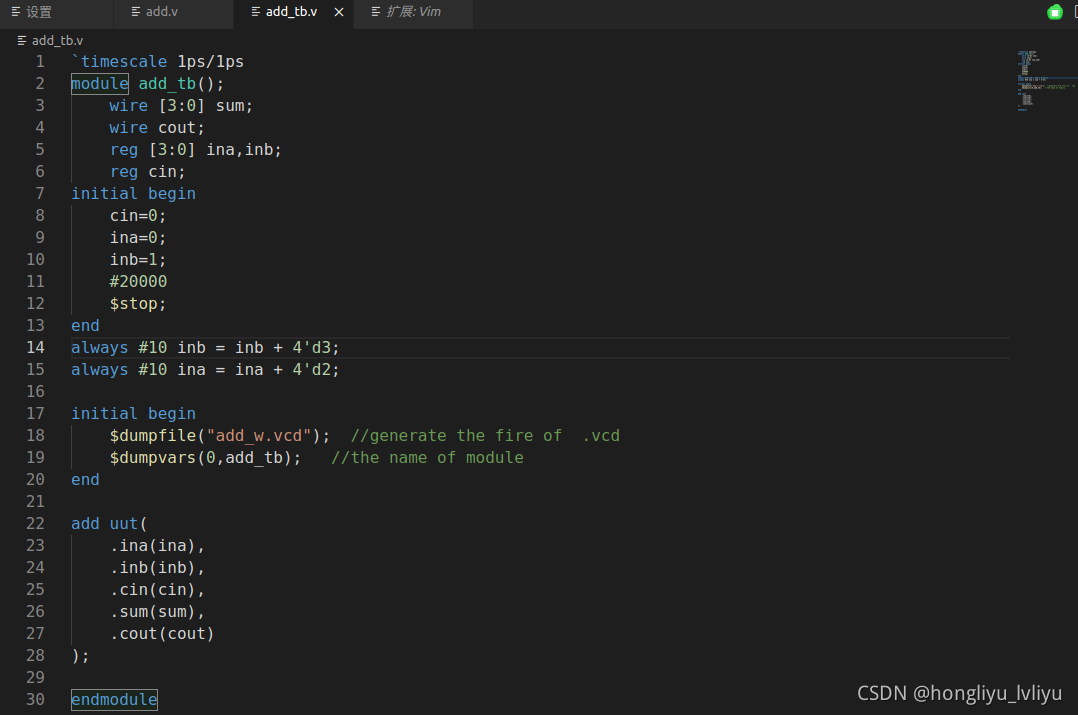

add_tb

`timescale 1ps/1ps

module add_tb();

wire [3:0] sum;

wire cout;

reg [3:0] ina,inb;

reg cin;

initial begin

cin=0;

ina=0;

inb=1;

#20000

$stop;

end

always #10 inb = inb + 4'd3;

always #10 ina = ina + 4'd2;

initial begin

$dumpfile("add_w.vcd"); //generate the fire of .vcd

$dumpvars(0,add_tb); //the name of module

end

add uut(

.ina(ina),

.inb(inb),

.cin(cin),

.sum(sum),

.cout(cout)

);

endmodule

以及.sh 文件

source_module="add"

testbentch_module="add_tb"

vcd_module="add_w"

echo $source_module

echo $testbentch_module

echo $vcd_module

iverilog -o $source_module".vvp" $source_module".v" $testbentch_module".v"

vvp -n $source_module".vvp" #simulation and generate wave

gtkwave $vcd_module".vcd" # view the wave by gtkwave

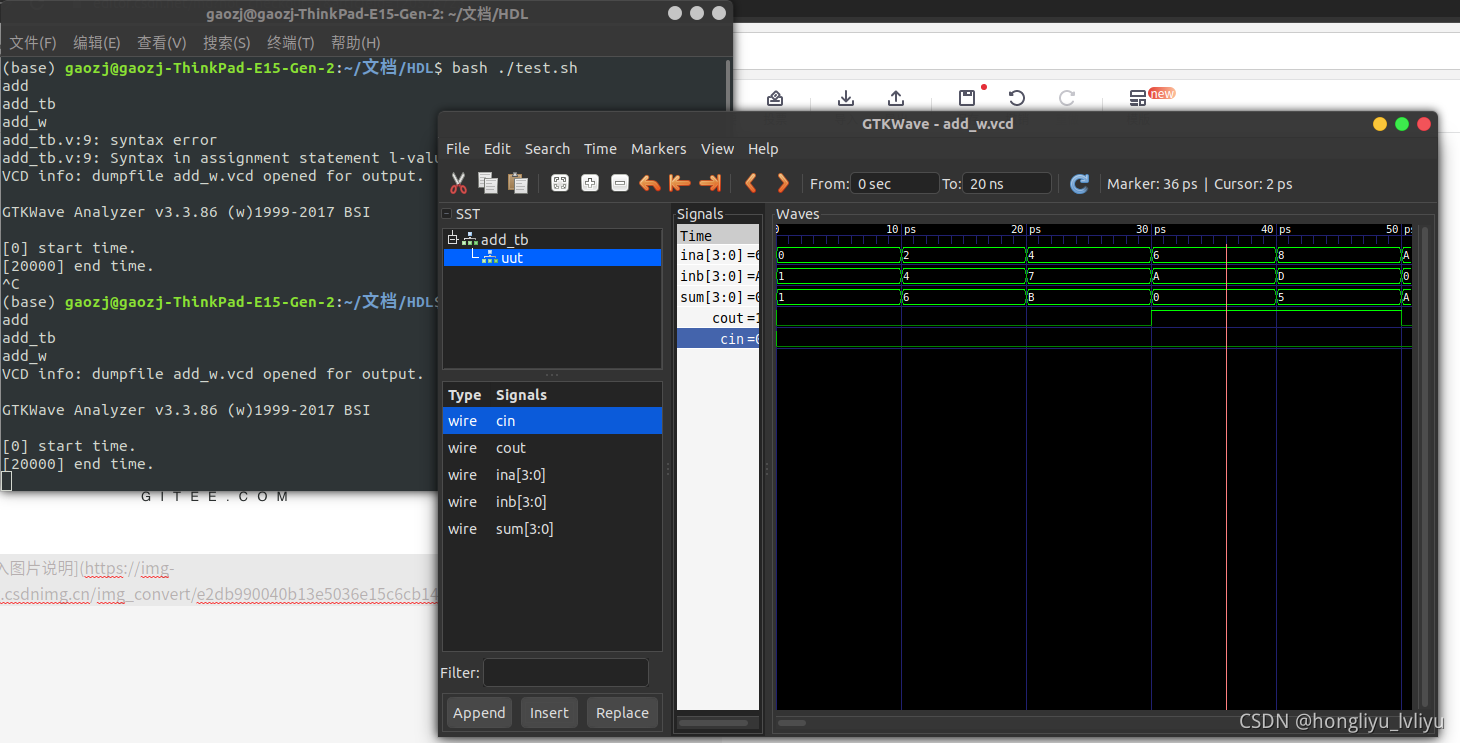

接下来在终端中运行.sh 文件即可看到仿真的波型

bash ./xxx.sh