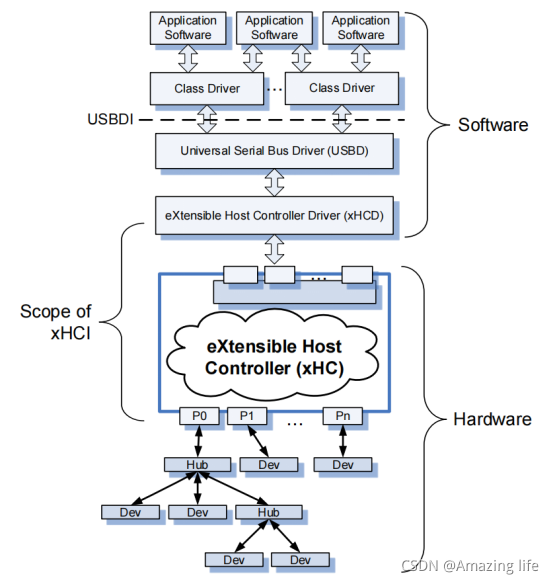

xhci规范中整体软件模型如下图所示:

这里描述的主要是上图中xhci部分,包括软件和硬件。

1. 接口架构

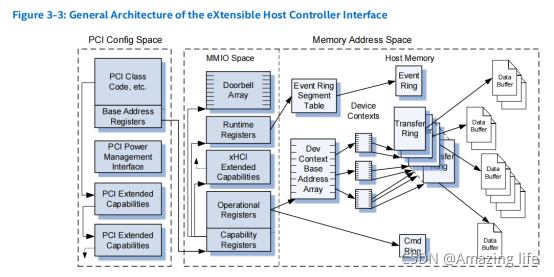

这里主要分为三部分:

1)Host Configuration Space.

每个xHC实现都应包括一种通过系统软件识别和枚举主机控制器的方法。本规范提供了一个主机配置空间的PCI示例,它被称为PCI配置空间。PCI配置空间定义提供了一个关于系统xHC枚举和资源(中断、电源、虚拟化等)的配置空间使用的工作示例。

2)MMIO Space.

寄存器空间表示xHC向驻留在内存地址空间中的系统软件提供的硬件寄存器。寄存器空间提供了在xHCI正常和扩展功能寄存器中定义的实现特定参数、操作和运行时控制和状态寄存器,以及用于标记对单个USB设备的访问的门钟阵列。该空间,通常被称为I/O空间,被实现为内存映射的I/O(MMIO)空间。

3)Host Memory

此空间由控制数据结构(设备上下文基地址阵列、设备上下文、传输环等)定义。以及由xHC驱动程序分配和管理的数据缓冲区,以启用单个设备的端点流量。此空间将在内存地址空间的内核和用户区域中分配。

xHCI支持两种USB传输类型:异步传输和周期性传输。同步传输和中断传输是定期传输类型。异步传输类型包括控制传输和批量传输。

“PCI配置空间”中的USB基本地址寄存器(BAR)指向xHC寄存器接口的基本地址。xHC寄存器接口包括4个主要组件: Capability Registers, Operational Registers, Runtime Registers, and the Doorbell Array。操作和能力注册器连接在MMIO空间中。运行时注册器实际上只是操作注册器的一个扩展。它们的分区允许xHC留在单独的页面边界上,允许运行时注册器更好地支持虚拟化。功能注册器中显示了xHCI功能指针机制(类似于PCI定义),以指向xHC实现的新功能或可选功能。

1)Capability register指定只读限制、限制和主机控制器实现的能力。这些值用作主机控制器驱动程序的参数

2)The Runtime and Operational Registers指定主机控制器配置和运行时可修改状态,并被系统软件用于控制和监视主机控制器的运行状态。这些寄存器被划分为在运行时大量访问的寄存器和仅在初始化时或在运行时少量访问的函数,以更好地支持xHCI的虚拟化。

3)xHCI扩展功能指定了xHC实现的可选特性,并提供了在本规范发布后向实现添加新功能的能力。

4)门铃阵列(Doorbell Array)是多达256个门钟寄存器,支持多达255个USB设备或集线器。每个门钟寄存器为系统软件提供一种机制,如果xHC有插槽或端点相关的工作,则通知xHC。门铃寄存器中的DB目标字段用一个值标识“响”门铃的原因。门铃寄存器0被分配给主机控制器,用于命令环管理。

- 注:这里所谓的插槽指的是device slot,以后会说到,可以理解为一个设备就是一个插槽。