站在了前人的肩膀上

参考教程:https://blog.csdn.net/qq_38791897/article/details/88806037

https://blog.csdn.net/qq_39498701/article/details/84668833

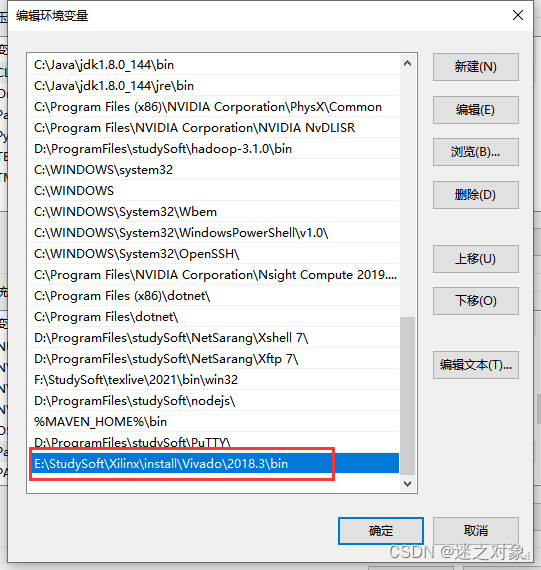

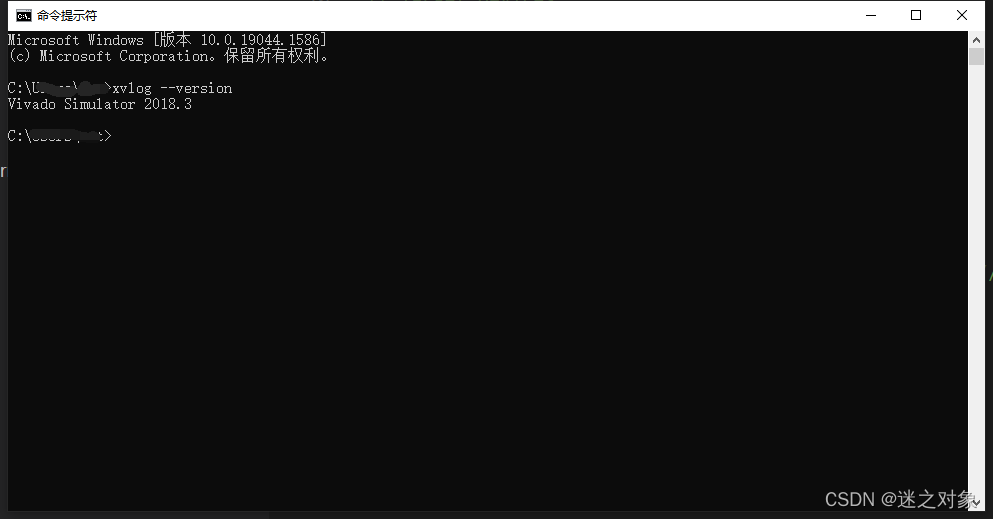

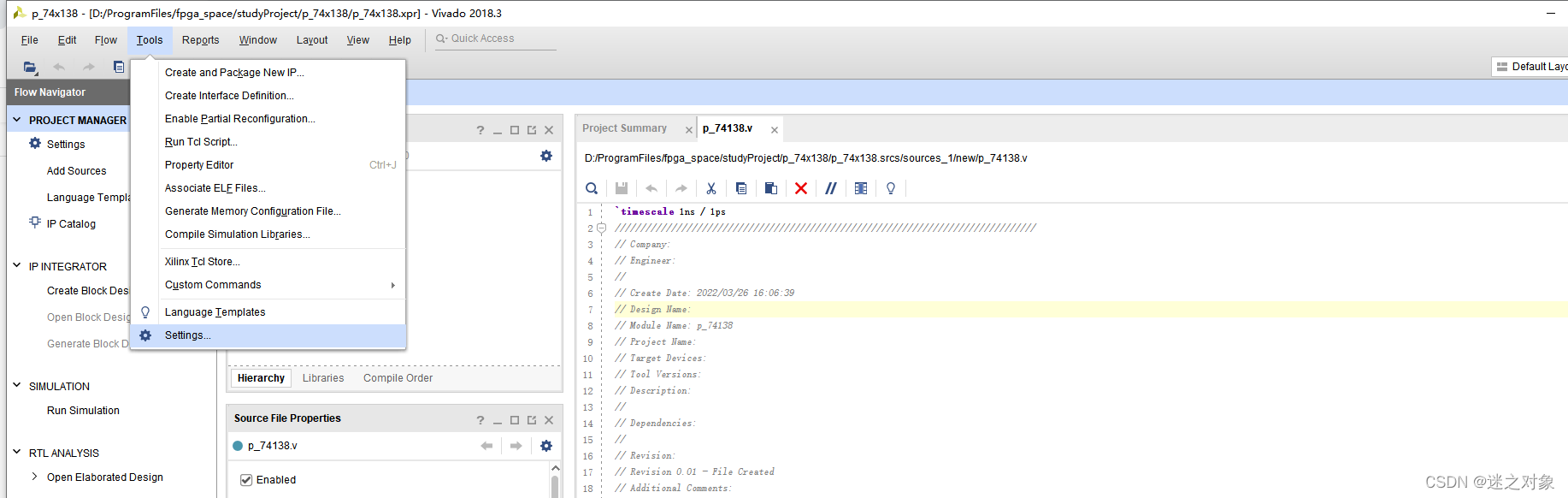

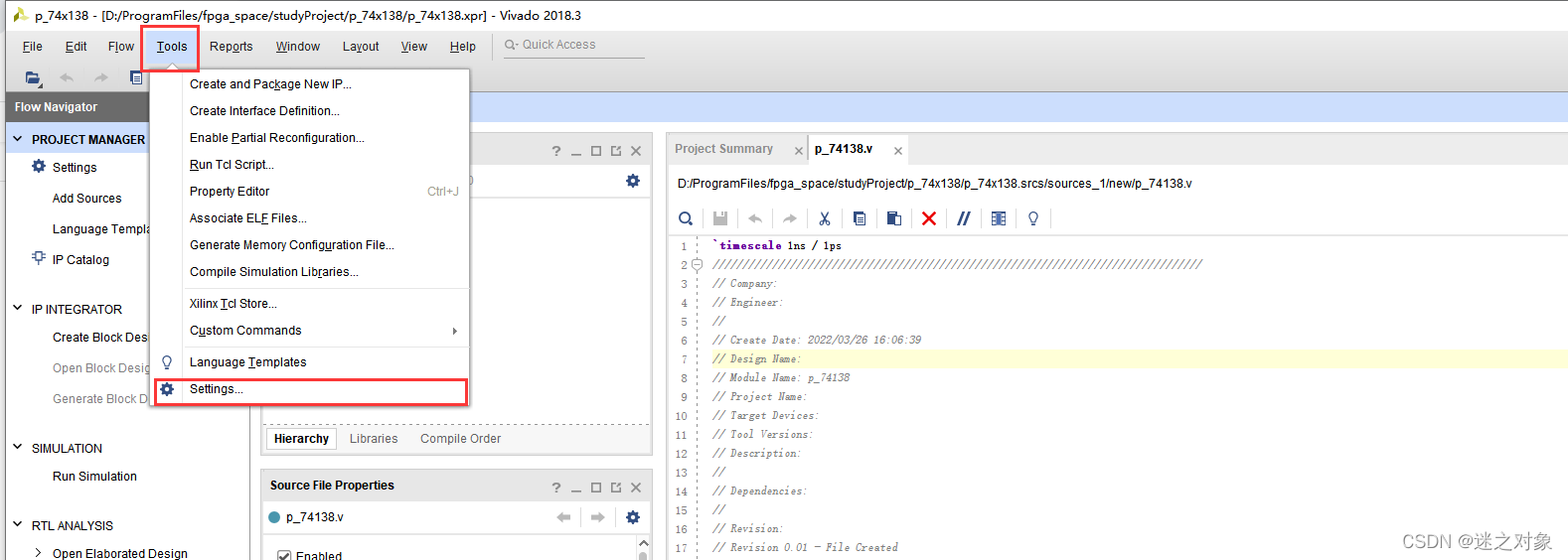

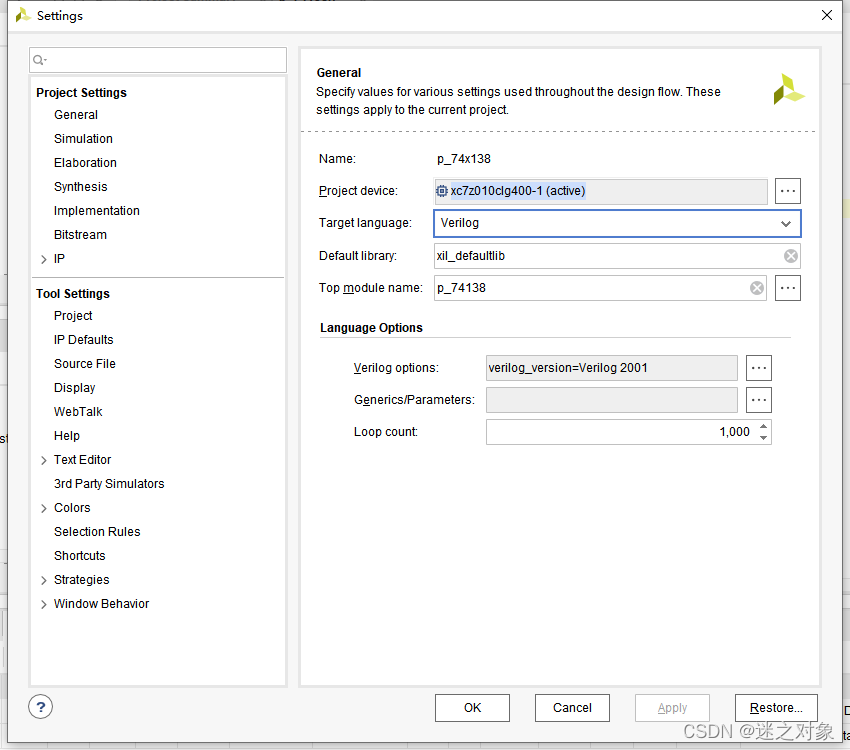

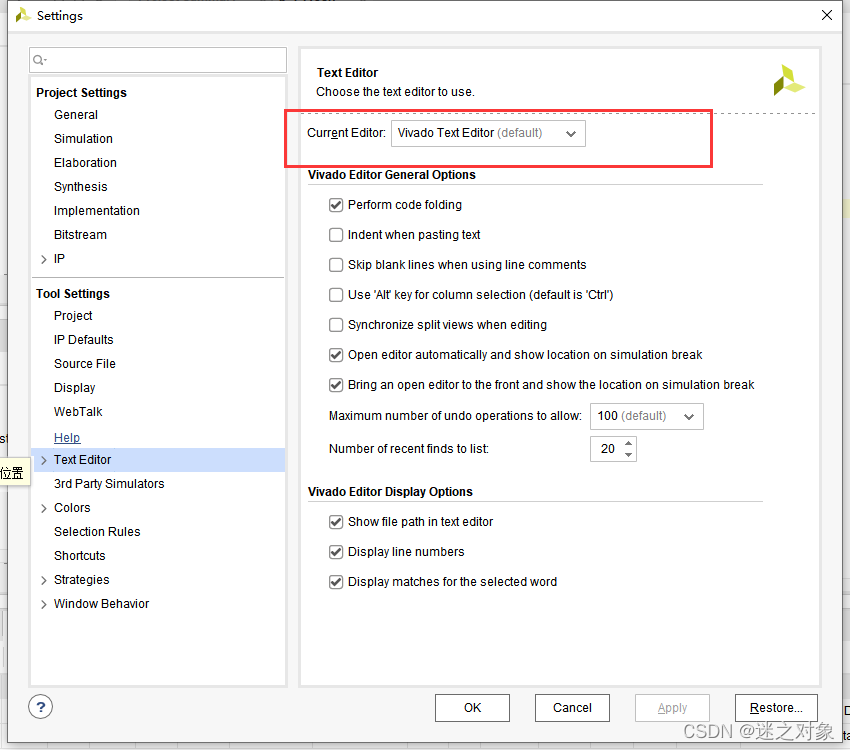

Vivado是Xilinx公司提供的逻辑开发平台(之一)。如果不喜欢Vivado自带的文本编辑器,可以选择第三方的文本编辑器,例如VSCode。在Vivado中指定VSCode作为文本编辑器的方法如下:

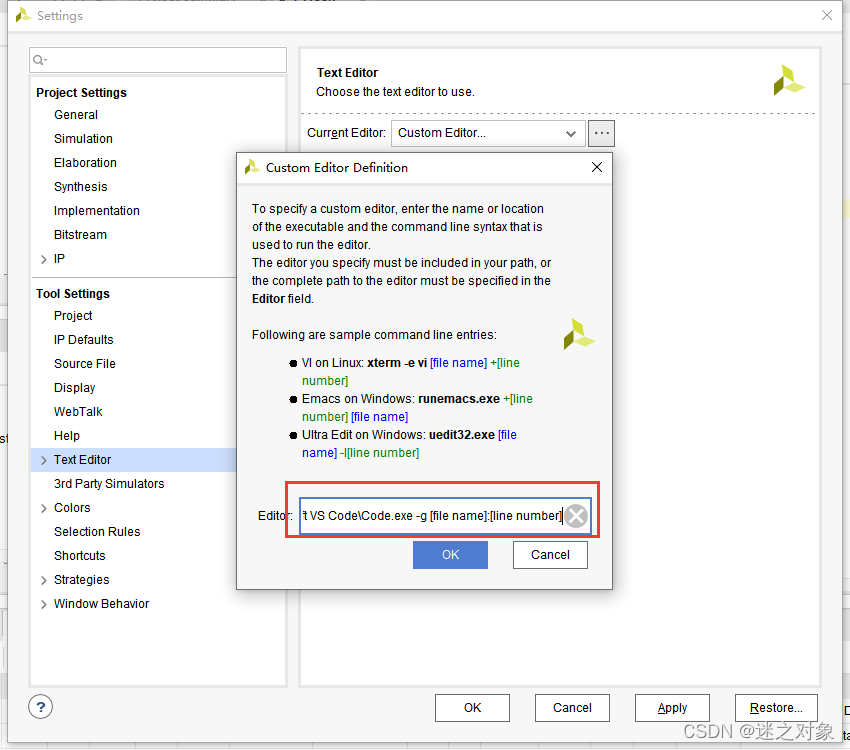

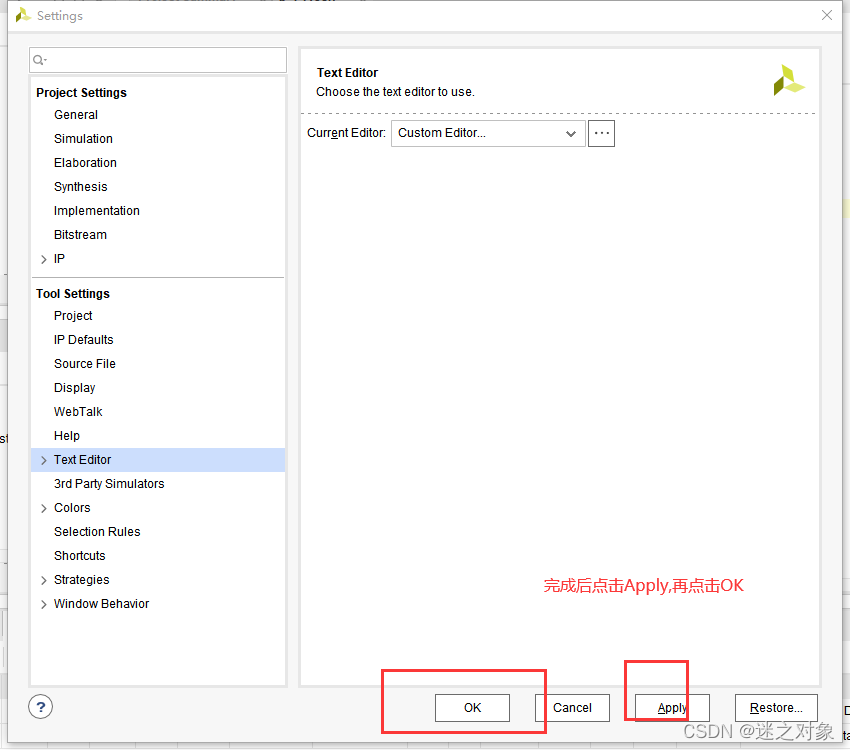

一 :Vivado指定Vscode作为编辑器

点击菜单栏上的Tools ,之后再点击Settings

E:\StudySoft\vsCode\Microsoft VS Code\Code.exe

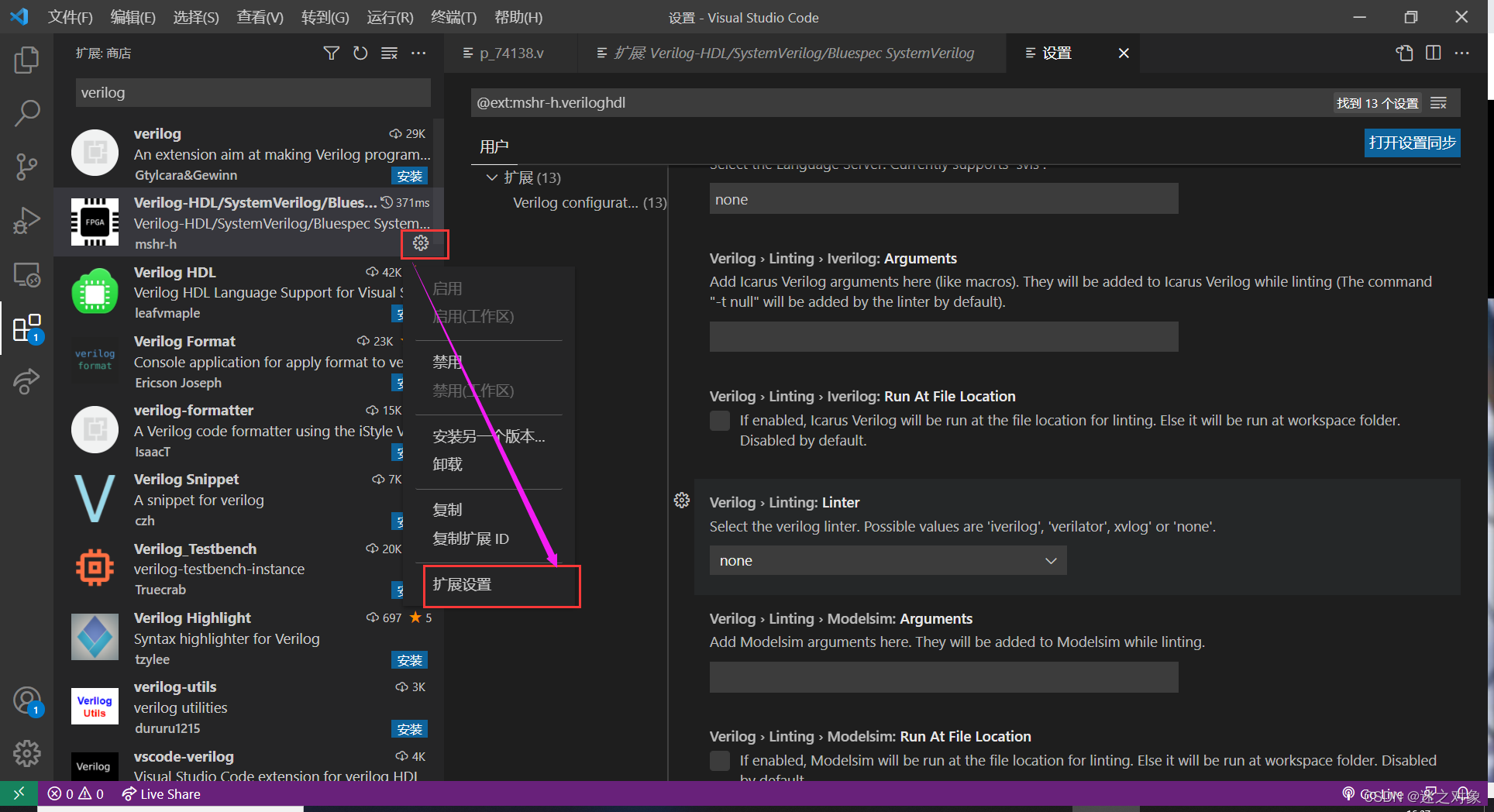

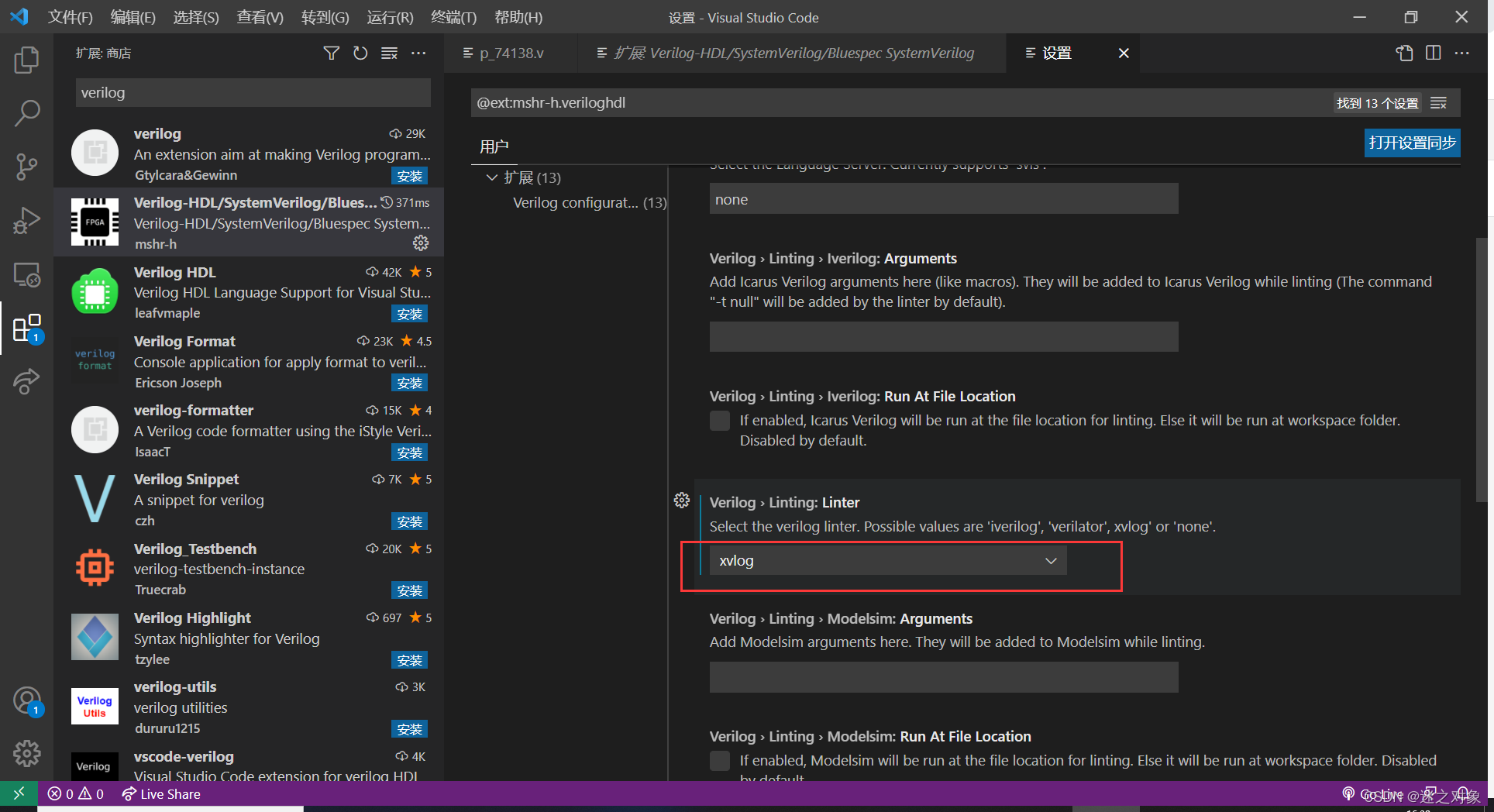

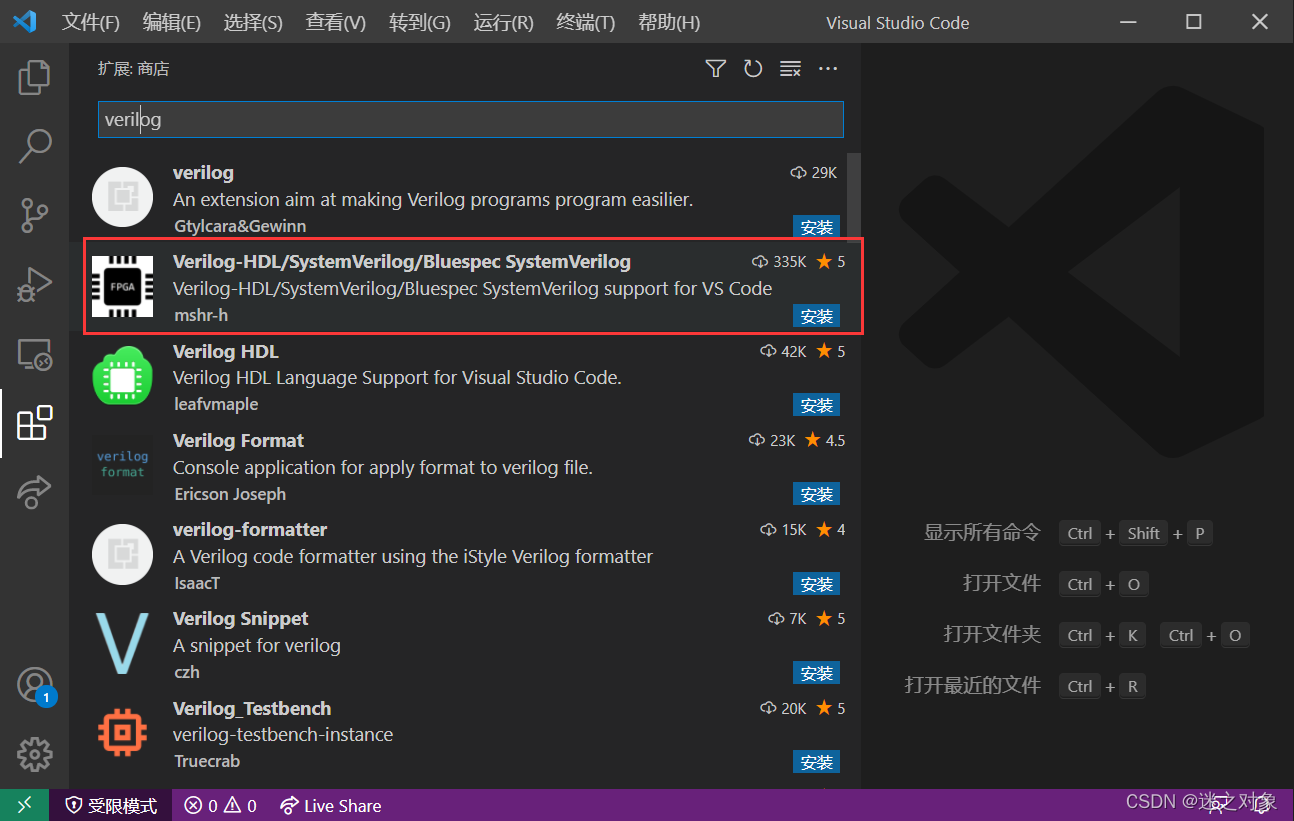

二:用VsCode舒适的编写Verilog

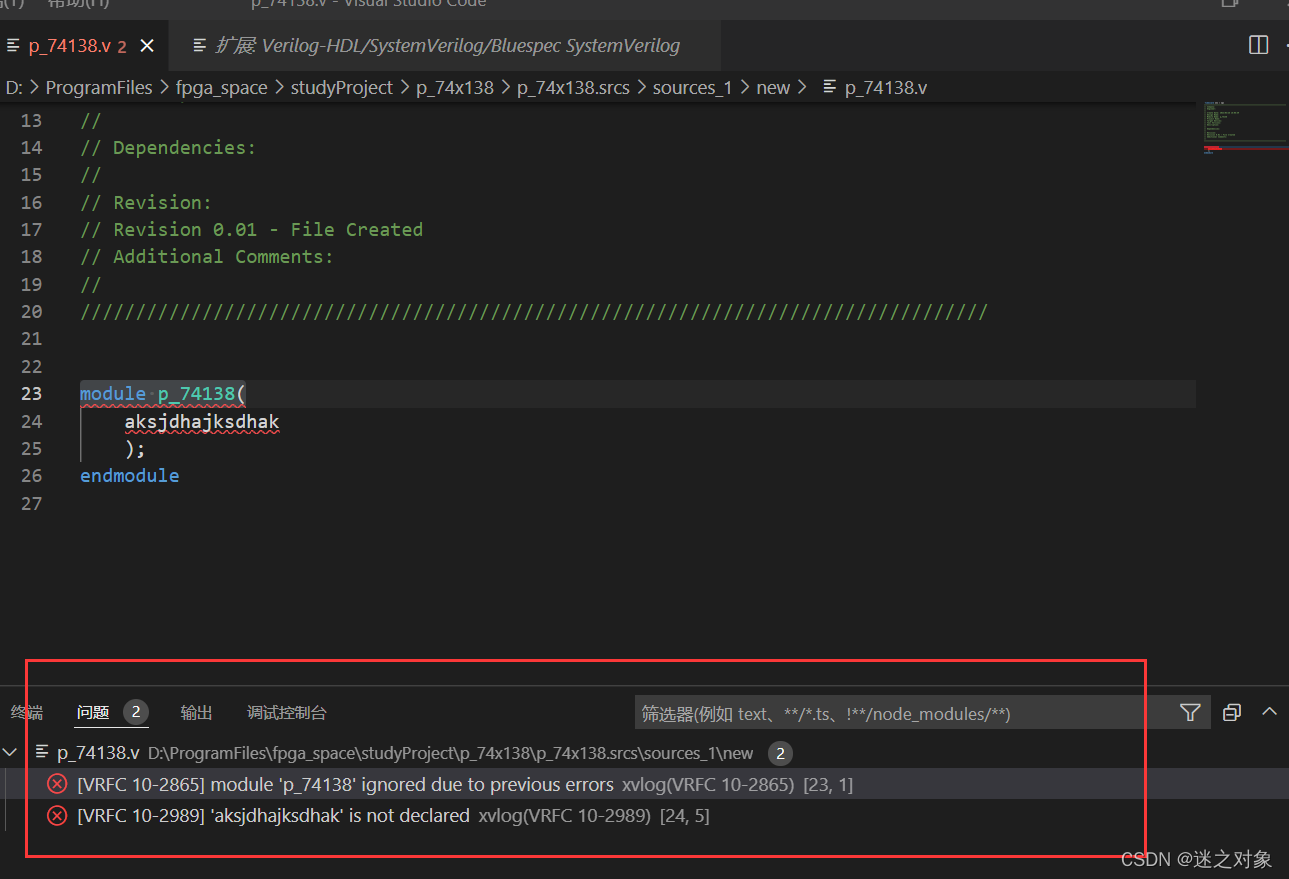

步骤一、实现自动纠错

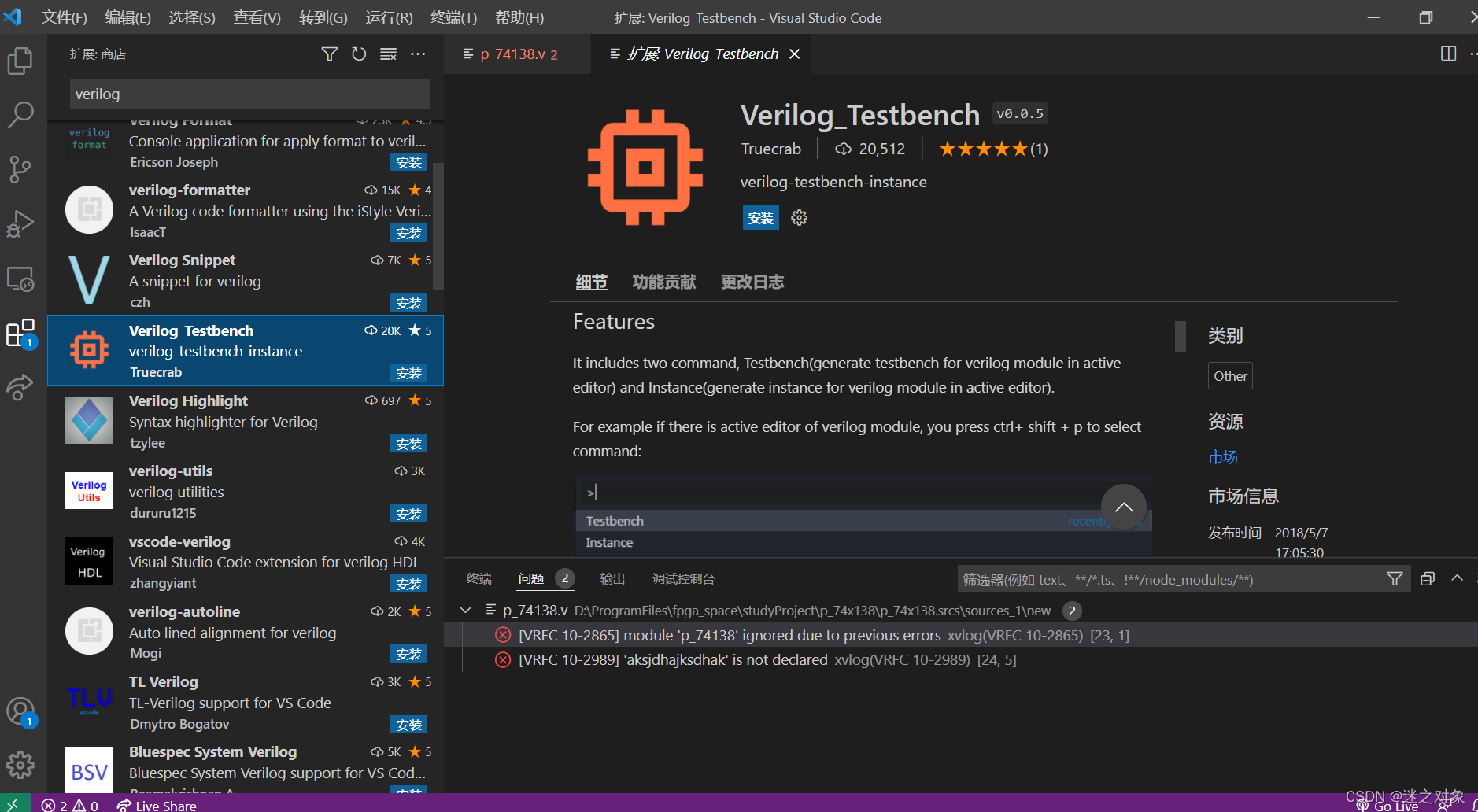

打开扩展,搜索verilog

https://blog.csdn.net/qq_39498701/article/details/84668833

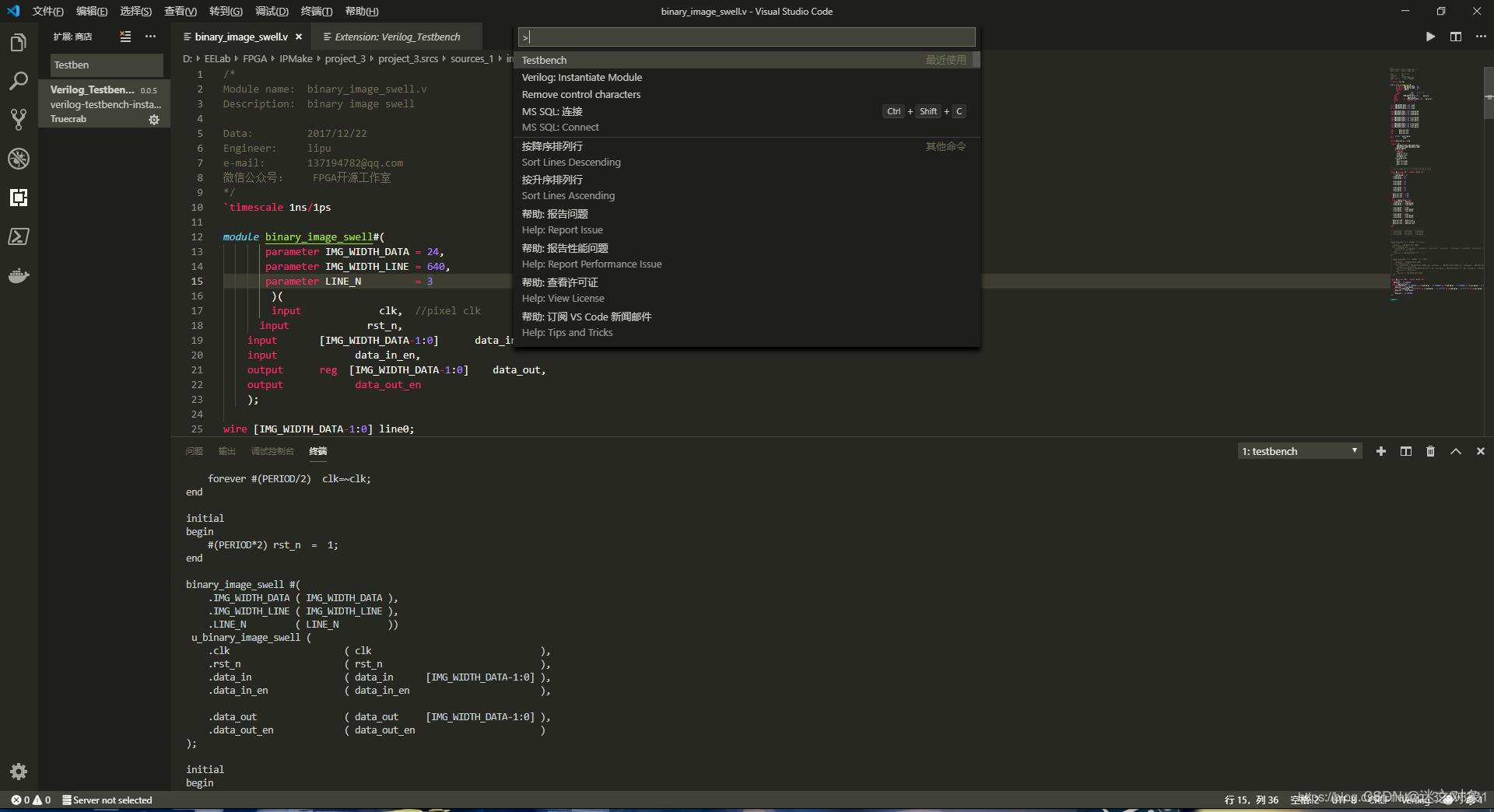

步骤二、自动生成Testbench

有时候在工程中要例化一个模块,这个模块有几十个输入几十个输出,如果没有一个好的脚本帮助你,不仅人为出错的可能比较大,例化的过程想必也是痛苦的。

还好有人已经在VsCode编写过自动生成Testbench的脚本了,感谢

扩展商店搜索Verilog_TestBench,安装过后,任意编写一段verilog程序。按下ctrl+shift+p,选择testbench即可生成testbench对应的tb文本。

效果如上图所示。执行脚本之后,其出结果导向powershell的输出结果之中。帮我们自动生成了了时钟信号,复位信号,以及进行了模块的例化。如果你只需要例化模块,复制这一部分进你的代码中就可以了。到这里,VsCode已经能够给你的工程带来及其舒适的体验了。

步骤三、进一步优化

这个功能我还没有用到,具体参考文章:https://blog.csdn.net/qq_39498701/article/details/84668833