示例代码包下载

vscode配置verilog开发环境示例代码包,可编译运行,观察波形-嵌入式文档类资源-CSDN下载

?具体操作按图索骥~~~~~

1. 安装iverilog编译器

官网链接 Icarus Verilog for Windows

?

?

选择下载带了Icarus和wtkwave的版本,这样既可以查看波形。

可以在命令行查看,配置路径

iverilog -v

Icarus Verilog version 12.0 (devel) (s20150603-1110-g18392a46)

Copyright (c) 2000-2021 Stephen Williams (steve@icarus.com)

This program is free software; you can redistribute it and/or modify

it under the terms of the GNU General Public License as published by

the Free Software Foundation; either version 2 of the License, or

(at your option) any later version.

This program is distributed in the hope that it will be useful,

but WITHOUT ANY WARRANTY; without even the implied warranty of

MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

GNU General Public License for more details.

You should have received a copy of the GNU General Public License along

with this program; if not, write to the Free Software Foundation, Inc.,

51 Franklin Street, Fifth Floor, Boston, MA 02110-1301, USA.

iverilog: no source files.

Usage: iverilog [-EiSuvV] [-B base] [-c cmdfile|-f cmdfile]

[-g1995|-g2001|-g2005|-g2005-sv|-g2009|-g2012] [-g<feature>]

[-D macro[=defn]] [-I includedir] [-L moduledir]

[-M [mode=]depfile] [-m module]

[-N file] [-o filename] [-p flag=value]

[-s topmodule] [-t target] [-T min|typ|max]

[-W class] [-y dir] [-Y suf] [-l file] source_file(s)

See the man page for details.gtkwave -v

GTKWave Analyzer v3.3.108 (w)1999-2020 BSIvvp -h

Usage: vvp [options] input-file [+plusargs...]

Options:

-h Print this help message.

-i Interactive mode (unbuffered stdio).

-l file Logfile, '-' for <stderr>

-M path VPI module directory

-M - Clear VPI module path

-m module Load vpi module.

-n Non-interactive ($stop = $finish).

-N Same as -n, but exit code is 1 instead of 0

-s $stop right away.

-v Verbose progress messages.

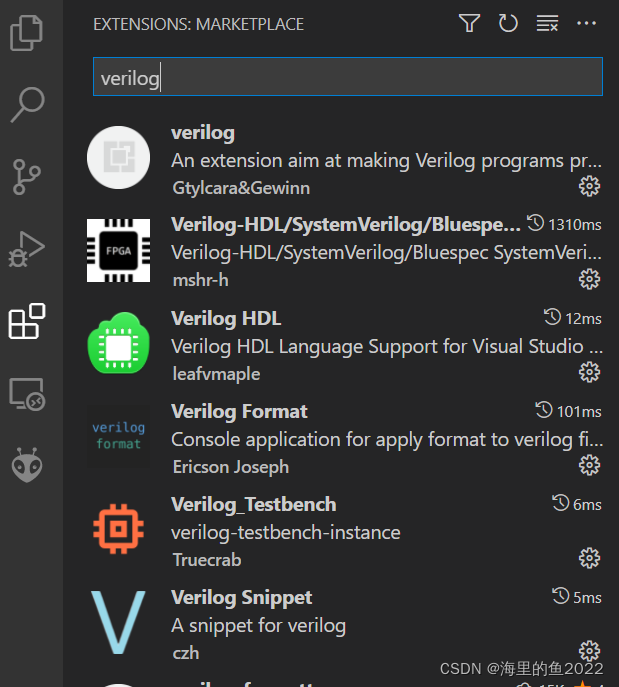

-V Print the version information.2 Vscode安装插件

这些就够用了,包括了编译运行和testbench自动实例化

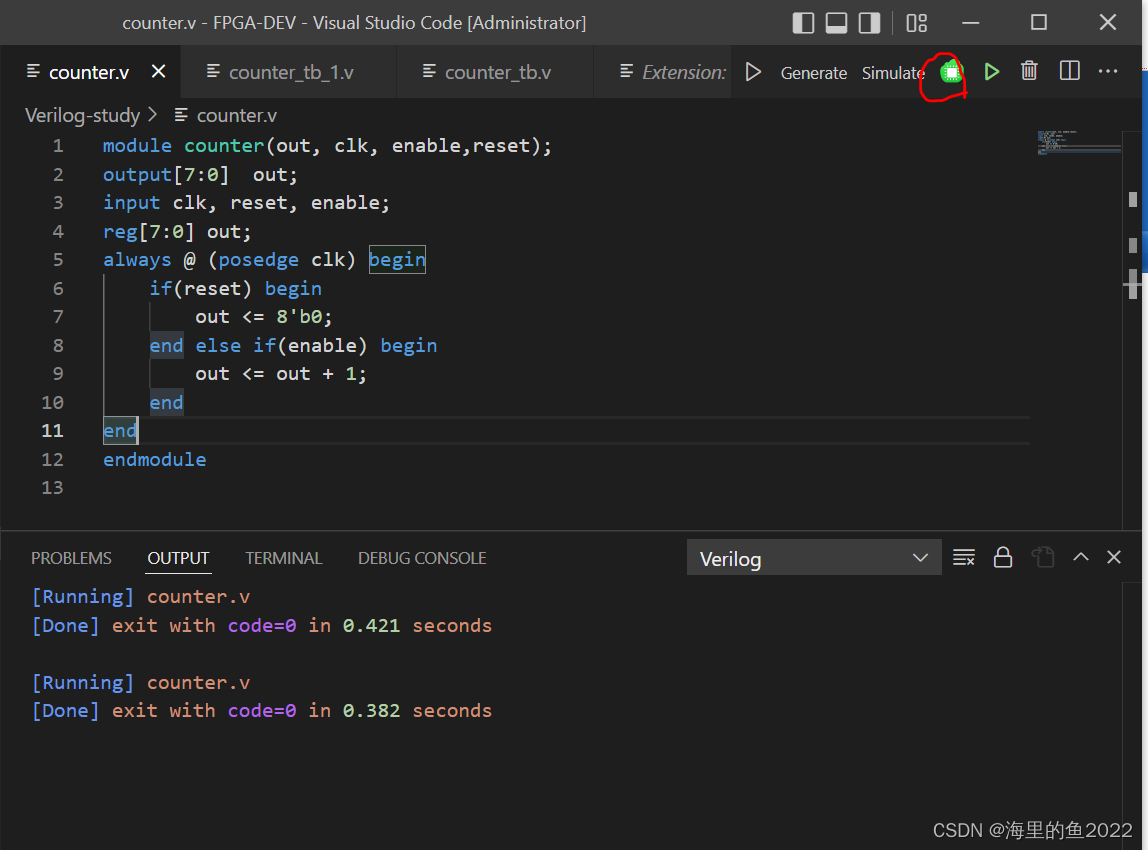

?3. 示例验证

?编辑一个8位时钟脉冲计数器

module counter(out, clk, enable,reset);

output[7:0] out;

input clk, reset, enable;

reg[7:0] out;

always @ (posedge clk) begin

if(reset) begin

out <= 8'b0;

end else if(enable) begin

out <= out + 1;

end

end

endmodule

运行检查错误

?4. 自动生成testbench实例化框架,注意,只是框架,具体测试信号激励还是要自己填写。

CTRL+SHIFT+P选择testbench,运行结果

python c:\Users\haiyang.pan\.vscode\extensions\truecrab.verilog-testbench-instance-0.0.5\out\vTbgenerator.py d:\FPGA-DEV\Verilog-study\counter.v

//~ `New testbench

`timescale 1ns / 1ps

module tb_counter;

// counter Parameters

parameter PERIOD = 10;

// counter Inputs

reg clk = 0 ;

reg reset = 0 ;

reg enable = 0 ;

// counter Outputs

wire [7:0] out ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

initial

begin

#(PERIOD*2) rst_n = 1;

end

counter u_counter (

.clk ( clk ),

.reset ( reset ),

.enable ( enable ),

.out ( out [7:0] )

);

initial

begin

$finish;

end

endmodulecopy到testbench的设计文件里,并添加激励信号定义

//~ `New testbench

`timescale 1ns / 1ps

module tb_counter;

// counter Parameters

parameter PERIOD = 10;

// counter Inputs

reg clk = 0 ;

reg reset = 0 ;

reg enable = 0 ;

// counter Outputs

wire [7:0] out ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

//initial

//begin

// #(PERIOD*2) rst_n = 1;

//end

counter u_counter (

.clk ( clk ),

.reset ( reset ),

.enable ( enable ),

.out ( out [7:0] )

);

initial

begin

clk = 0;

forever #10 clk = ~clk;

$finish;

end

initial begin

reset = 1;

#15 reset = 0;

#1000 $finish;

end

initial

begin

$dumpfile("counter_tb.vcd"); //生成的vcd文件名称

$dumpvars(0, tb_counter); //tb模块名称

end

initial begin

enable = 1;

end

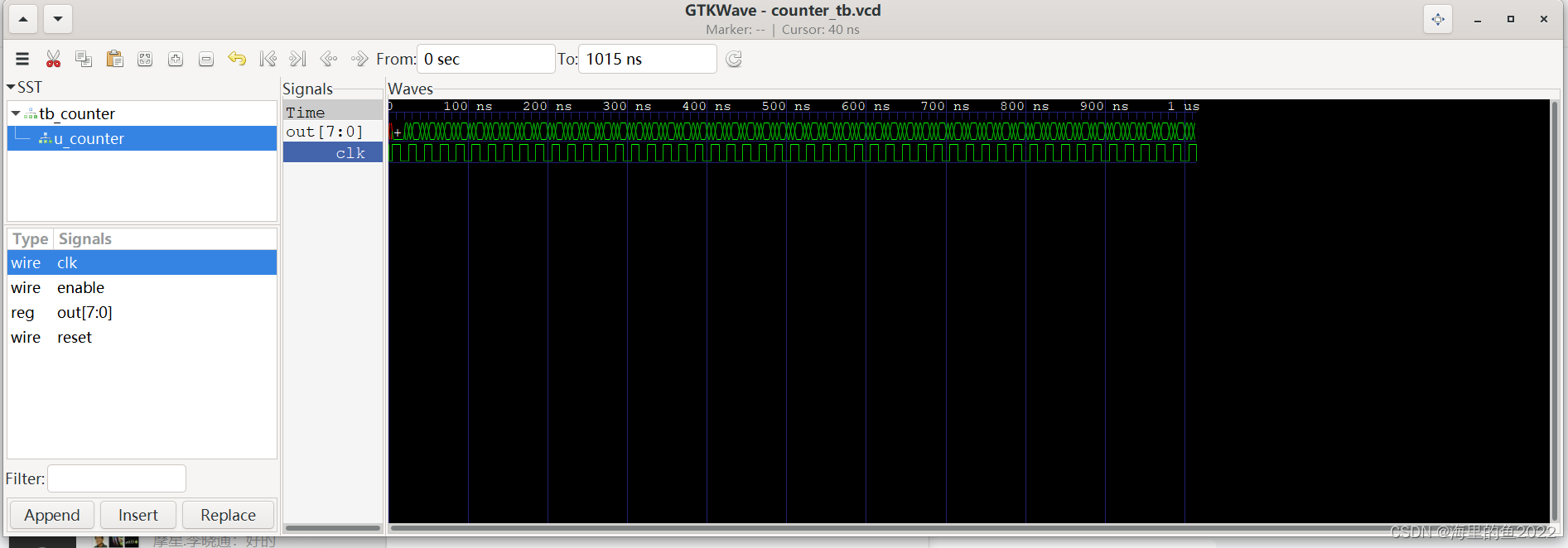

endmodule?运行编译仿真

命令行运行

iverilog -o counter.vvp counter.v counter_tb_1.v ?VVP生成波形

vvp counter.vvp

VCD info: dumpfile counter_tb.vcd opened for output.

counter_tb_1.v:46: $finish called at 1015000 (1ps)?gtkwave观察波形

gtkwave counter_tb.vcd

?