textbook:Computer Organization and Architecture 10th - William Stallings

useful tool:

ʮ����ת������ת����:

https://www.99cankao.com/numbers/twos-complement.php

����ӷ�����:

https://www.easycalculation.com/2s-complement-addition.php

����תʮ����

https://www.exploringbinary.com/twos-complement-converter/

floating point:

������

boolean func����:

https://www.boolean-algebra.com/

https://www.emathhelp.net/zh-hans/calculators/discrete-mathematics/boolean-algebra-calculator/?f=x%28%7Ey%7Ez+%2B+yz%29

(�ڶ�������һ��)

��ֵ��תfunc:(��kmap)

http://tma.main.jp/logic/index_en.html

������ֵ����ͼ:logisim

syllabus

����:

Grades

Grade A (A+, A, A-), 15% - 20%

Grade A and Grade B (B+, B, 😎, ~ 60%

lab

���

�����

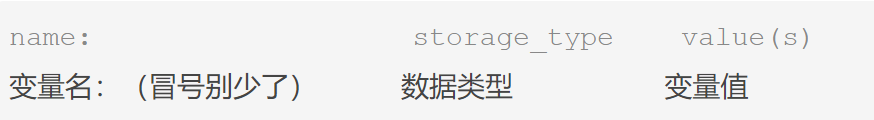

���ݱ�������:.data

���������:.text

����������ʽ:

��:var1: .word 3;

array1: .space 12(����һ�� 12�ֽ� ���ȵ����� array1, ���� 3������)

load/store ��ȡд��

w:word

b:byte

a:address

��ȡload:

lw register_destination, RAM_source

���ڴ��� ���� RAM_source �����ݵ� ��Ӧ�ļĴ�����

lwָloadword,ͬ�����Ի���lb(load byte)

�store:

sw register_source, RAM_destination

��ָ���Ĵ����е����� д�� ��ָ�����ڴ���

sw��store word

Indirect and Based Addressing��������Ѱַ

ֱ��Ѱַ

la $t0, var1

��var1�ĵ�ַ�����Ĵ���t0

���Ѱַ

lw $t2, ($t0)

����ַΪ�Ĵ���t0�е����ݵ����ݸ����Ĵ���t2

sw $t2, ($t0)

���Ĵ���t2�����ݸ�����ַΪt0���ݵ��ڴ�

ƫ����:

sw $t2, -4($t0)��������

���Ĵ���t2�����ݸ�����ַΪ(t0����-4)���ڴ�

����ָ��

������

branch��֧ifelse

��ת(while,for,goto)

�ӳ������

system call/IO

lab1

lec

lec1

computer=

os+CPU+RAM+**Graphics+Storage+Printers

cpu :

cpu-control unit:

cpu instruction cycle:fetch and execution

important registers

Program Counter (PC): stores the memory address of the next instruction (will increment after fetching an instruction)

Instruction Register (IR): stores the instruction currently being executed

Memory Address Register (MAR): stores the memory address from which data (also instructions) will be fetched to CPU

Memory Buffer Register (MBR): stores the data being transferred to and from the immediate access storage (like a buffer to store data temporarily)

CPU action in fetch:

know the instruction��s memory address (pc)

->instruction put in MAR, cpu fetch

->instruction put in MBR, loaded into IR

fetch ���,pc����һ��

lec2 numberSystem & computer Arithmetic

10����������ת2����:

10����С��ת2����:(��ʱ��ﵽ����ȷ��ֵ)

��ʾ��Χ:

Arithmetic & Logic Unit (ALU)

����:

10���Ƹ�����:����10����������ʾ,Ȼ��ȡ�䲹��(1��0,0��1Ȼ��+1)

10���Ƹ�С��:floating point representation

bias=E+127

�Ӽ���

�ӷ����overflow:

- ���Ų�ͬ,�������;

- ������ͬ,��������ķ���λ�ͱ��������λ�Ƿ���ͬ,�����ͬ���ж�overflow

- ����6λ101101(-19)�Ӳ���6λ111001(-7)�ó���7λ,ȥ��1 100110(-26)δ���

- 10011 + 10111

- ���� 101101 (-19) + 101001(-23)��ӽ�� 1 010110 ȥ����7λ,010110,���Ÿı�,�����(��λ�����ʾ��Χ-32,31)

- ������ӷ���������һ����ʱ,����0(1011+11=1011+1111)

����:����ӷ�

�˷�:

Use two operations ��add�� and ��shift�� to implement the addition

if bit in the multiplier is 0: just shift

if bit in the multiplier is 1: add and shift

ע:��ΪQÿִ��һ�ζ�Ҫ����,�ճ��Ŀռ������������productA,���Դ���ռ��2n����n

ʮ����ת2����

����:

������:

��������ʾ��

lec3 assembly language

MIPS

Register-based architecture:

cpu��register�Ͻ��в���:

operations can be divided into two categories:

(1) memory access (load and store data between memory and registers)

(2) ALU operations (operations between registers)

MIPS registers:

MIPS memory:

0xFFFFFF��0x800000��ROM��OS�õ�,;user program���õĵط��·ֳ�������:

text,data,stack��

R-type instructions:

I-type instructions

J type instruction:

jump:

�����instruction���26bit��ʾ32bit�ĵ�ַ?

1, һ��instruction��4byte,���ÿ��instruction�ĵ�һ��byte��4�ı���,�����������bitһ����00

2,��ת��ַ��ǰ��λ���ͱ���ַ(pc)��ǰ��λ��һ��,���Dz�����̫Զ

meaning of u

addu: overflow is ignored does not mean unsigned

add : overflow cause interrupt

һ����addu

multiple/division:

using lo and hi

lec4 MIPS Assembly Language

0/sign extend

ADDI, ADDIU are both use signed-extend.

ANDI, ORI, XORI both use zero-extend.

zero: constant must �Ǹ���

operands

- shiftleft: unsigned and ������������

-

- shiftright: �����ʾ

- logical: ��0

- arithmetic:��1

- noop: sll $0,$0, 0

- lx d, offset(b)

lec5 MIPS Assembly Language

jump

instruction cycle:

�����ǵ���j��һ���ֱ����ת��,Ҫ����һ�����,���仰˵jump�����һ��ָ��һ���ᱻִ��(�������ó�noop)

��,ѭ�����,addiu��ִ��5�Ρ�

(branch����ת��ַͬ��)

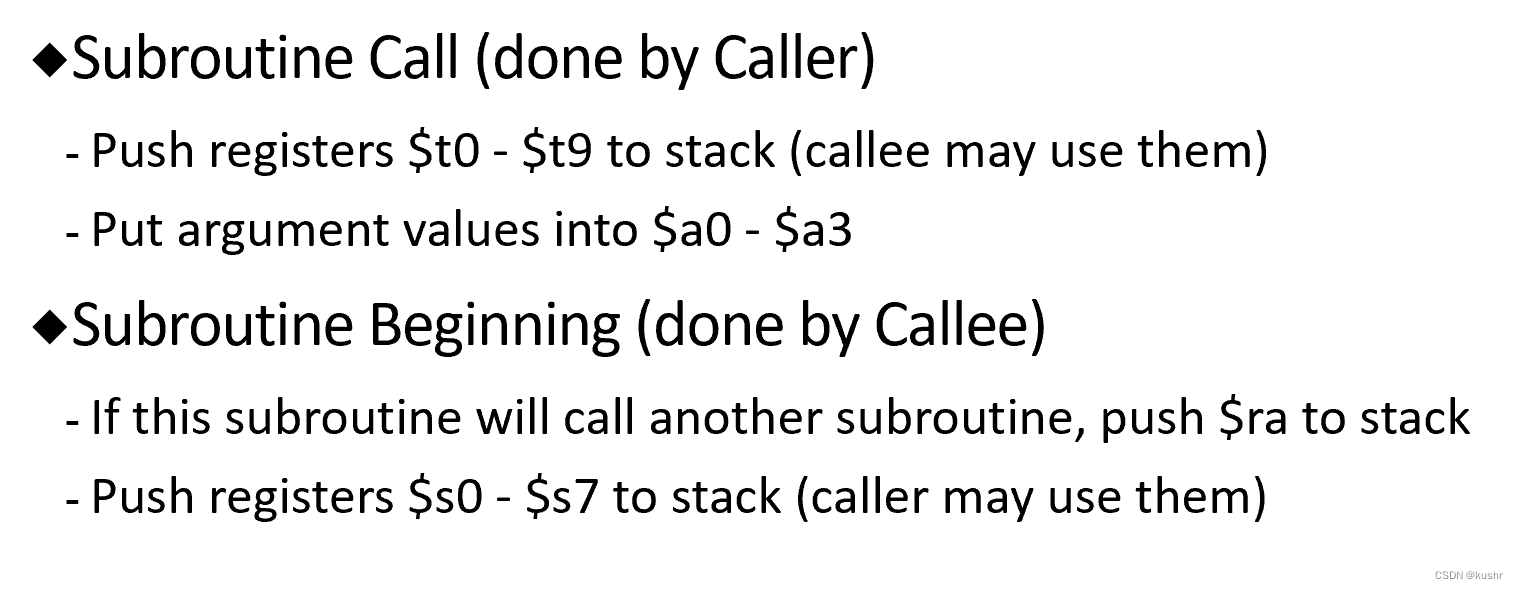

�Ĵ���ʹ�ù淶

-

$t0 - t9: subroutines can use without caution

-

$s0 - $s7: saved registers; subroutines should not use (if need to use it, save the value first and restore the value after use)

-

$a0 - $a3: contain arguments for the subroutine

-

$v0 - $v1: contain values returned from the subroutine

-

Recall: Caller should use $s0 - $s7, Callee should use $t0 - $t9

-

�������callerҲ��callee,��s0��s7,��Ҫ��stack��

-

lec6 digital logic1

boolean������

����:

https://www.boolean-algebra.com/

��ֵ��תfunc:

http://tma.main.jp/logic/index_en.html

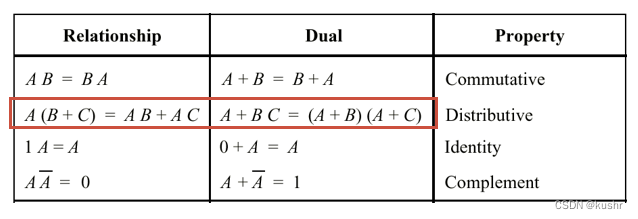

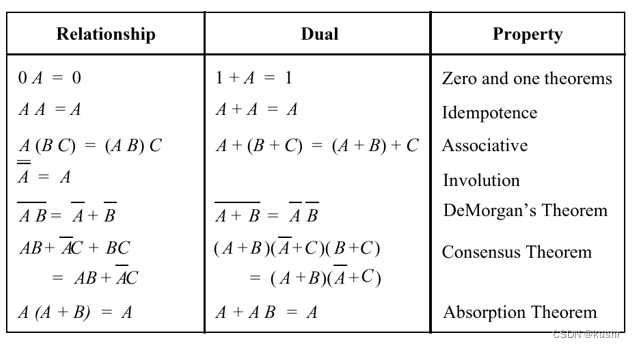

boolean Algebra

n���������switch function:22n

dual:

and��or,or��and,0,1����(��/�Dz�����!)

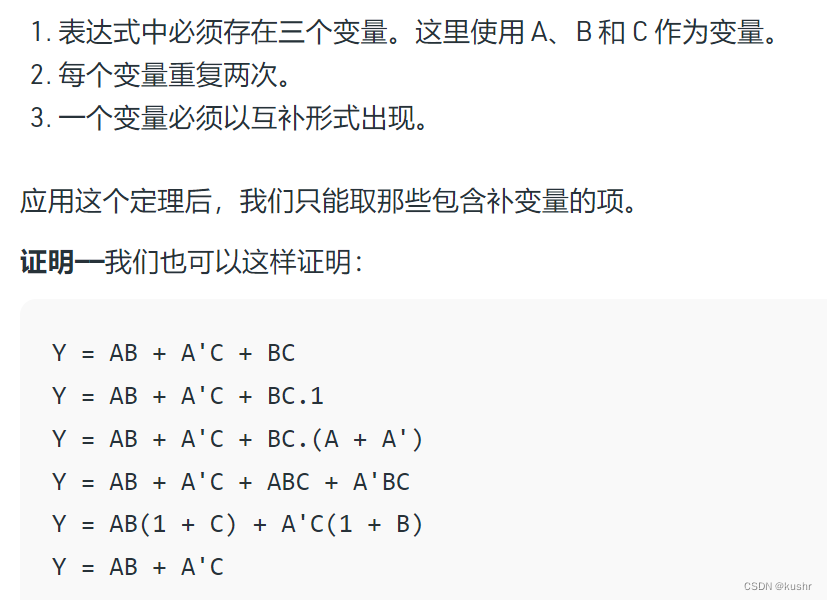

consensus Theorem:

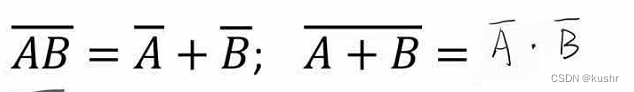

DeMoegan��s Theorem

��������and/or operation

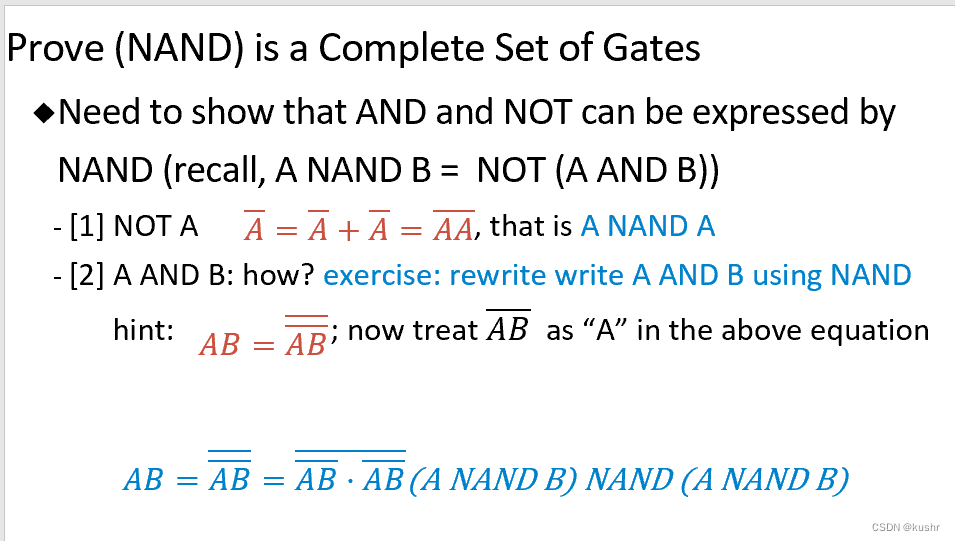

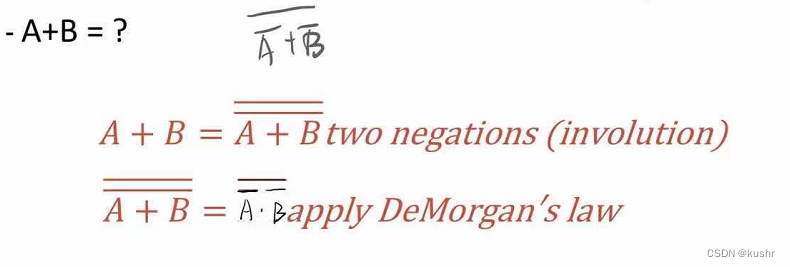

completeness of functionality

ʵ��and,or,��not

(NAND)

֤��:NAND

(NOR)

(OR,NOT)

(AND, NOT)

֤��:��and��not��ʾor

combinational logic

sop:�˻��ĺ�,easy to get(��ֵ��)

lec7 digital logic2

simplification: ������/kmap/Quine-McKluskey

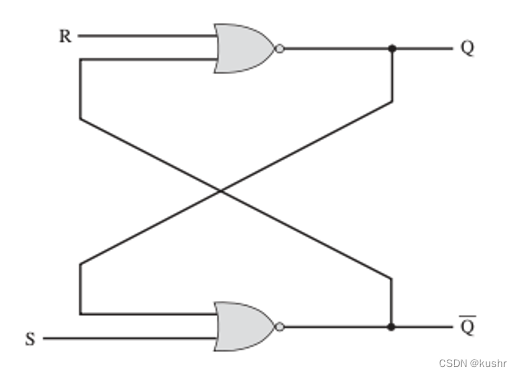

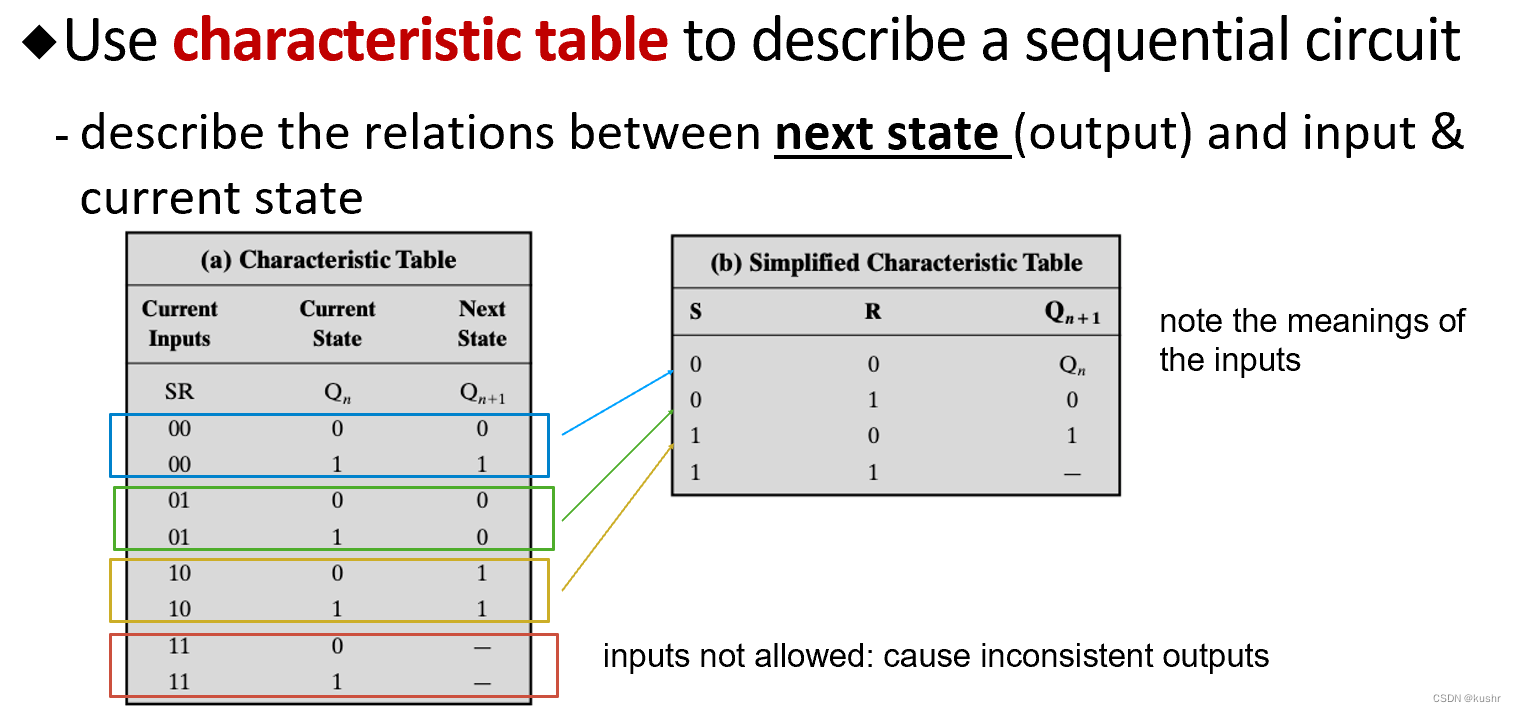

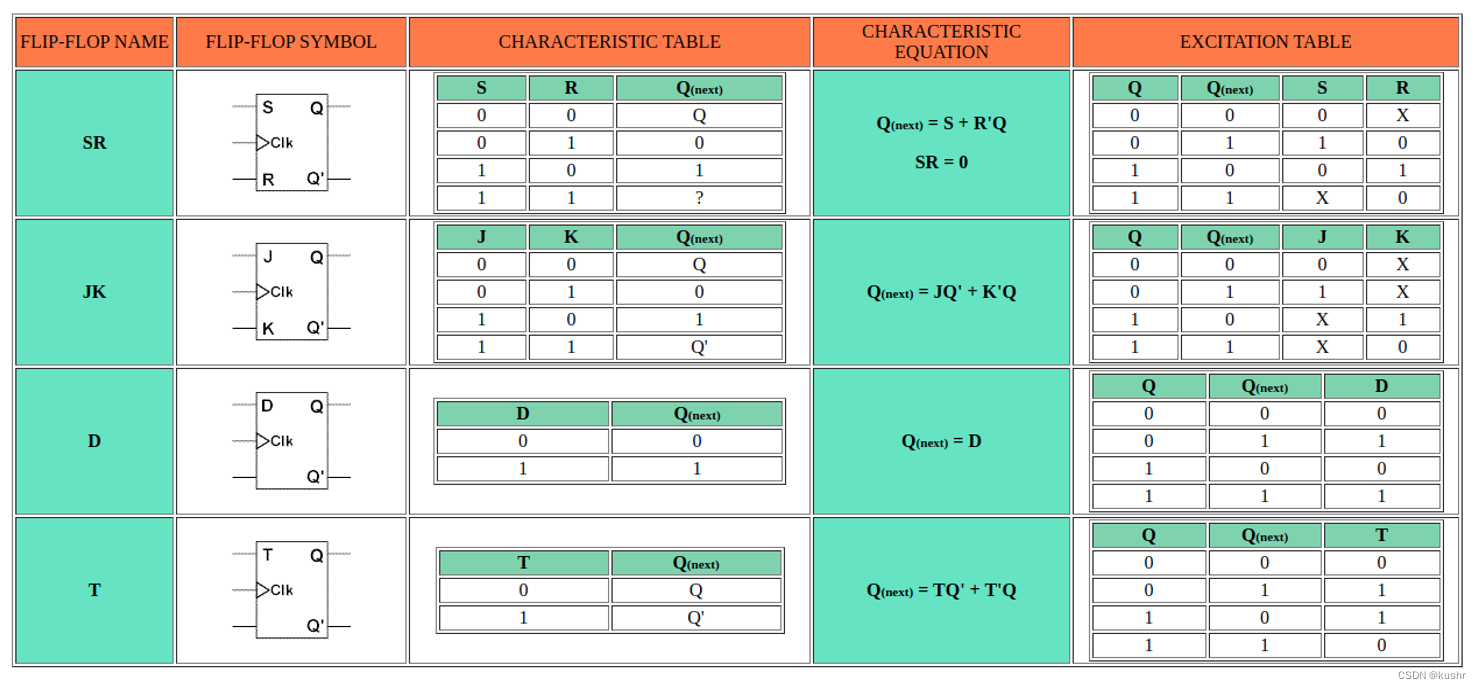

Sequential Circuits

������������һ���������

stable state:������벻��,���������

����˳��:

��sr flip-flopΪ��,֪��input sr��q,!q��,����s��q�����q,���ü�����ķ�q����q

����ó�sr��characteristic table

(s=1,r=1ʱq��q����ֵ��ͬ,���Բ��ܳ���)

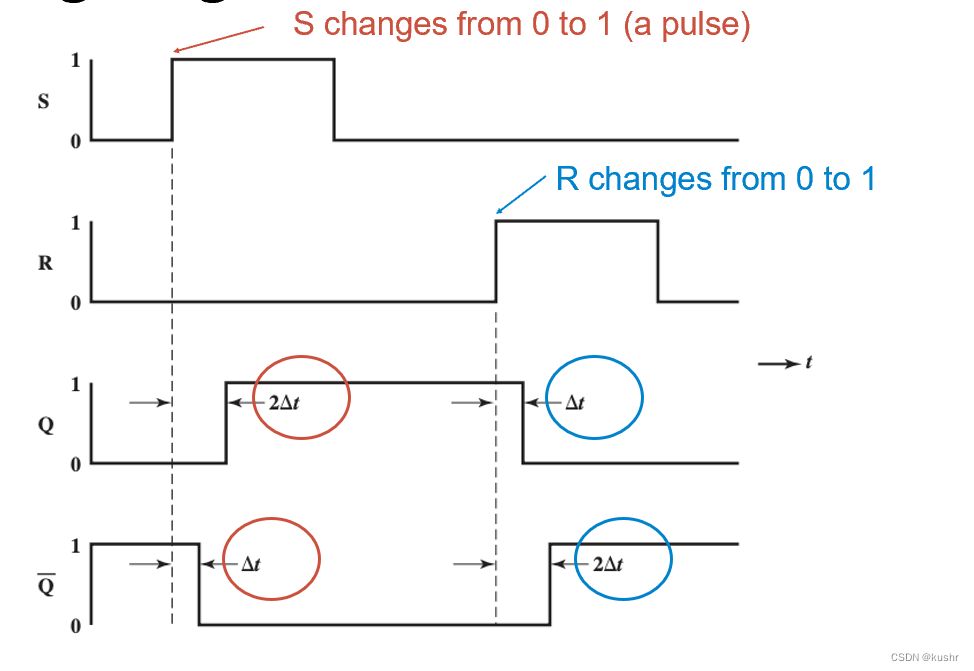

timing

gate��ʱ,���ܻᵼ�´���

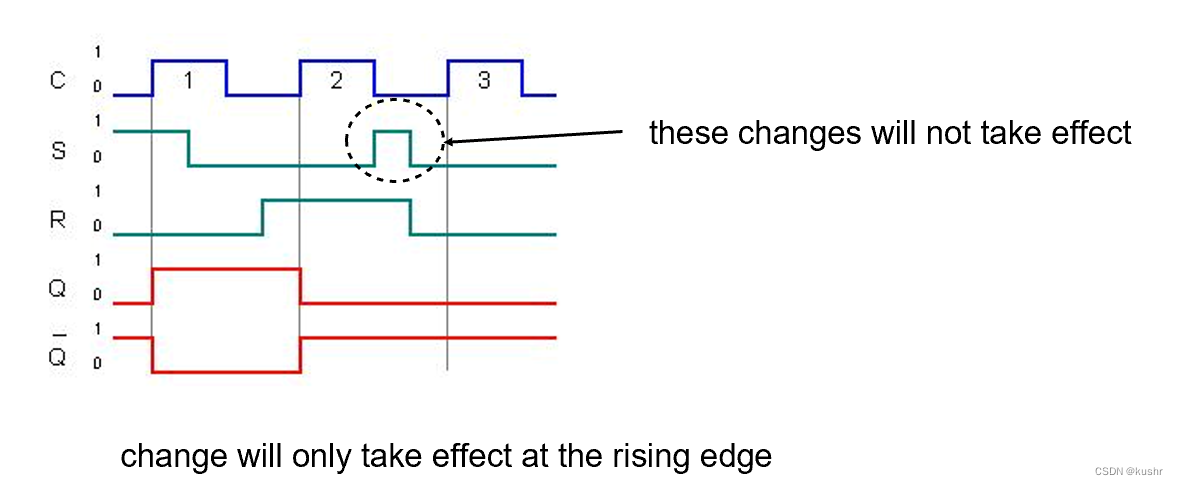

����������and����һ��clock:

�����positive edge triggered,��ֻ��clock��0��1ʱ�ı����Ч

other ff

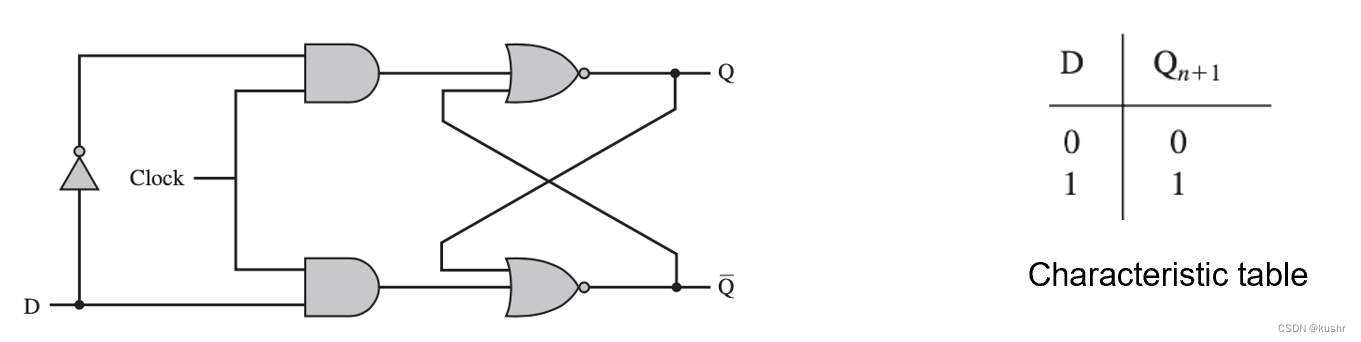

D-FF

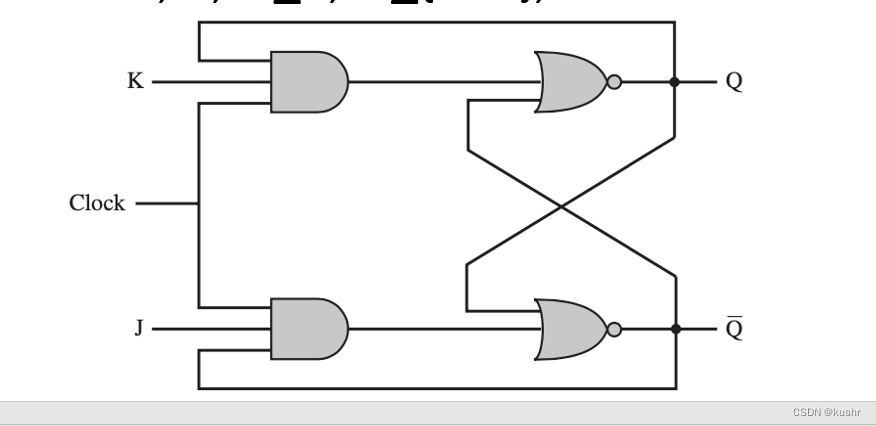

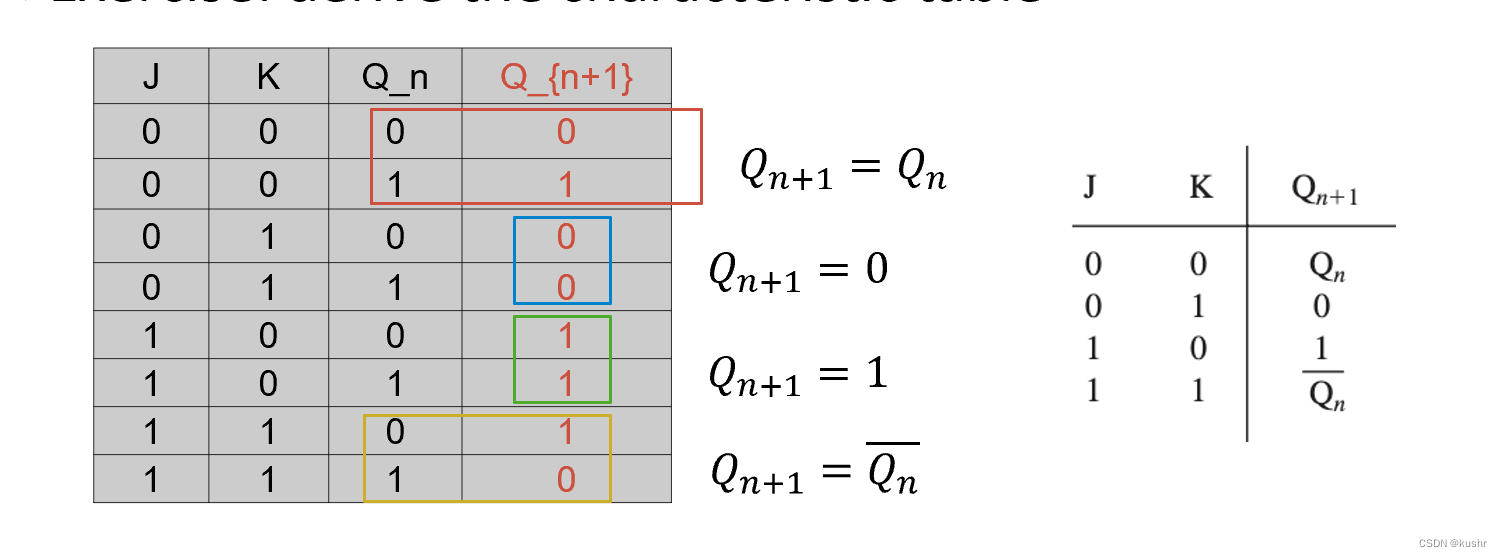

JK-FF

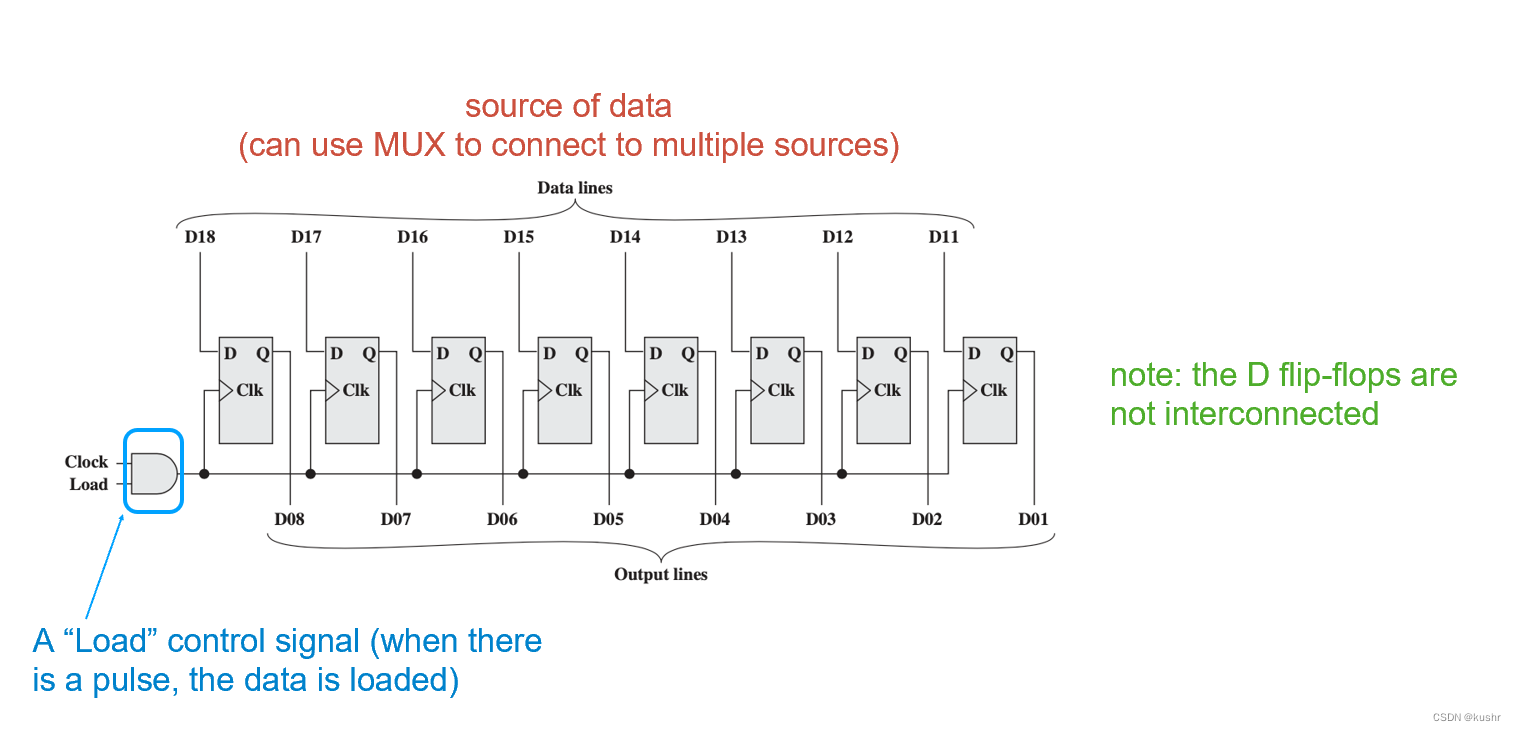

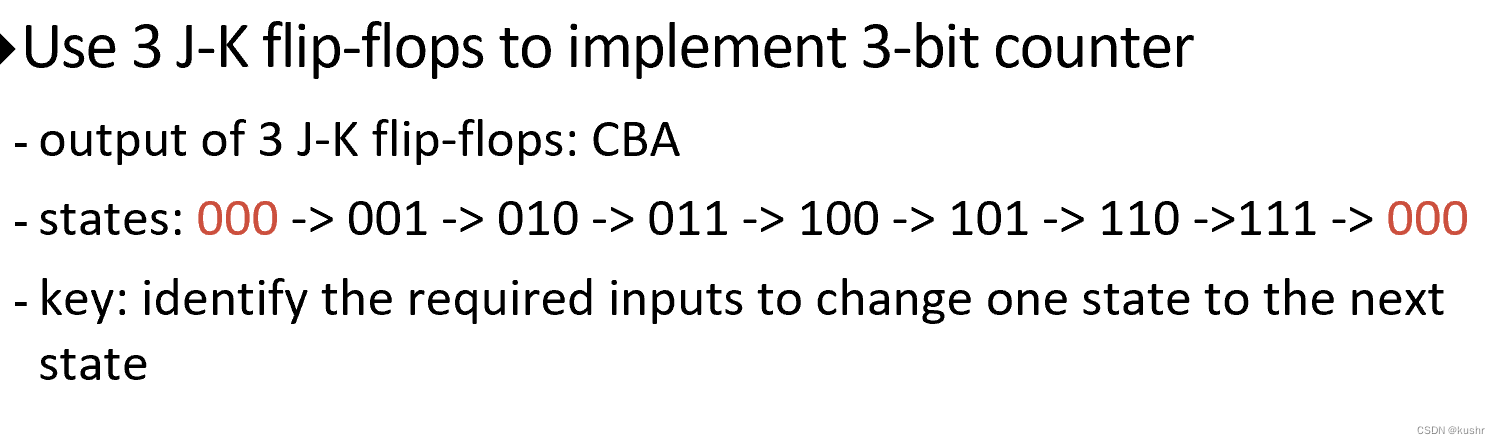

registers/counters

parallel register:ͬʱ�ı����

synchronous counter:states of flip-flops WILL change at the same time

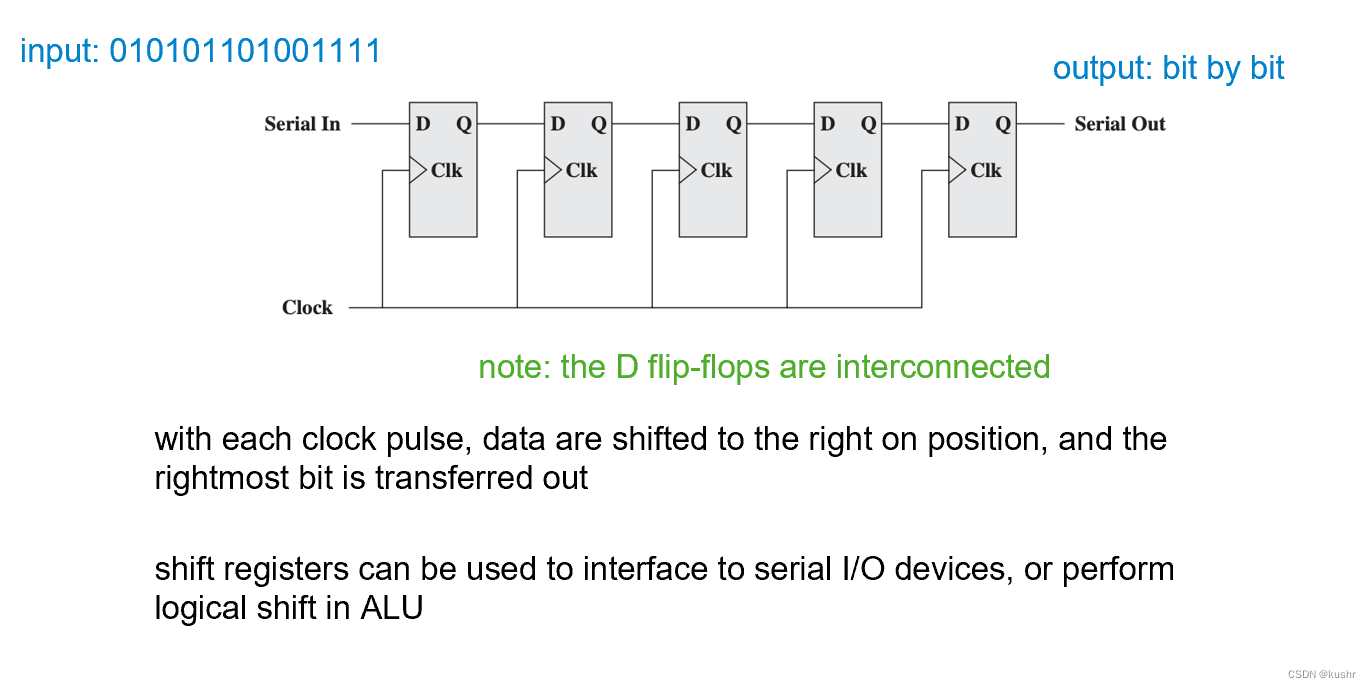

shift register: ���θı����:

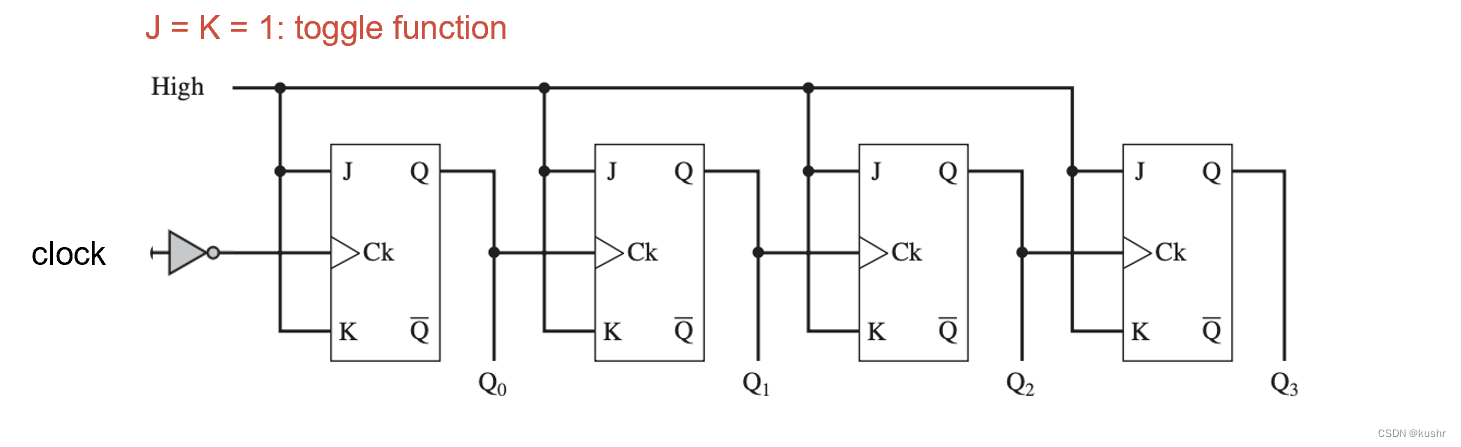

asynchronous counter:states of flip-flops will NOT change at the same time

asynchronous :ripple counter

j=k=1(q=!q), ǰһ��ff�������Ϊ��һ��ff��clock

synchronous counter

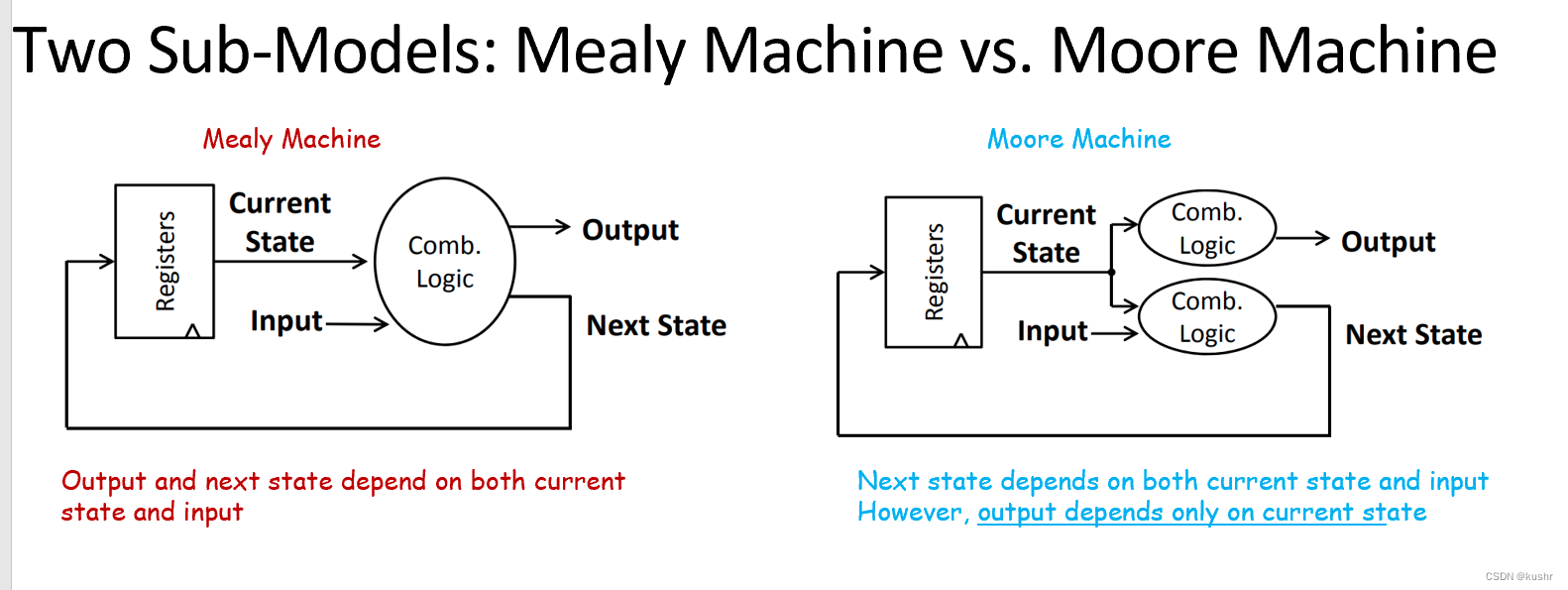

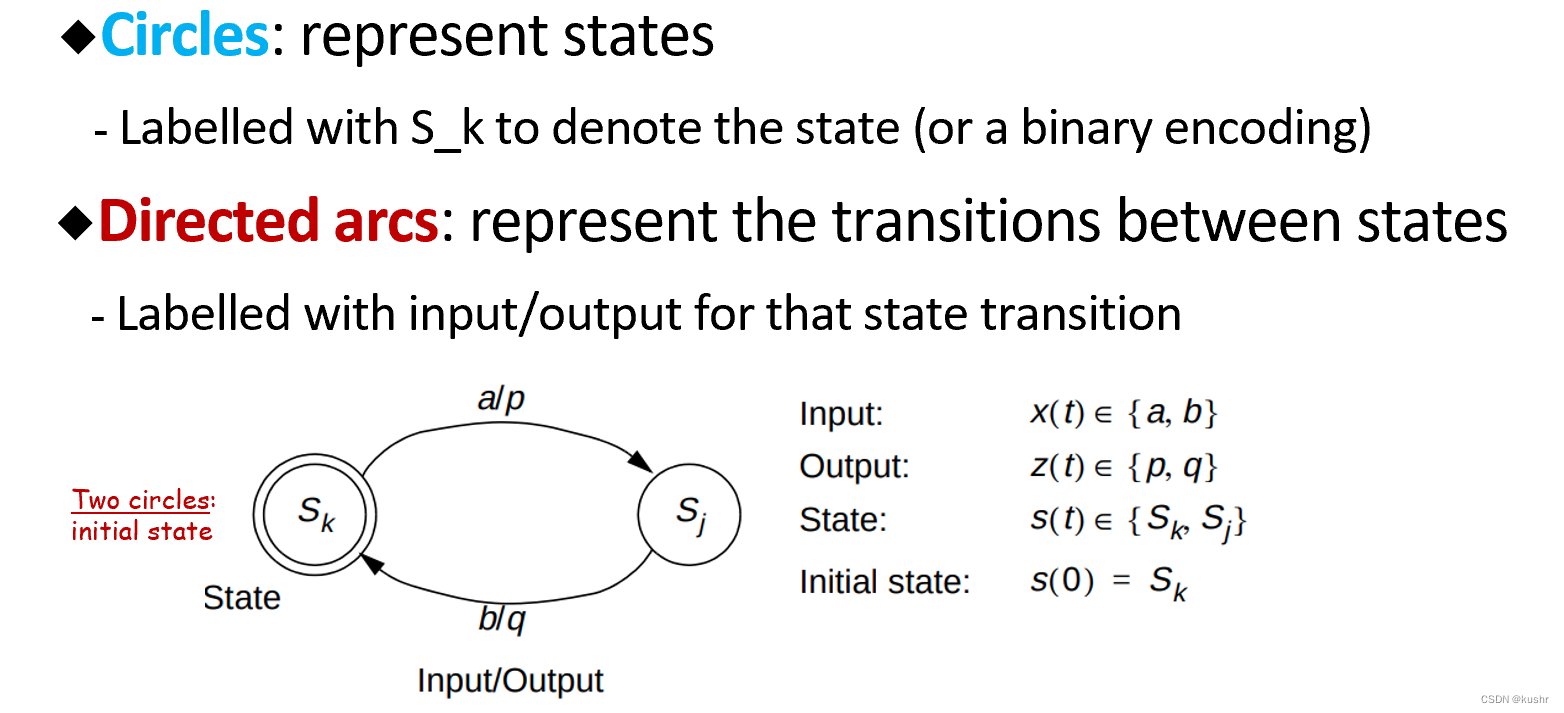

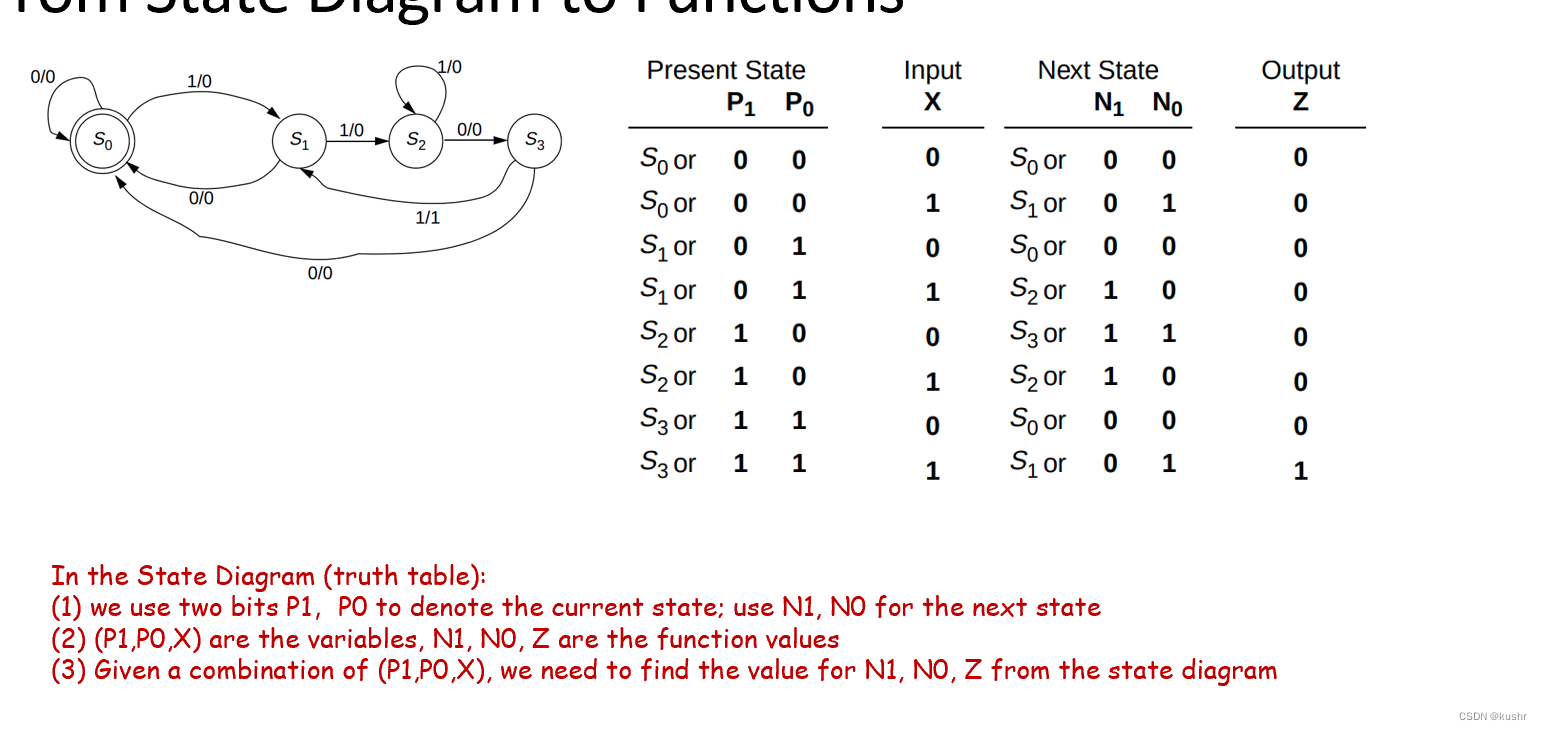

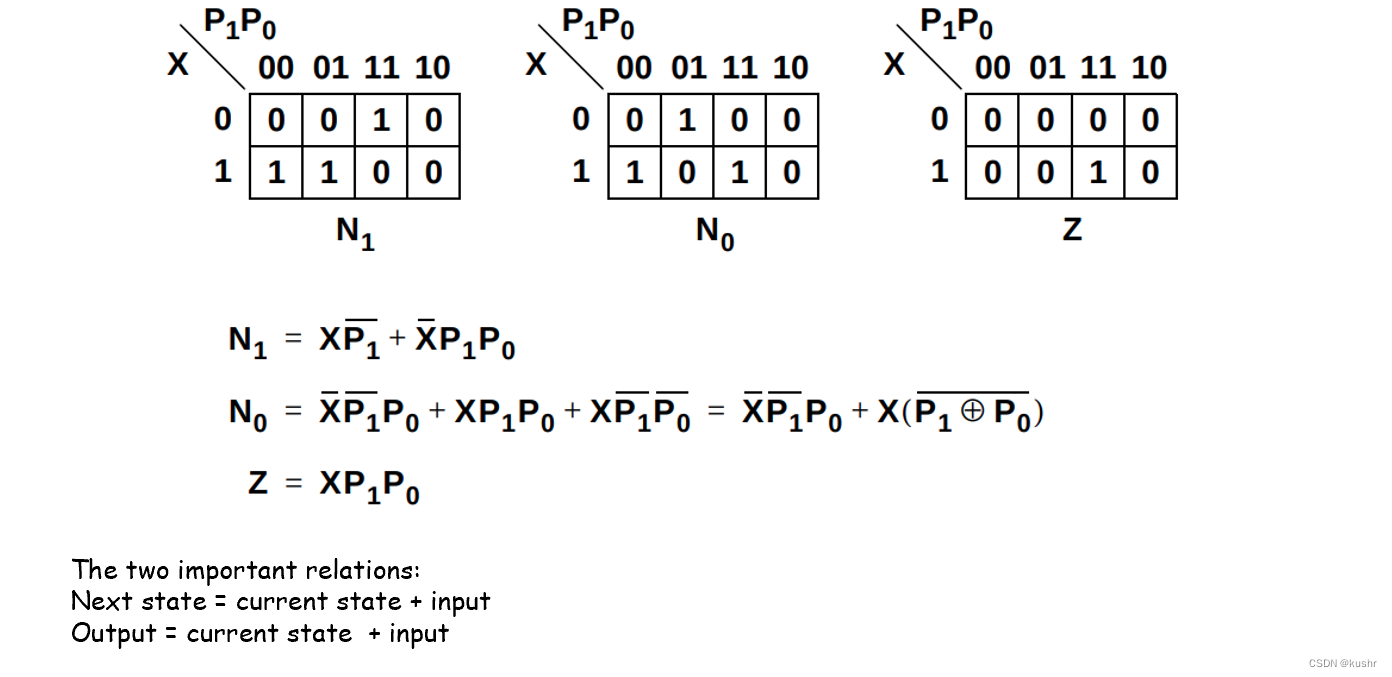

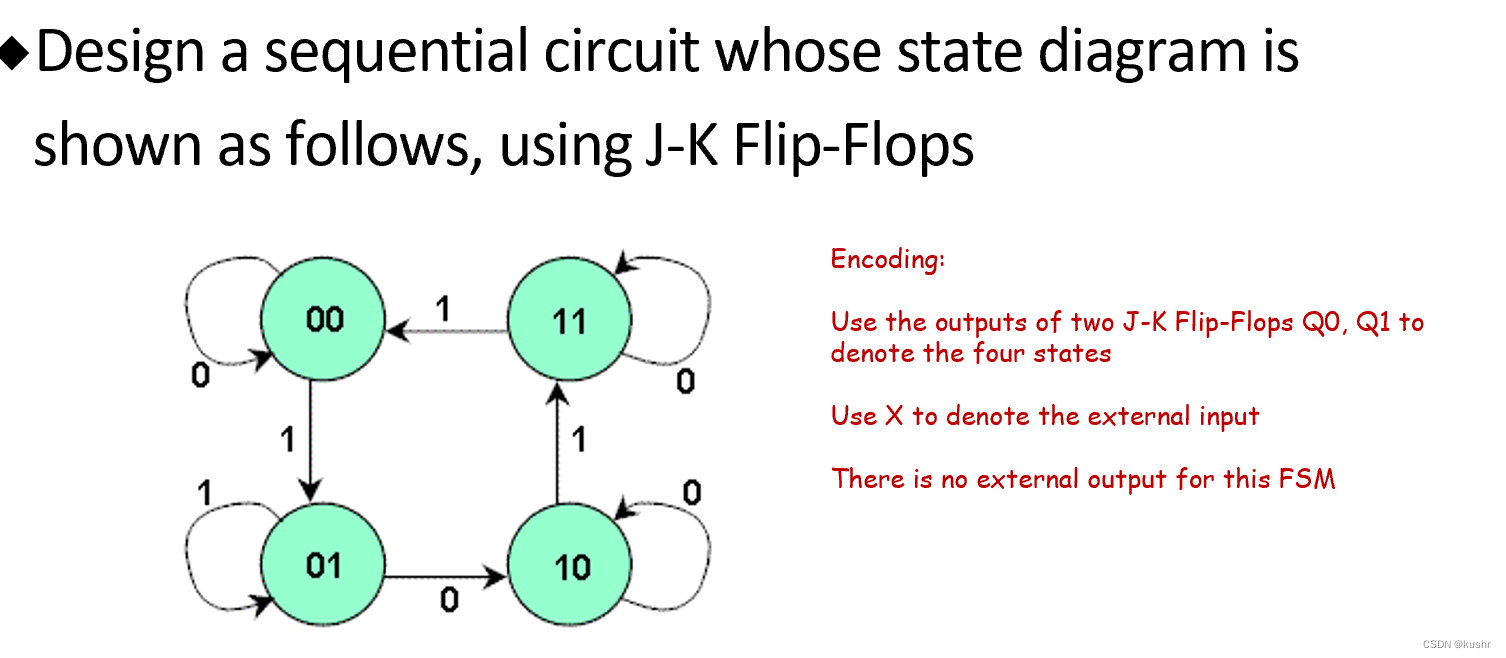

lec8 ����״̬��(FSM)/˳���·���

FSM

Next state = external input + current state

External output = external input + current state

diagram to table:

table to func:

Seq circuit design

һЩqnext������Ĺ�ϵ:

Design a sequential circuit

˳��:

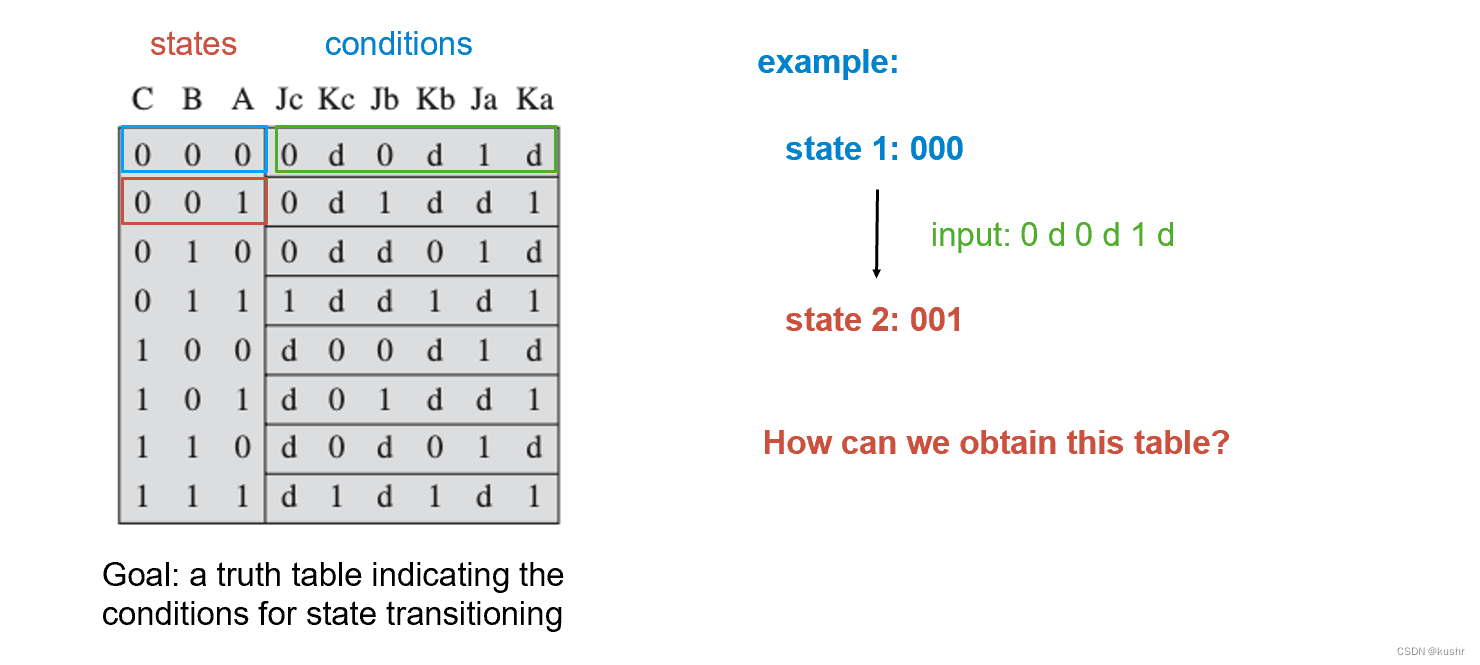

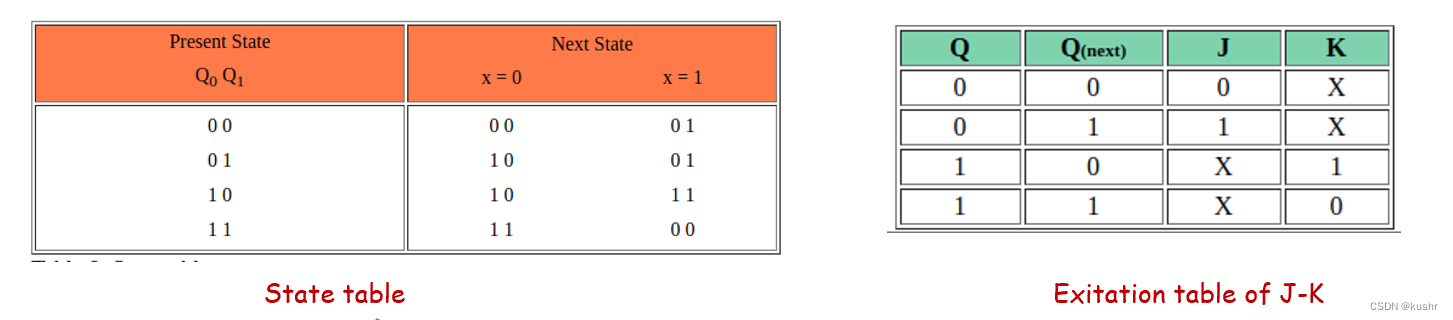

1��дFSM��table(present state,next state,input)

2���г�ff��excitation table(q,qnext,input)

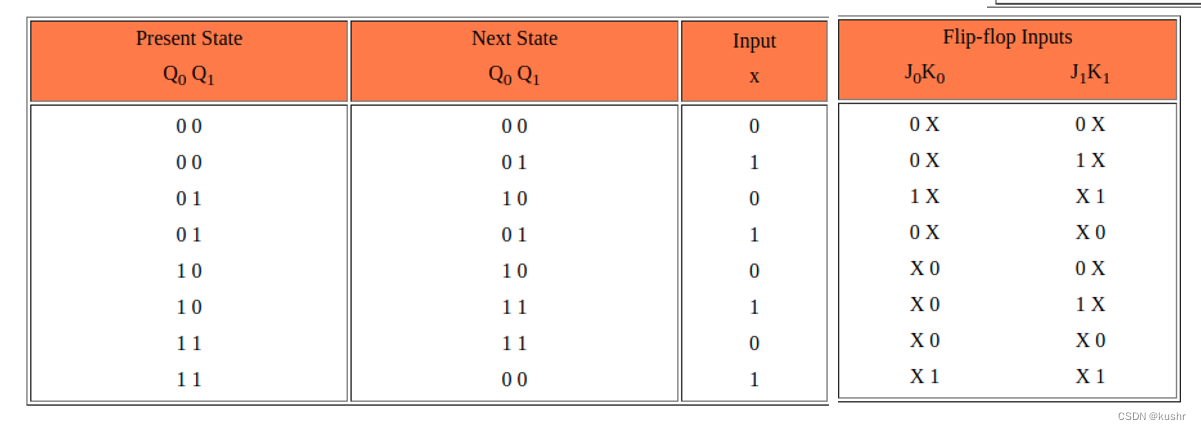

3������FSM table��present state��next state�Ĺ�ϵ,����ff table,�ҳ�ÿ��ff������

4���ɴ�table�еó�ÿ��ff�����switch func

5��������·ͼ

Example:

����1,2:

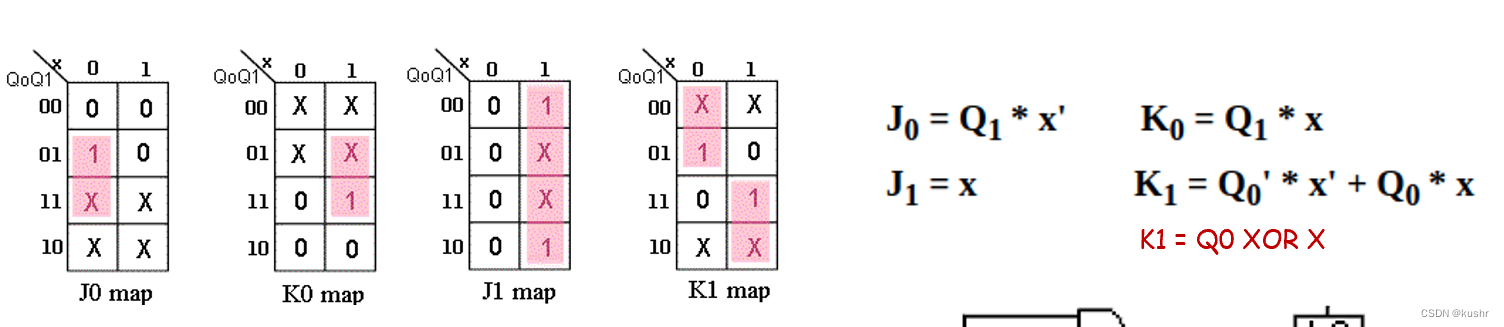

����3:

����:����������jk��ff,ff0��ff1,��˶�Ӧ�ĸ�����,j0,k0, j1,k1, ���ϱ��п��Կ���:

��һ����,q0��0�䵽0,��˸���ff table,j0k0�ֱ���0,x ��

q1��0�䵽0,��˸���ff table,j1k1�ֱ���0,x ��

�ڶ�����,q0��0�䵽0,��˸���ff table,j0k0�ֱ���0,x ��

q1��0�䵽1,��˸���ff table,j1k1�ֱ���1,x ��

��������,q0��0�䵽1,��˸���ff table,j0k0�ֱ���1,x ��

q1��1�䵽0,��˸���ff table,j1k1�ֱ���x,1 ��

���Դ�����

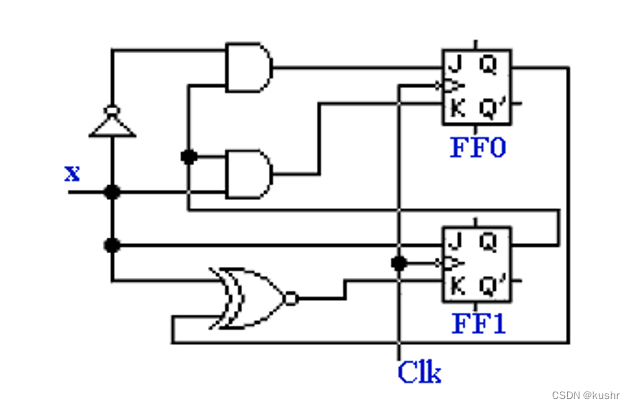

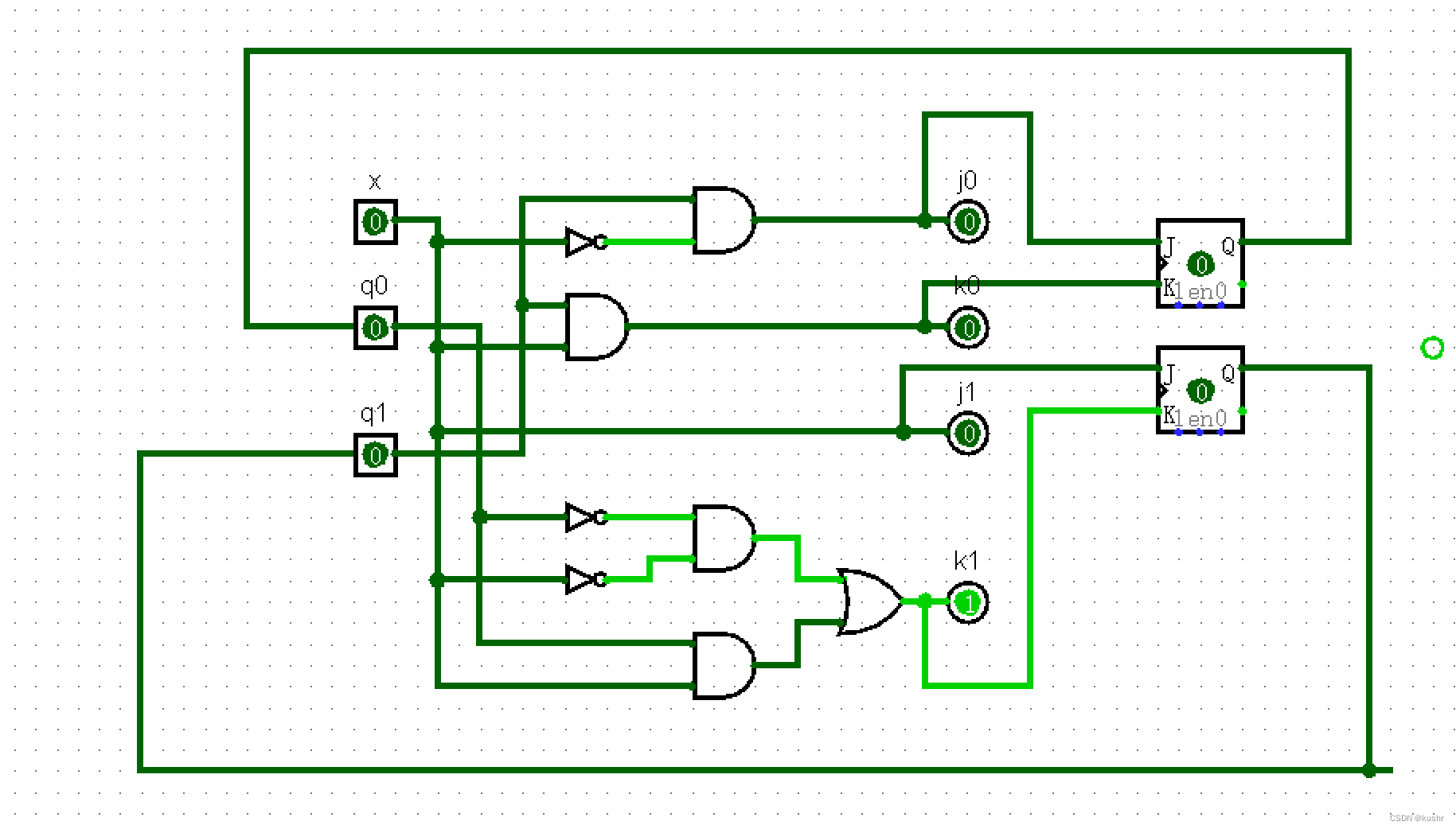

����4:��kmap(q0q1��present),��fuction

����5:����·

hint:��һ��������logism����boolean func ���

project-analyze circuit -table

ff��memory��(q0��q1����һ��û��С����,����ֻ�Ƿ��㿴)

lec9 Computer Memory (I):Memory hierarchy and Cache

- Memory can be categorized based on Technologies

- SRAM (Static Random Access Memory)

- DRAM (Dynamic Random Access Memory)

- PROM (Programmable Read-Only Memory)

- Magnetic Disk

Memory can be categorized based on Technologies

SRAM (Static Random Access Memory)

DRAM (Dynamic Random Access Memory)

PROM (Programmable Read-Only Memory)

Magnetic Disk

Measures of Performance �C Access Time (latency)

random access:һ��ָ��(��/д)��ʱ��

non random access:�ӷ���ָ�����ָ��ص��ʱ��

memory cycle time:ָ��1����ָ������Է����ʱ��

transfer rate:1/memory cycle time

**Physical features �C **

volatile:������(�Ĵ���,ram��)

non volatile:����(Ӳ��)

erasable:���Ա���д��ɾ��:register/Ӳ��(hard drive)

non erasable:���ܱ���д(ROM:read only),CD

internal: registers in processor, main memory, cache

external: the peripheral storage devices, such as disk and tape �C they are accessible to the processor via I/O controllers

memory hierarchy

1:expose hierarchy

programmer��������

2��hide hierarchy

cache memory

�ڿ���cpu�ĵط�

����cache-�Ҳ���ȥmemory(��block��),��word����cache

��С��λ:word

ÿ��word��n bit�ĵ�ַ,����memory��2^n����ʽ

block:����k��word;M=2^n/k blocks

cache��m��,ÿ�ж���k��word(block���е�����)

cach����m��,memory����M��block,m<<M��

mapping

direct mapping

ע��,cache��һ��line��ֻ�ܴ���һ��block

�ڴ��block�����䵽�涨��cache line

����,q=m/M,q��block�����䵽һ��cache line��

Equivalently, the mapping can be implemented through modular operation:

w:word number within block (2^w words)���еڼ�����

s:s bits = block number (2^s blocks)�ڴ�ڼ���

r:identify the line number in Cache(2^r line in chache)����ڼ���

s-r:Tag for a line in Cache: which block this line is currently storing

s-r = cache line number, s = main memory block number, r = number of lines in cache

s(��Ӧ����) mod(2^r)=r

��С��λ:byte

associate mapping

���̶�

address = s + w bits; 2^s blocks in memory

measurement of cache

miss rate: l1<0.01, l2 0.03-0.05��

Replacement Algorithms for Associative Mapping

Least Recently Used (LRU)

First-in-first-out (FIFO)

Least Frequently Used (LFU)

lec10:Internal and External Memory

internal

memory cells:

ram

dynamic ram cell(DRAM):��Ҫrefresh

static RAM cells

����Ҫrefresh

DRAM vs. SRAM

Common: volatile �C need continuous power

Difference:

DRAM cell is simpler and smaller, thus denser (more cells per unit area) and less expensive

however, DRAM requires the supporting refresh circuitry

DRAM tends to be favored for large memory requirement

DRAM for main memory, SRAM for cache

rom:Read-Only Memory

���ɸı䲻��ɾ��

Usage

system programs

library subroutines for frequently wanted functions

Programmable ROM (PROM)

Read-Mostly Memory (a variation of ROM):EPROM��EEPROM��flash memory

Erasable Programmable ROM (EPROM)

chip logic