1ЁЂЮБЫцЛњађСа

????????ШчЙћвЛИіађСа,вЛЗНУцЫќЪЧПЩвддЄЯШШЗЖЈЕФ,ВЂЧвЪЧПЩвджиИДЕиЩњВњКЭИДжЦЕФ;вЛЗНУцЫќгжОпгаФГжжЫцЛњађСаЕФЫцЛњЬиад(МДЭГМЦЬиад),ЮвУЧБуГЦетжжађСаЮЊЮБЫцЛњађСаЁЃ

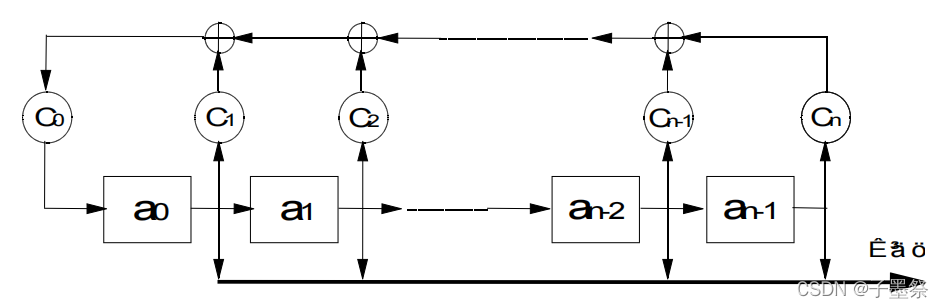

????????ЮБЫцЛњађСагжГЦЮЊЮБЫцЛњТы,ЪЧвЛзщШЫЙЄЩњГЩЕФжмЦкађСаЁЃЫќВЛНіОпгаЫцЛњађСаЕФвЛаЉЭГМЦЬиадКЭИпЫЙдыЩљЫљгаЕФСМКУЕФздЯрЙиЬиеї,ЖјЧвОпгаФГжжШЗЖЈЕФБрТыЙцдђ,ЭЌЪБгжБугкжиИДВњЩњКЭДІРэ,вђЖјдкЭЈаХСьгђгІгУЙуЗКЁЃ

????????ЮБЫцЛњађСаЕФВњЩњЗНЪНКмЖр,ЭЈГЃВњЩњЕФЮБЫцЛњађСаЕФЕчТЗЮЊвЛЗДРЁвЦЮЛМФДцЦїЁЃЫќгжПЩЗжЮЊЯпадЗДРЁвЦЮЛМФДцЦїКЭЗЧЯпадЗДРЁвЦЮЛМФДцЦїСНРрЁЃгЩЯпадЗДРЁвЦЮЛМФДцЦїВњЩњГіЕФжмЦкзюГЄЕФЖўНјжЦЪ§зжађСаГЦЮЊзюДѓГЄЖШЯпадЗДРЁвЦЮЛМФДцЦїађСа,МђГЦ m ађСа,вЦЮЛМФДцЦїЕФГЄЖШЮЊ n,дђ m ађСаЕФжмЦкЮЊ 2n-1,УЛгаШЋ 0 зДЬЌЁЃ

????????Цфжа,ЮБЫцЛњЪ§ЗЂЩњЦїЕФГѕЪМзДЬЌашгЩЮЂДІРэЦїЭЈЙ§DМФДцЦїИјГіЁЃ

2.гВМўЕчТЗ

????????ЮБЫцЛњађСаЗЂЩњЦїЕФГѕЪМзДЬЌЪЧгЩЮЂДІРэЦїжа DМФДцЦїЬсЙЉЕФ,ЖјDМФДцЦїЕФЮЛЪ§ЮЊ 8 ЮЛ,ЫљвдашвЊЩшМЦвЛжж 8 ЮЛЕФЮБЫцЛњађСаЗЂЩњЦї,ЫќЕФБОдЖрЯюЪНЮЊ:

????????F(x) = x8 + x4 + x3 + x2 + 1

ЮБЫцЛњађСаЗЂЩњЦїНсЙЙШчЯТЭМЫљЪО:

?VerilogДњТы:

module random_num(

input clk,

input rst,

input en,

input [7:0] d,

output [7:0] ran_num

);

integer i;

always @(posedge clk or posedge rst)begin:loop

if (rst)

ran_num <= ?8'b0;

else if(en)

ran_num <= ?d;

else begin

for(i=1;i<8;i=i+1)

ran_num[i] <= ?ran_num[i-1];

ran_num[0] <= ?ran_num[1] ^ (ran_num[2] ^ (ran_num[3] ^ ran_num[7])) ;

end

end

endmoduleЗТецНсЙћ:

?