������֤�����뷽��ѧ��Ҫ(һ)- ������֤����֤ƽ̨

??���´�оƬ�����������,���۹�����֤�����������е�λ�ü��������ǵ�����,������Ŀǰ���еĸ�����֤��������֤����ѧ,�����ܳ��õ���֤����SystemVerilog��E��PSL��SystemC��Vera��

1.1 ������֤����֤ƽ̨

??��֤��Ҫ����������֤��������֤��ʱ����֤��,������Ҫ�������֤,���оƬ��ƶ������Ϊ���ܽ�����֤,ȷ������ܹ�����ʵ��Ԥ�ڵ�Ч����ͨ����֤���ԡ�Ӳ���������Ի�C���Եȿɴ��֤ƽ̨(testbench)��

??��֤ƽ̨��Ҫ����㹻���Զ������������ÿһ����������(test case)�Ĺ��ܸ����ʺͼ��ٴ�������������ʱ�䡣��������ܻ����Ӳ���ƽ̨�ĸ��ӶȺ�Ͷ���ʱ�䡣

1.1.1 ר��оƬ�������

??��ͼ1-1��,���ܲ��Ա�����һ��������ģ��,ʵ���а����˶�������������������Ի��������в�����������֤����Ҫ������������ǵ��ȸ��ӵĹ��̡�

??��ͼ�п��Կ���,��֤���趨�淶��ɺ�Ϳ��Կ�ʼ��,һ�ֳ�������ͼ���,�����ܶ�����³�����ͼ��ɽΡ�

1.1.2 ʲô����֤

��֤��ȷ����ƺ�Ԥ���������һ�µĹ���,���ͨ����ͨ��һ��������ƹ淶������ġ�����ר��оƬ���,�ڲ�ͬ���в�ͬ����֤��ʽ:

(1)�Ĵ������伶(register transfer level,RTL)�Ĺ�����֤��

(2)�ż��ķ���,Ϊ����֤�ۺϺ�������Ƿ�������Ĺ���һ�¡�

(3)��ʽ��֤(�ȼ��Լ��)��ȷ���ż�������RTL�����һ���ԡ�

(4)ʱ����֤,Ϊ����֤����ܷ����ض���Ƶ��������,ͨ�����þ�̬��֤���ߡ�

??�����ᵽ����֤(verification)��Ϊ�Ĵ������伶(RTL)�Ĺ�����֤��������֤��ר�ü���оƬ��������й�ע��Ƶ���Ϊ,�������еĹ��ܶ������� RTL��α���֤��

??ͼ 1��2չʾ��һ���߲�εĹ�����֤��ͼ��һ��ר�ü���оƬ��ƿ��Ա�����ӵ��һ ϵ�����������ļ���,��Ƶ�����ǻ�����Ƶ�����͵�ǰ��״̬���ڹ�����֤�Ĺ��� ��,����ʦ�ڱ������(design under test,DUT)����֤ƽ̨����֤ƽ̨������Ӧ�� һ�����߶�����Լ���,�����������͵���Ƶ������С���������ͨ����֤ƽ̨����,����ͨ���ֶ����������,��������бȽ�,������Ƿ���ȷ�����������ͨ����֤ƽ̨�� �ű������ֹ���ʵ�֡�

1.1.3 ��֤ƽ̨������Щʲô

??��֤ƽ̨����Ҫ��������:

(1)����������

(2)�Ѽ���Ӧ�õ���������С�

(3)���������֤�����Ƿ�ͨ��,Ҳ����ȷ��������Ƶ����������һ�¡�

-

����������;��

??������ֶ����Ƽ������û���������Ҫ�������Ƽ�����������������Ƶ������е�1 ��1����,��ͼ1-3��ʾ;�û�������һ�������û���ָ��(���źŸ�ֵ��������ͨ���Ժ�����������ĵ���)����֤ƽ̨��������ijЩ�������ڴ�ͳ����֤ƽ̨��,�����Ƽ������û�����������һ�µġ�

??�����û�������;���кܶ���,������ֱ�ӵ�,Ҳ����������ġ���������Ǵ��û� �ṩ��ȷ������,�������ν��ֱ�Ӳ���(direct test)����������Ǹ��������������,�������ν���������(random test)��

??��ͳ��֤ƽ̨��������:����һ��ʱ��˳��Ѷ������������뵽��������С�

??����֤ƽ̨��������:�����ڸ��߲�α��û�����ģ����װ��

??������һ���洢���Ķ�д������ֱ�Ӳ��Ժ�������������

��ֱ�Ӳ���

??��ͳ�ֹ�����ֱ�Ӳ���,��ͨ������ÿ���źŵ���ֵ��ʵ�֡�

������������

??ͨ���Լ�������֤�ܹ����зֲ�߲� ����ģ,Ҳ������ν��������֤(transaction based verification),�� �� �� �� ��rd_mem,wr_mem���ַ�װ�õ������,�������������Խ������ɵĸ߲㼤��(������һ�����ݵļ���)���ݸ���,��ͼ 1-4��ʾ,�������Դ�������������Ч�ʡ�

??��һ�����Ӹ�����֤ƽ̨��,�������Ը����û�ָ����Լ��,��ȫͨ����֤ƽ̨�� ������,�����ν��Լ�������������(constrained random stimulus generation),��ͼ 1-5��ʾ������,�û�Ҫ�Ѱ��Ĵ�СԼ����64���غ�1522����֮��,����������֮����һ��Ȩ�����÷�������֤ƽ̨�������Զ����ɺͽ������ע�뱻������С�

-

Ӧ�ö����Ƽ���

??����,��֤ƽ̨����һ�����߶����������ע�뱻������С���֤ƽ̨ͨ���߲�ε� ����Ӧ�ø߲�ε��û�����,�����Ƽ�������֤ƽ̨���ɲ���ͨ����Ӧ�Ľӿڷ��͵����� ����С�����֤ƽ̨��,ʵ�����ֹ��ܵ���֤���(verification component,VC) ����Ϊ��������(transactor)�������߹���ģ��(Bus Function Model,BFM)���ڱ�����,���Dz� ������������Ϊ������ -

������

??���ɺ�Ӧ�ö����Ƽ������������������֤ƽ̨����Ҫ������,��֤��Ŀ���Ǽ������Ƿ���Ԥ��һ��,Ҳ���ǽ����顣������ķ�����:

(1)**���δ��ڼ��:**�����ڼ����,���ܳ�����Ϊ����,���Ҳ����������������Ҫ�ع����,��ôһ���̶��ϵ��Զ����������DZ�Ҫ�ġ�

(2)**ͨ���Զ����ĺ����Ƚ�:**��¼������Ƶ����,ͨ�����нű����ȶԽ������������dz��õ�һ���ֶ�,�Ȳ���Ҫ����̫�����,�ֲ���Ӱ�����Ч��(����Ĵ�ӡ��Ϣ���ܻᵼ�·����ٶ��½�,��Ϊ���ļ�I/O��������)�����ӵ������,���뿼��Ҫ��ӡ����Ϣ,����̫����ɹ������־�ļ������Կ���ͨ���߲��������¼��Ϣ,�Լ�����־�ļ���

??�����������һ���ô�����,�������������������ʵ�ֺ���,��C/C++��perl������ֻ���ڲ��Խ���֮����ܽ���,�����Ļ���Ҫ���½��з���,�˷Ѻܶ�ʱ�䡣

(3)**��һ��ʵʱ�ļ�������Լ�ʱ�Զ����:**ʵʱ�ļ������ҪͶ�����Ŀ���,Ȼ�� �����൱����,�ر��Ƕ��ڵ���,һ�������ȶԴ���,���ǿ���ͨ�����ô����־���ߴ� ӡ��Ϣ�����û�;���κ�ʱ��,����������֤ƽ̨��״̬���û���ȫ�ɼ�,�����ڷ����� ���ʱ��,ͨ��ֹͣ����������̵������ڡ�

Ŀǰ�϶�Ӧ�ú�����ʵʱ���ִ�������,��ȡ������Ƶĸ��ӶȺ� �ӿڵ���Ŀ�Լ���֤ƽ̨��Ӧ�ò�Ρ�

1.1.4 ������֤����

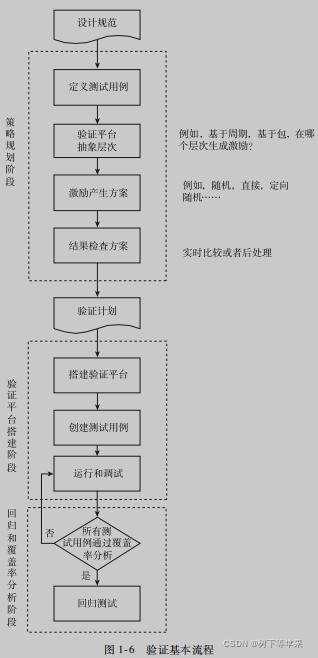

??ͼ1-6��ʾ�˹�����֤���̡������֤���̿��Ա��ֽ��������Ҫ��:(1)�ƶ���֤���Ժ���֤�ƻ�;(2)������֤ƽ̨,���к͵���;(3)�����ʷ����ͻع���ԡ�

1.���ƶ���֤���Ժ���֤�ƻ���

�ƶ���֤���Ժ���֤�ƻ�����Ҫ���������������⡣

(1)��Ҫ���ܵ�Ͳ�������

??���������Ҫ�IJ��Ե�dz���(�����Կռ�ܴ�),�ɴ����ڸ�,�����Ҫ�����Կռ���С��һ�����Թ����ķ�Χ,���Ҳ�����������;�����Щ���ܵ�,���ǽ����ݾ����� ���ⶨ��֤���ԺͲ�������,�����廯��һ����ϸ�ġ���ִ�е���֤�ƻ���,��Ϊ���� ��֤������ָ����

(2)��֤ƽ̨�ij�����

??��֤ƽ̨�ij����ν���������Ҫ�Ĵ�������:���ء������߸��߲�ε��������͡� �߲�εij���ģ��������֤ƽ̨�еͲ�εĹ����Զ�����

(3)�������ɺͽ�����ԭ�� ��Щԭ���������뵽��֤ƽ̨�ļ���������ṩ��,�������μ���,���жϲ� ����ͨ������ʧ�ܡ�

2. ��֤ƽ̨���

??���ǵڶ�����,Ҳ������֤ƽ̨�Ĵ,��д���������͵��ԽΡ��������, ��д��֤ƽ̨����Ͳ�����������֤ƽ̨��������չ,��Ϊ�����������ϱ����ӽ������� ��,��֤ƽ̨�ĴҪ�Կ�����Ϊ����ԭ��,�����ܹ�������ƹ���ʦ����֤����ʦ���� ����������

3. �ع���Ժ�����������

??һ������ȫ�������������ɹ�����,��֤�ͽ����˻ع���� (regressiontest)������ �����Ρ��ع����Ҫ���ܹ����ڵ�����������,���Ǽ��������ܹ����õ�����,�ɹ� ����ʧ���ܹ��Զ���顣��������ʾ������Ʊ����Եij̶�,����֤��������Ҫ����

??�������,���еIJ���Ӧ����ÿ�����ÿ�����ع���������Ե����С���ƻ����� ֤����ʦӦ�ò鿴������,�Ӷ��Ļ������Ӹ���IJ���������Ŀ���Ǵﵽ 100%,���߾� ���ܴﵽ 100%��

??��ͬ������в�ͬ����֤������������һ�����κ���ƶ�Ϊ��õ���֤���̡�ÿ���� �ƶ����䲻ͬ�ĵط�,��������������֤���̡���������,���������ͽ�������Կ��ܽ����ᱻ��ʾ�Ķ��塣���ǿ������������߲�ε���������,��֤ƽ̨ʹ�ô�ͳ��ֱ�Ӳ���,������Ҳ���ܲ�����顣���ڸ��ӵ����,���еļ������ɷ������߽����������Ԥ�ȶ���õġ�һ����˵,������Щ��Ƶ���֤ƽ̨�� ����һ���ϸߵij������ϲ�����

??��֤����ͬ��Ҳ����ȡ���ڱ���֤��ƵIJ��,Ҳ����������֤����ģ�Ĵ��롣�� ��,һ��оƬ���Էֽ�Ϊ����ģ�顣Ϊ��,����Ϊÿ��ģ��һ����������֤ƽ̨,ͬ ʱ������һ����֤ƽ̨��оƬ������֤��ijЩ���,оƬ������һ��ϵͳ,���ܴ��ڼ��� оƬ������ϵͳ������֤ƽ̨��

??ÿ��ģ�鼶����֤ƽ̨��Ҫ��Ŀ���ǰ������Ը���ģ���е�ʵ��,ʹ���ɵ�оƬ�и� ������,Ȼ��оƬ������֤ƽ̨��Ҫ���Ե��Ǹ���ģ��֮��Ľ������ܡ�

�ο��鼮:SystemVerilog�빦����֤