5.1 CPU的功能和组成

?

1.CPU的功能

指令控制(程序的顺序控制)操作控制(一条指令由若干操作信号实现)时间控制(指令各个操作实施时间的定时)数据加工(算术运算和逻辑运算)?2.CPU的基本组成

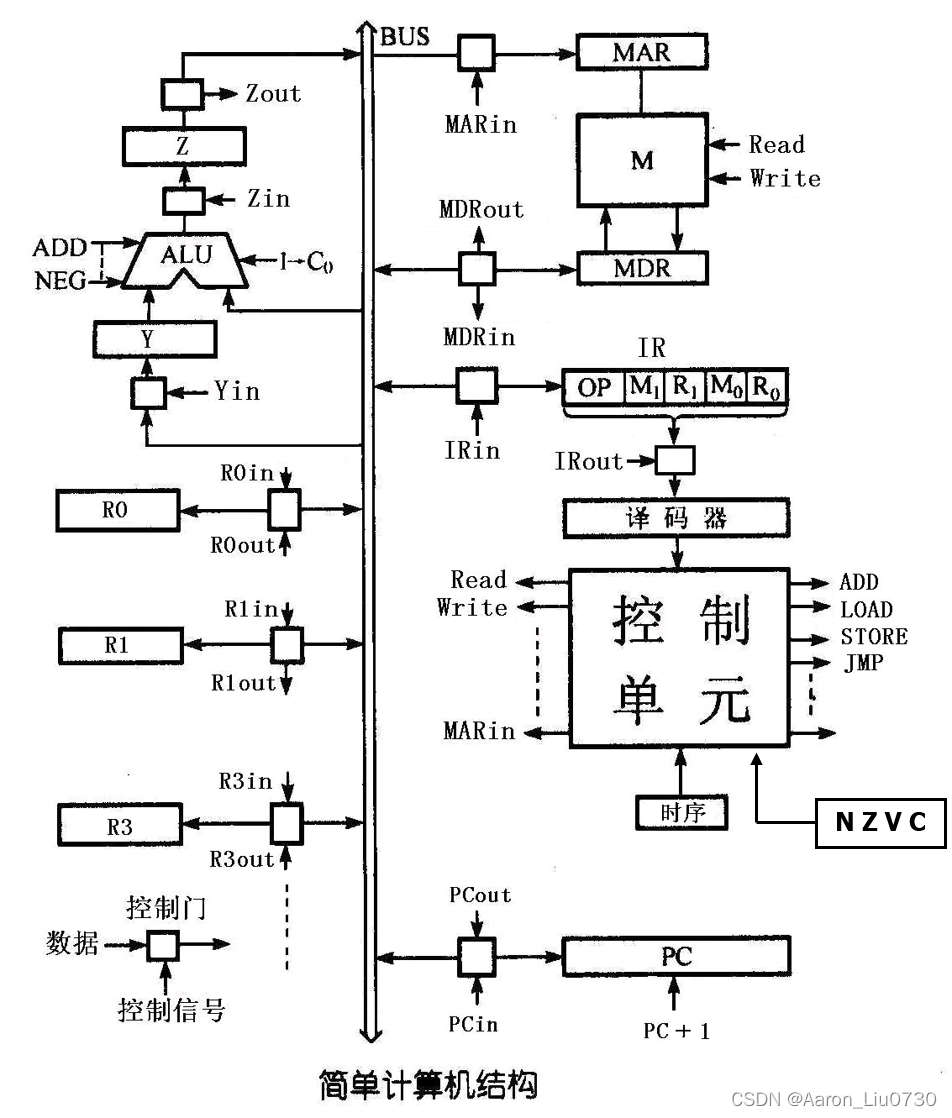

中央处理器 CPU= 运算器 + 控制器运算器ALU累加器暂存器控制器程序计数器 (PC) 、指令寄存器 (IR) 、数据缓冲器 (DR) 、地址寄存器 (AR) 、通用寄存器、状态寄存器 (PSW) 、时序发生器、指令译码器 (ID) 、总线

3.CPU中的主要寄存器

DR 缓冲寄存器 / 地址寄存器 ARn 中转站补偿速度差别IR 指令寄存器PC 程序计数器PSW 程序状态寄存器AC 累加器通用寄存器

中转站补偿速度差别IR 指令寄存器PC 程序计数器PSW 程序状态寄存器AC 累加器通用寄存器4.操作控制器

数据通路 : 各个部件之间传送信息的通路。操作控制器可分为时序逻辑型、存储逻辑型、时序逻辑与存储逻辑结合型三种硬布线控制器 ( 组合逻辑 ) 是采用时序逻辑技术来实现的微程序控制器 ( 存储逻辑 ) 是采用存储逻辑来实现的;混合类型 前两种方式的组合

5.2 指令周期?

指令周期? CPU 从内存取出一条指令并执行这条指令的时间总和。CPU 周期?? 又称机器周期, CPU 访问一次内存所花的时间较长,因此用从内存读取一条指令字的最短时间来定义。时钟周期? 通常称为节拍脉冲或 T 周期。一个 CPU 周期包含若干个时钟周期

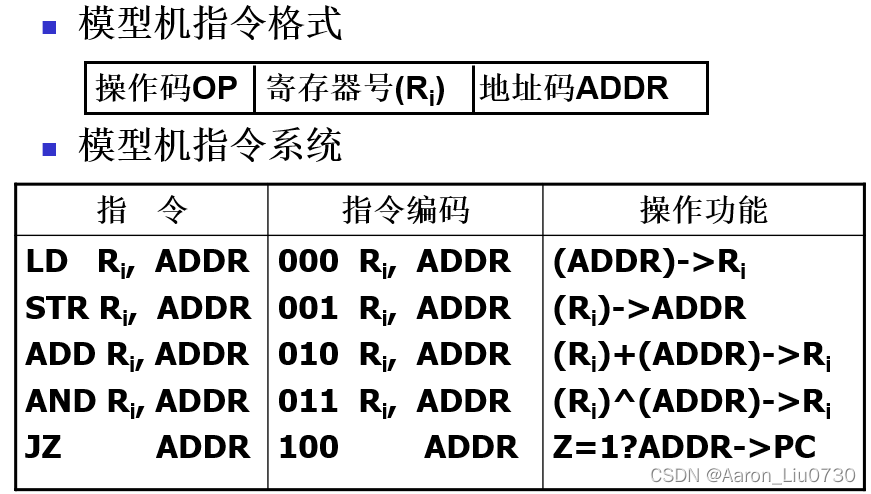

下面我们用一个模型机来介绍指令周期概念

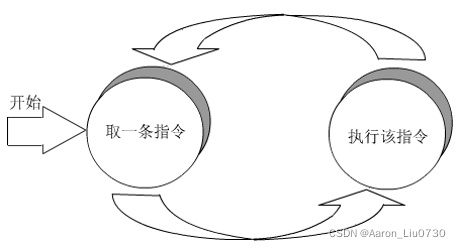

主要包括:取指(令)周期、(指令)执行周期????????????????????????程序执行过程:框架原理

分析内容:指令的操作过程

分析对象:典型指令CLA 指令: 0 →AC指令性质非访内存指令二个 CPU 周期操作过程取指令阶段执行指令阶段ADD 指令: AC +( D ) → ACSTA 指令: AC → DNOP 指令:空操作????????????????? JMP指令:D→PC?

取指令阶段

PC →ARPC + 1 →PCAR →ABUSM →DRDR →IRIR ( OP )→指令译码器译码及指令识别CLR指令执行过程

操作控制器送信号给 ALUALU 响应控制信号,执行 AC 清零工作ADD指令

指令性质访内指令三个 CPU 周期操作过程取指令阶段执行指令阶段送操作数地址两操作数相加送操作数地址:IR(地址码字段)→AR

两操作数相加

AR →ABUSM→DRAC + DR→ACSTA指令

AC →D访内指令三个 CPU 周期取指令送操作数地址存数存数操作

AC →DRAR →ABUSDR →DBUSDBUS →MNOP指令

第一个 CPU 周期执行取指令码,操作过程与其它指令相同第二个 CPU 周期为执行指令,不执行任何动作JMP指令

取指令阶段操作相同执行指令阶段IR (地址码部分) → PC指令周期的描述

文字描述数据通路图描述示意图描述方框图语言描述一个方框代表一个 CPU 周期菱形框代表某种判别或测试“ ~ ” 代表公操作

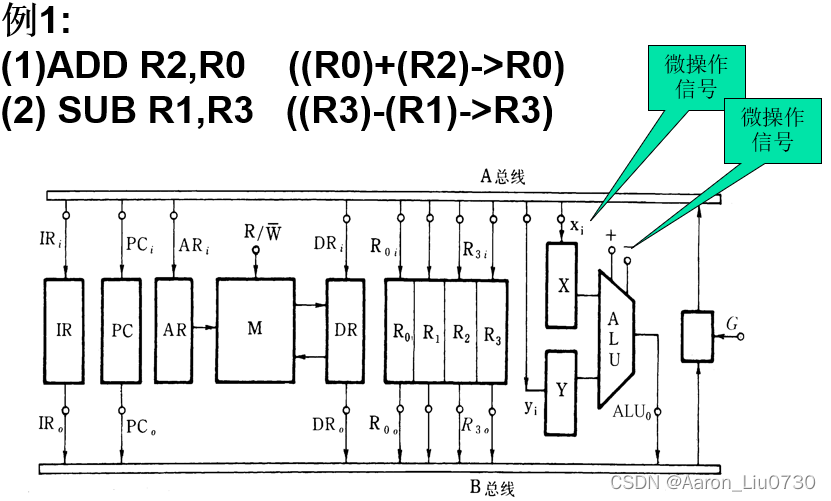

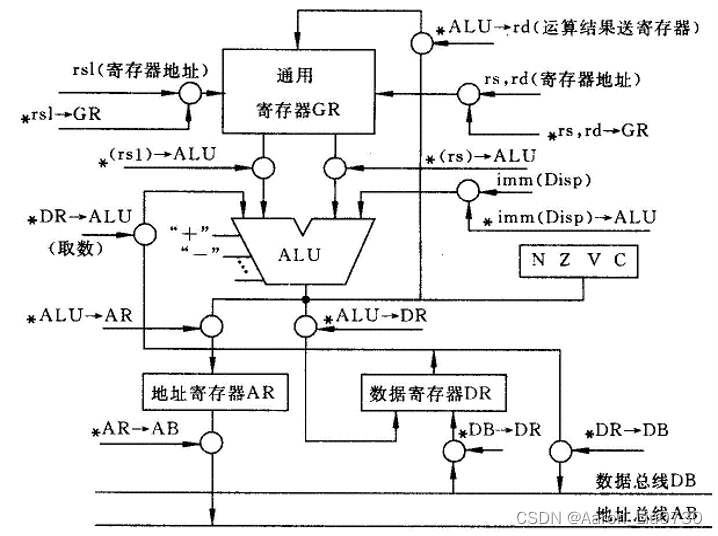

双总线结构机器的数据通路图

一条指令包括一个取指令周期和一个及一个以上的执行周期组成在每个 CPU 周期中数据通路是明确的数据通路的建立及操作受到操作控制器的控制,决定于是什么指令。

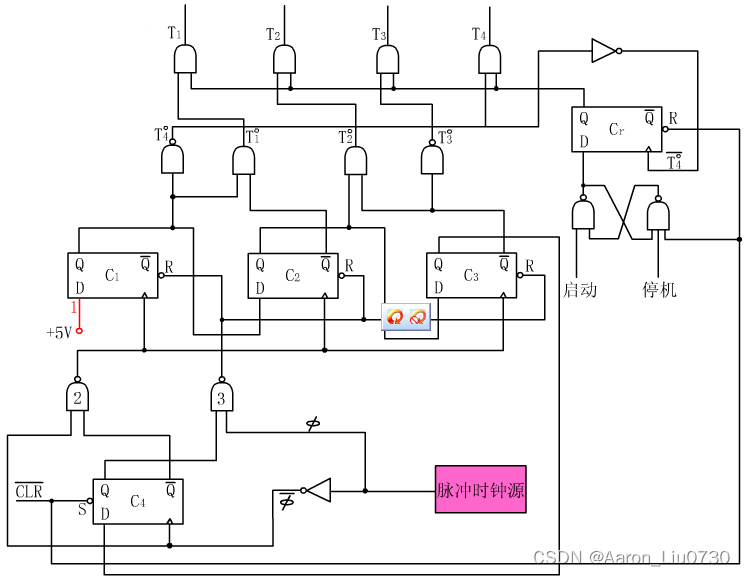

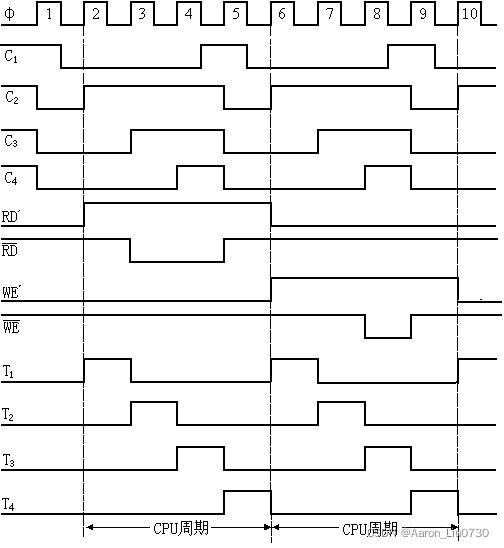

5.3 时许产生器

时序产生器计算机的协调动作需要时间标志,而时间标志则是用时序信号来体现的。硬布线控制器中,时序信号往往采用主状态周期 - 节拍电位 (CPU 周期 )- 节拍脉冲 ( 时钟周期 ) 三级体制。在微程序控制器中,时序信号比较简单,一般采用节拍电位 - 节拍脉冲二级体制。组成:

时钟源环形脉冲发生器节拍脉冲和读写时序译码逻辑启停控制逻辑

?环形脉冲发生器

环形脉冲发生器与时序信号译码

启停控制逻辑

? 启动、停机是随机的,对读 / 写时序信号也需要由启停逻辑加以控制。? 当运行触发器为“ 1” 时,打开时序电路。当计算机启动时,一定要从第 1 个节拍脉冲前沿开始工作。? 当运行触发器“ 0” 时,关闭时序产生器。停机时一定要在第 4 个节拍脉冲结束后关闭时序产生器。

控制方式

同步控制方式定义:不同指令在执行时所需的机器周期数和时钟周期数都是固定不变的。三种方案采用完全统一的机器周期执行各种不同的指令采用不定长的机器周期(将大多数操作安排在一个较短的机器周期内完成,对某些时间紧张的操作,则采取延长机器周期的办法来解决)中央控制与局部控制结合(将大多数指令安排在固定的机器周期完成(称为中央控制),对少数复杂指令采用另外的时序进行定时(称为局部控制))异步控制方式控制方式:每条指令的指令周期由不等长的机器周期数组成根据执行部件的信号决定指令周期的结束特点:每条指令、每个操作控制信号需要多少时间就占用多少时间操作控制序列没有固定的 CPU 周期数和时钟周期数与之同步联合控制方式同步方式与异步方式相结合的方式其一,大部分操作序列同步的(机器周期数固定),少量操作采用执行部件的应答其二,机器周期中的时钟周期数固定,各指令的机器周期数不固定(微程序控制)

5.4 微程序控制器

微程序控制计算机: 概念

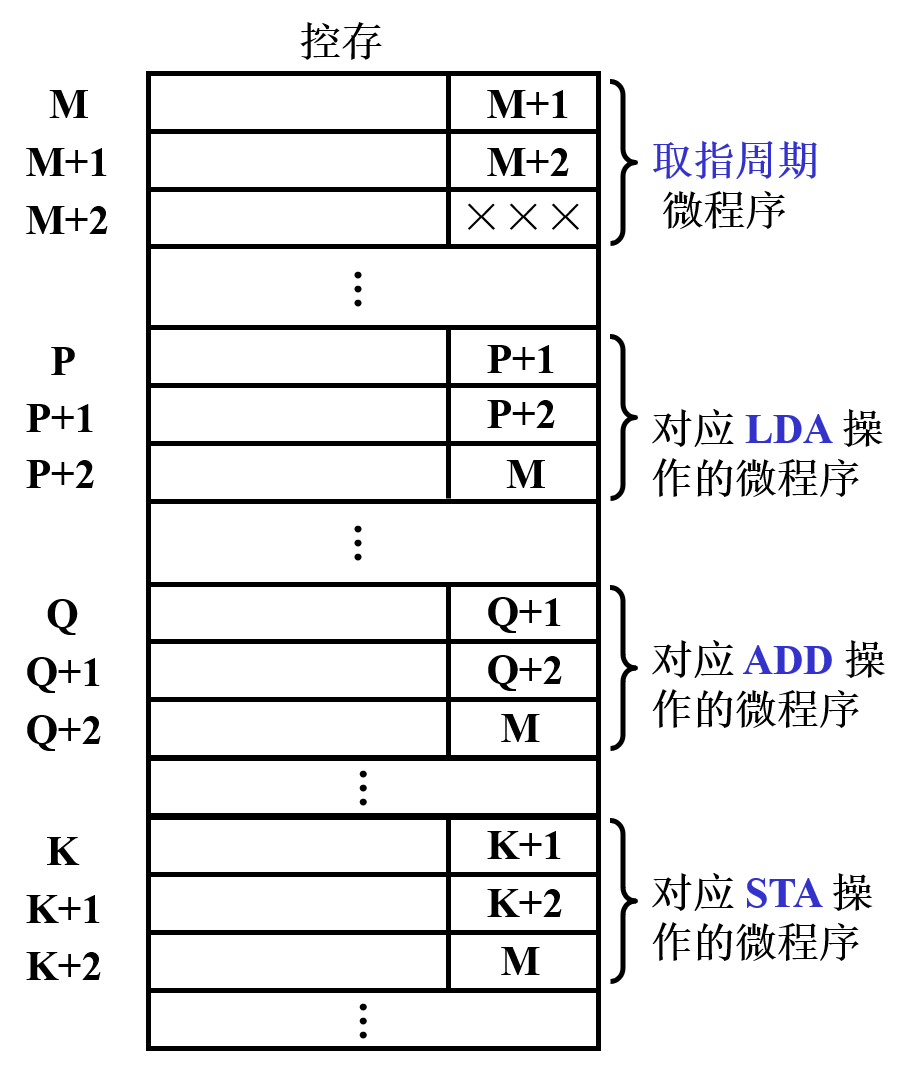

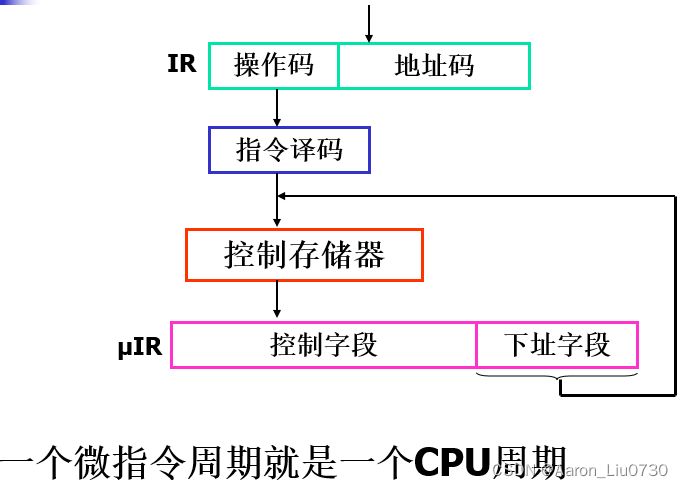

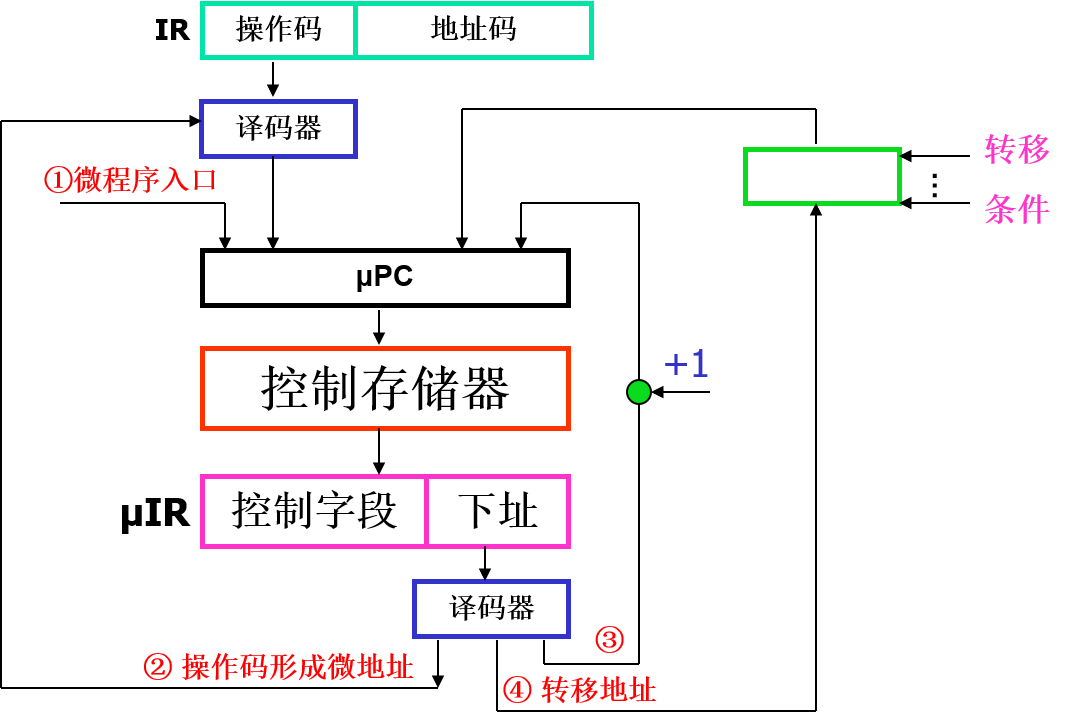

微命令由控制部件向执行部件发出的各种控制命令微操作执行部件在微命令的控制下完成的基本操作微指令一组实现一定功能的微命令的集合微程序完成一条机器指令功能的微指令序列的集合控制存储器存放微指令的存储器?

微程序控制信号的编号与意义

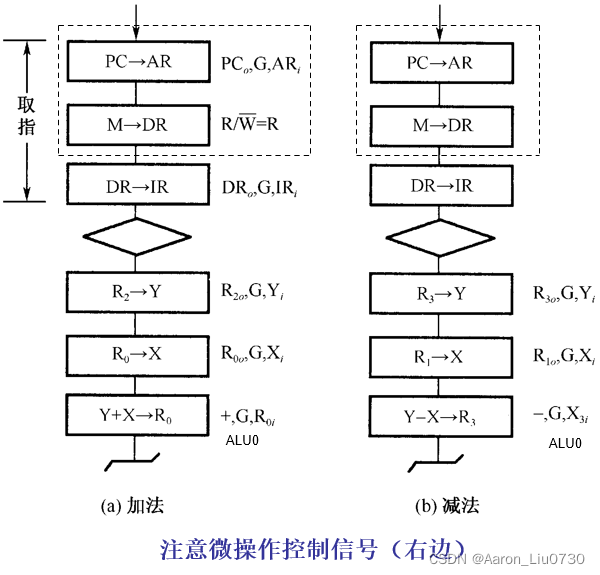

例: 加法指令所需的控制信号

(1) 取指

指令地址送AB: PC →AB(1)

从存储器取指令送DB:

ADS(21), M/IO#=1 (22), W/R#=0 (23)

指令送IR: DB →IR(5)

PC+1: PC+1(3)

(2) 计算操作数地址

取源操作数地址码:

Rs1→GR(8), (rs1)→ALU(10), disp→ALU(4)

加法运算: +(13)

有效地址送AR: ALU →AR(19)

(3) 取操作数

操作数地址送AB: AR →AB(20)

由存储器将操作数送DB:

ADS(21), M/IO#=1 (22), W/R#=0 (23)

操作数送DR: DB →DR(6)

(4) 执行加法运算并送结果

两个源操作数送ALU:

rs→GR (9), (rs)→ALU(11), DR→ALU(12)

加法运算: +(13)

送结果: ALU →GR(17)

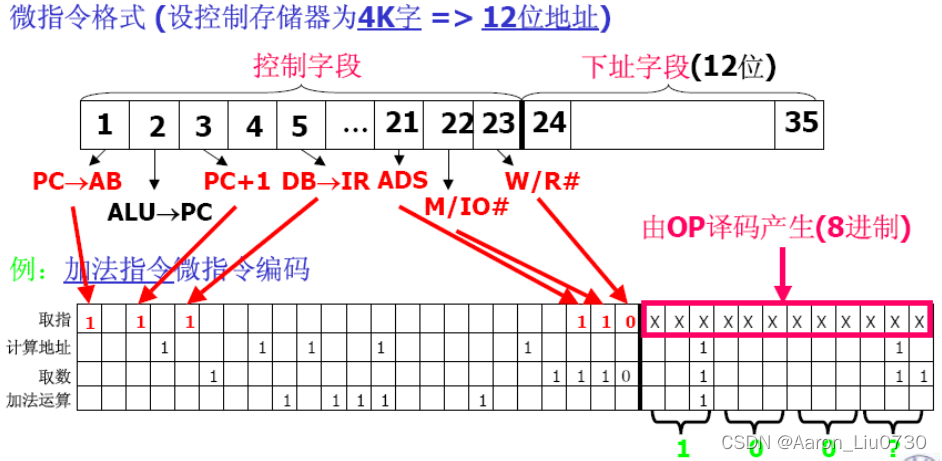

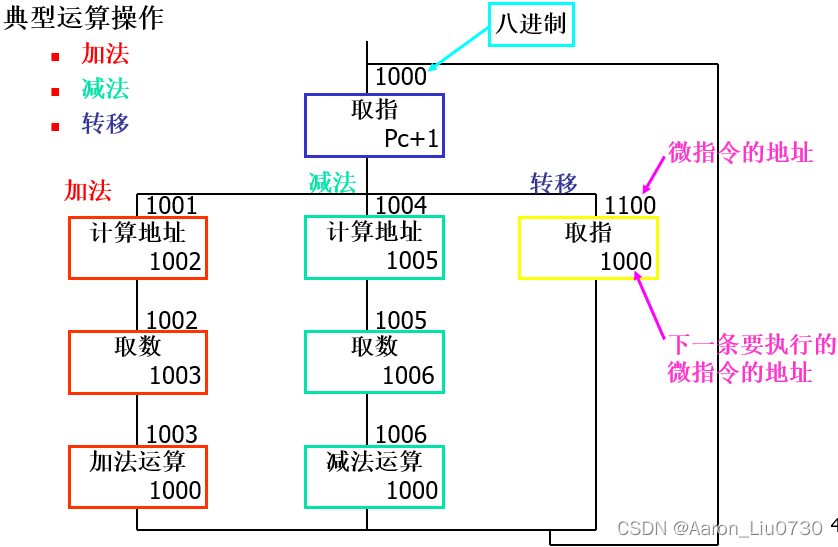

微程序指令的组织

?典型运算的微程序流程图

微程序控制器简图

微地址形成方法

计数器方式多路转移方式?

微程序设计的目标

微指令字的长度控制存储器的容量微程序的执行速度微程序设计的灵活性微指令编码

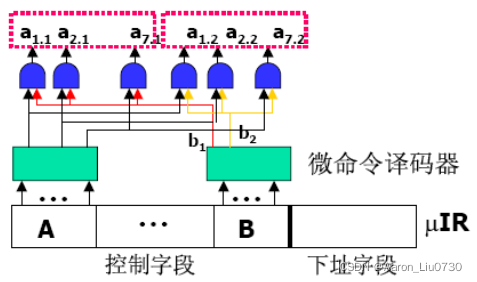

直接控制法控制字段中的每一位表示一个微命令缺点 :控制字段长 , 如三 , 四百位控制存储器容量要大 字段直接译码法把互斥的微命令编为一组对微命令进行编码 , 留出一个代码表示本段不发微命令增设微命令译码器字段间接编译法

字段直接译码法把互斥的微命令编为一组对微命令进行编码 , 留出一个代码表示本段不发微命令增设微命令译码器字段间接编译法一个字段的某些微命令由另一个字段的某些微命令来解释

如: 字段A受字段B的控制

常数字段

作为操作数送入ALU运算

作为计算机器初值来控制微程序的循环次数

?微指令格式

水平型微指令在一条微指令中定义 , 并执行多个并行操作微指令采用直接控制法 , 字段编译法 ( 直接或间接 )垂直型微指令微指令中设置微操作码字段,采用微操作码编译法,由微操作码规定微指令的功能特点一条微指令只要求能控制实现一 / 二种操作格式类似于指令 , 有微操作码字段

水平型微指令和垂直型微指令的比较?

水平型并行操作能力强 , 效率高 ; 垂直型则差一条垂直型微指令一般只能完成一个操作水平型微指令的执行时间短 , 而垂直型则长由水平型微指令解释的微程序短 , 而垂直型则长水平型微指令难掌握 , 而垂直型则较易掌握水平型微指令与机器指令的差别很大

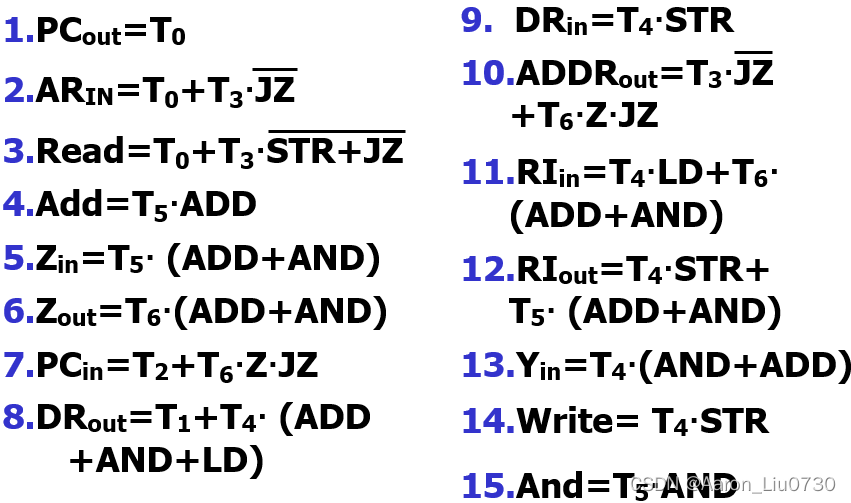

5.5 硬布线控制器

硬布线控制器的设计步骤

1.绘制指令流程图

2.列出微操作时间表

3.微操作的逻辑综合

?

??

微操作时间表

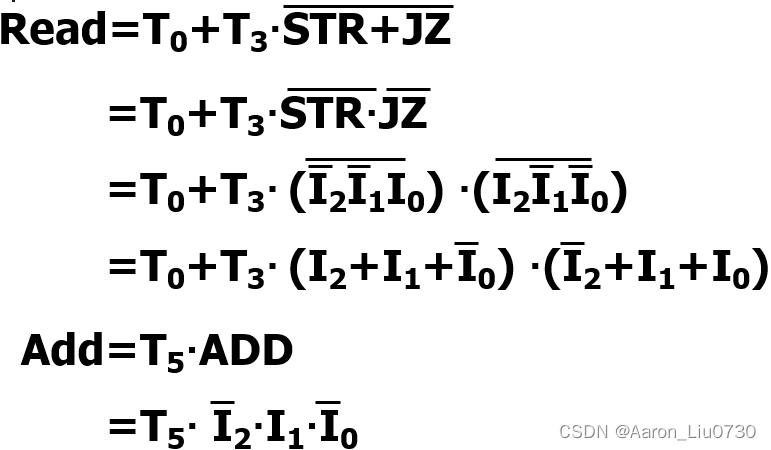

微操作的综合逻辑

对前两个步骤进行综合分析、归类,然后写出各微操作信号的逻辑表达式(由时序信号、指令译码信号及条件码、状态标志产生的)。

各种微操作的逻辑表达式

?

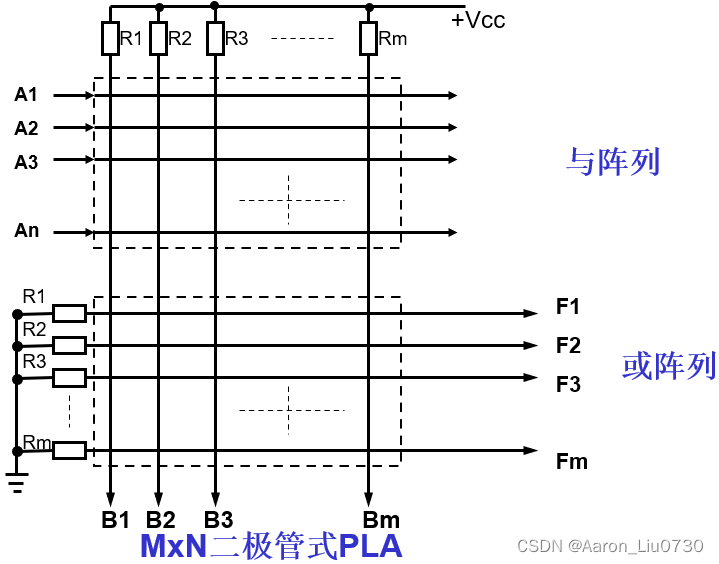

可编程逻辑阵列(PLA)控制逻辑?

硬布线控制器的构成

?

?

??

5.6 流水CPU

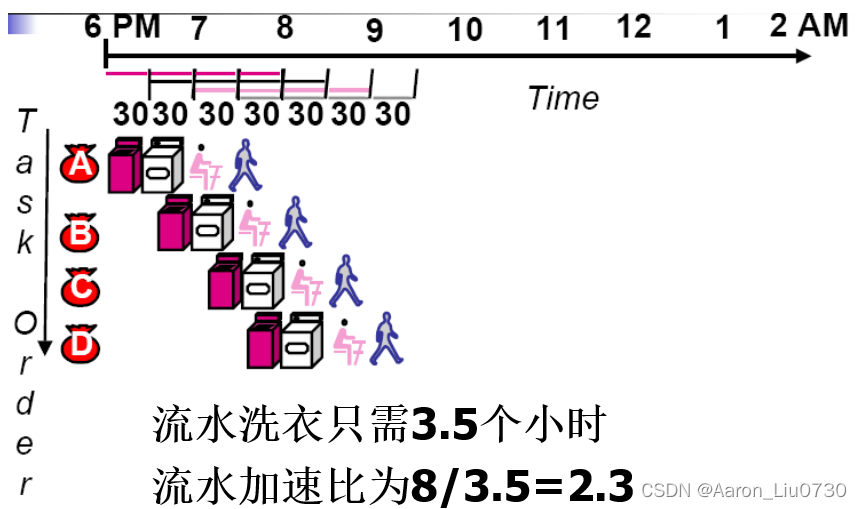

并行处理技术

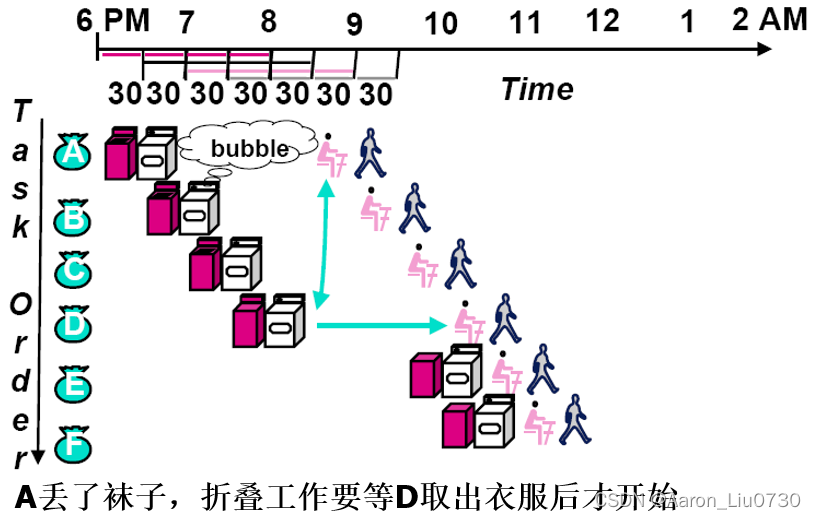

时间并行时间重叠改善操作流程:流水线技术空间并行资源重复增加冗余部件,如增加多操作部件处理机和超标量处理机

?

MIPS指令执行阶段?

1) IFetch: 取指令,PC+1

2) Decode Instruction:指令译码,读寄存器

3) Execute:

计算操作数地址运算4) Memory:

读 : 从内在读数据写 : 写数据到内存5) Write Back: 写数据到寄存器

?

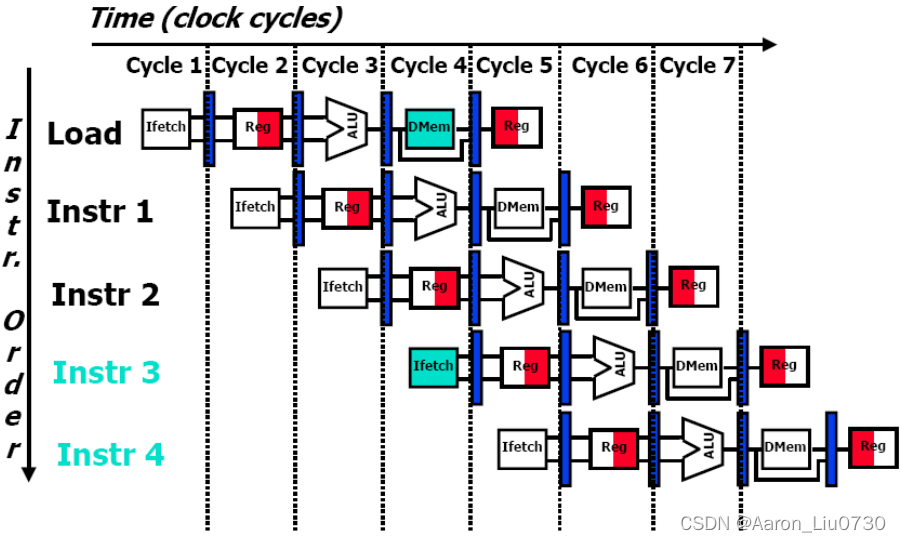

指令流水时空图

?

?

流水方式和非流水方式比较

假设内存存取需 2nsALU 运算需 2ns寄存器读写需 1ns非流水方式lw : IF + Read Reg+ ALU + Memory + Write Reg = 2 + 1 + 2 + 2 + 1 = 8nsadd : IF + Read Reg+ ALU + Write Reg = 2 + 1 + 2 + 1 = 6ns流水方式Max( IF,Read Reg,ALU,Memory,Write Reg) = 2 ns非流水时空图

?

超标量超流水

?

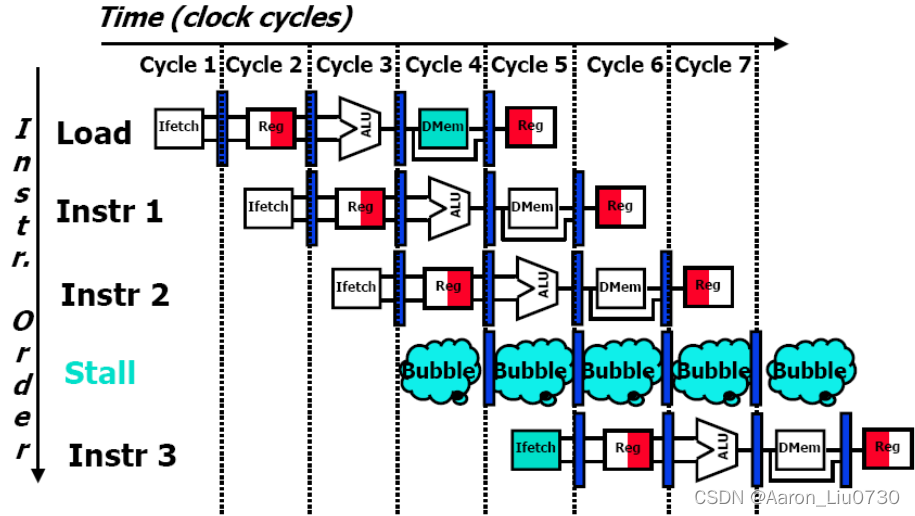

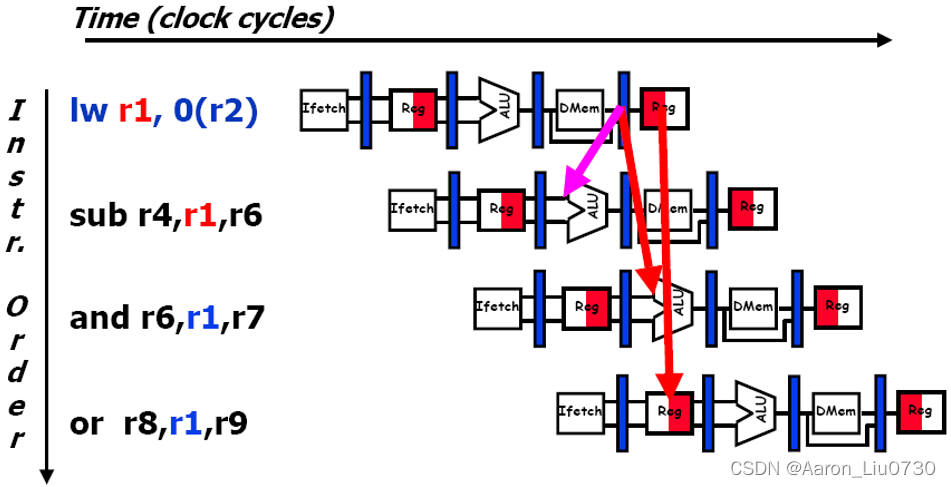

流水线中相关问题

指令相关问题影响流水的性能资源相关流水执行的多条指令同时使用同一个部件数据相关流水执行的多条指令访问相同的数据RAW 、 WAR 、 WAW控制相关转移指令引起的相关?单个存储器?

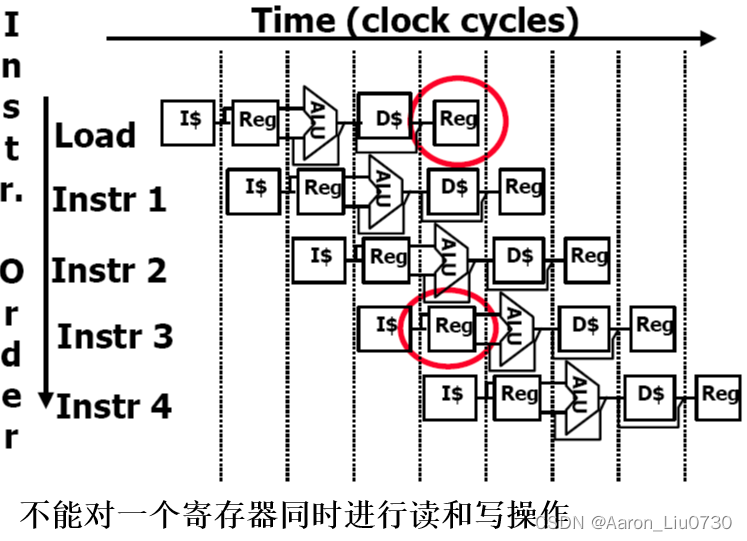

解决方法不能以增加内存的方式来解决增加 L1 cache ,且将数据 L1 cache 和指令 L1 cache 分开当两个 cache 都没命中时,需要更复杂的硬件控制?寄存器

事实上寄存器的读写时间非常快:比 ALU 阶段的一半时间还少解决方法:一种简单的方法通常寄存器的写操作在前半个时钟周期内通常寄存器的读操作在后半个时钟周期内结论:可以将寄存器读、写操作放在同一个时钟周期内?数据相关:寄存器

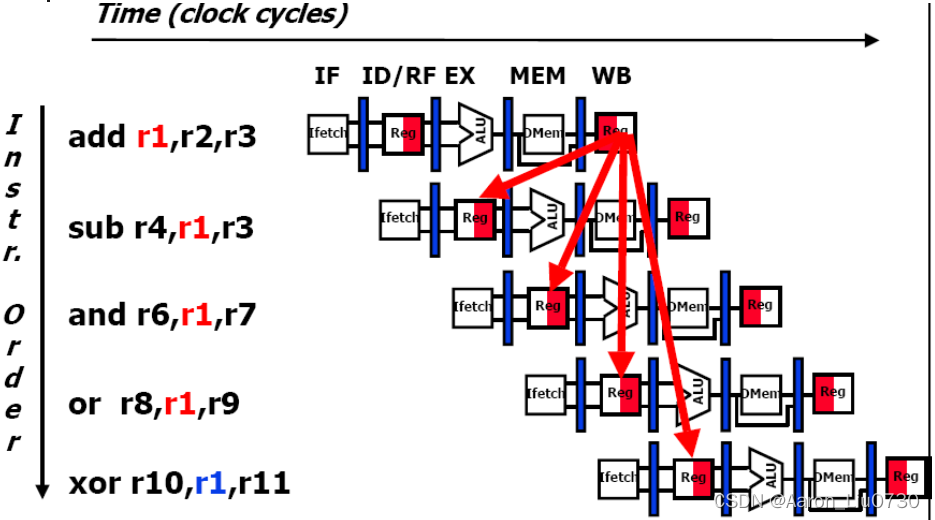

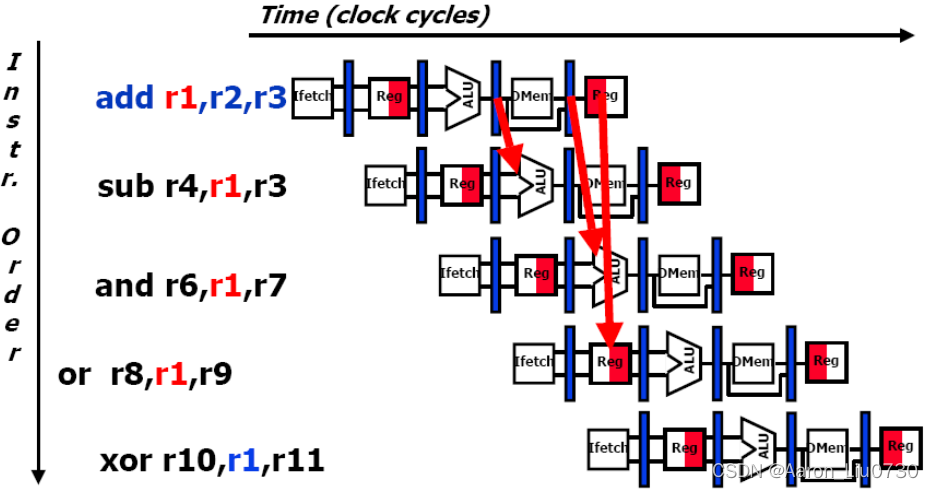

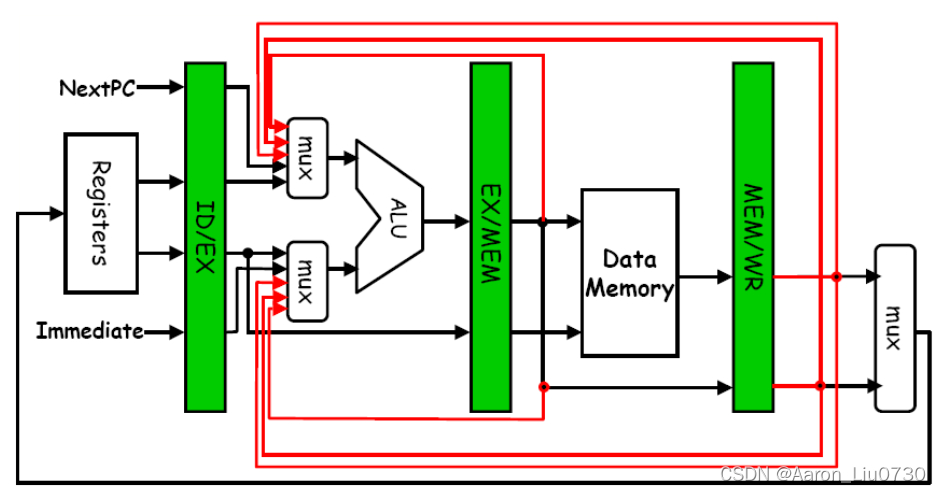

?向前传输避免数据相关

?硬件实现

有向前传输的数据相关

?

数据相关

【例】流水线中有三类数据相关冲突:先写后读相关( RAW);先读后写相关( WAR);写-写相关(WRW)。判断以下三组指令各存在哪种类型的数据相关。

(1) I1: ADD R1,R2,R3 ; (R2) + (R3)->R1

I2: SUB R4,R1,R5 ; (R1) - (R5)->R4

(2) I3: STA M(x),R3 ; (R3)->M(x),

?????????????????????????????????????????????? M(x)是存储器单元

I4: ADD R3,R4,R5 ; (R4)+(R5)->R3

(3) I5: MUL R3,R1,R2 ; (R1)×(R2)->R3

????? I6: ADD R3,R4,R5 ; (R4) + (R5)->R3

控制相关?

引起原因:转移指令解决办法:转移预测法硬件方法转移取( 53%MIPS )顺序取( 47% )延迟转移法编译优化: Branch-delay slots延迟槽

?

Pentium CPU

非固定长度指令格式, 9 种寻址方式, 191 条指令,兼具有 RISC 和 CISC 特性,不过我们还是将其看成 CISC提供了更加灵活的存储器寻址结构,可以支持传统的 4k 大小的页面,也可以支持 4M 大小的页面动态转移预测技术32 位微处理器(主要寄存器宽度为 32 位)Pentium 结构图

5.7 RICS CPU?

三个基本要素一个有限的简单的指令集CPU 配备大量的通用寄存器强调对指令流水的优化特点 :指令数量少。一般少于 100 种使用等长指令。目前典型长度为 4 个字节寻址方式简单。一般 2-3 种,不超过 4 种只有 LOAD/STORE 访问存储器。没有 SS 型指令大部分指令可以单周期执行控制器多采用硬布线方式采用延迟转移技术较多的寄存器RISC 强调编译优化实例 MC88110CPU 结构框图(见下图)12 个执行功能部件3 个 Cache (指令,数据和目标指令)两个寄存器堆(通用寄存器堆、扩展寄存器堆)六条 80 位宽的内部总线