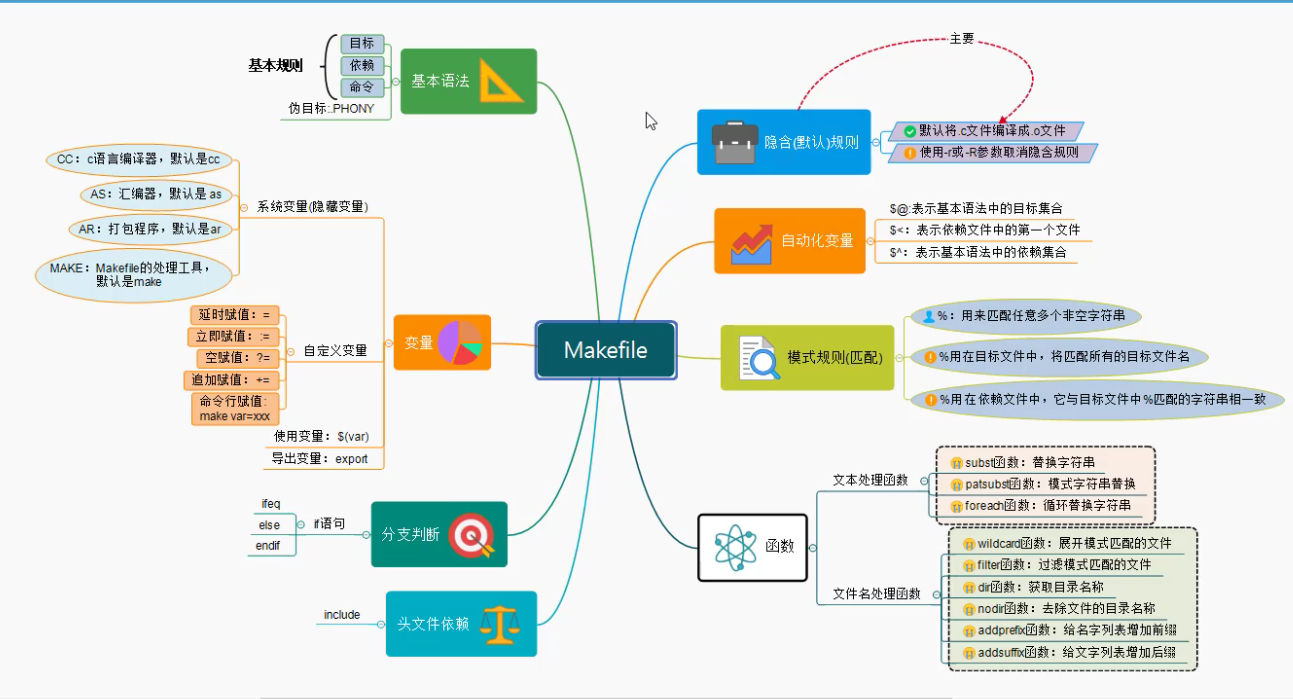

- 简介:本文主要讲解了在开发常规项目时,用于自动化部署生成目标文件的Makefile。对其包含的主要语法进行了讲解,最后给出了一个项目通用的Makefile模板,以帮助大家理解。

1. Makefile 三要素

- 目标

- 依赖

- 命令

目标:依赖(文件、其它目标)

<tab>命令1

<tab>命令2

<tab>命令3

target1:target2 target3

echo "target1"

target2:

echo "target2"

target3:

echo "target3"

输出:

$ vim Makefile

$ make

echo "target2"

target2

echo "target3"

target3

echo "target1"

target1

.PHONY:指定伪目标,即它指定的目标不是真正的目标,不管当前目录下有没有PHONY修饰的目标文件,每次make时均会执行PHONY修饰的目标文件下的命令行,一般用于修饰clean目标。

-

举个例子:

$ cat -n Makefile1 1 clean: 2 rm -f foo $ cat -n Makefile2 1 .PHONY: clean 2 clean: 3 rm -f fooMakefile1和Makefile2的差别就是在Makefile2中定义了:

1 .PHONY: clean-

直接Make看看

$ ls -l total 8 -rw-r--r-- 1 huanli huanli 18 Jul 13 17:51 Makefile1 -rw-r--r-- 1 huanli huanli 32 Jul 13 17:51 Makefile2 $ make -f Makefile1 clean rm -f foo $ make -f Makefile2 clean rm -f foo -

Makefile1和Makefile2的行为好像没有区别,但创建一个文件clean, 再make看看

$ touch clean $ ls -l total 8 -rw-r--r-- 1 huanli huanli 0 Jul 13 18:06 clean -rw-r--r-- 1 huanli huanli 18 Jul 13 17:51 Makefile1 -rw-r--r-- 1 huanli huanli 32 Jul 13 17:51 Makefile2 $ make -f Makefile1 clean make: 'clean' is up to date. $ make -f Makefile2 clean rm -f foo -

区别来了,Makefile1拒绝了执行clean, 因为文件clean存在。而Makefile2却不理会文件clean的存在,总是执行clean后面的规则。由此可见,.PHONY clean发挥了作用。

-

2. Makefile的变量、模式匹配

2.1 系统变量

- CC:编译器,如gcc

- AS:汇编器

- AR:打包程序

- MAKE:make

2.2 自定义变量

=:延迟赋值,当左值被引用(执行)的时候,才会根据右值的最新值对左值赋值。

:=:立即赋值,立即根据右值的当前值,对左值进行赋值。

?=:空赋值,只有当左值此时为空时,才会根据右值当前值对左值进行赋值。

+=:追加赋值,在左值的原值后面跟上(追加)右值的当前值。

make var=xxx:在命令行中执行make命令的时候,由用户对Makefile文件中的var变量进行赋值。

2.3 自动化变量

$<:代表最左边的依赖项

$@:代表目标

$^:代表所有的依赖项

2.4 模式匹配

%:匹配任意个非空字符串(类似shell中的*),且在makefile语句中,:前后的两个%代表的字符串是一样的。所以可以使用如下语句表示将当前目录下的所有c文件编译成.o的目标文件:

%.o : %.c

$(CC) -c $< -o $@

但在make的规则中,.o文件默认是由同名的.c文件编译来的,所以当需要某.o文件时,make会自动编译相应的.c文件。上面的语句即使不写,也是默认执行的!!!

3. Makefile的条件分支

-

ifeq/ifneq

ARCH ?= x86 ifeq ($(ARCH), x86) CC = gcc else CC = arm-linux-gnueabihf-gcc endif TARGET = my_target OBJS = main.o func.o $(TARGET) : $(OBJS) $(CC) $^ -o $@ .PHONY:clean clean: rm $(TARGET) %.o -

ifneq

ifneq (var1, var2) ... else ... endif

4. Makefile中的常用函数

4.1 patsubst――模式替换

$(patsubst Pattern, Replacement, Text)

功能:搜索Text中的单词,将符合Pattern模式的单词替换为Replacement。在Pattern模式中,可以使用通配符%代表任意个字符,但只有第一个%具有通配左右,后面出现的将作为普通的%。如果需要中间某%具有通配作用,则可以将其之前的所有%用反斜杠进行转义处理。

例如:$(patsubst %.c, %.o, x.c.c bar.c)执行后将会得到”x.c.o bar.o“。

当然,我们还有更简单的写法,同样是达到上述目的,我们先定义一个变量・sources = x.c.c bar.c,然后执行$(sources:.c=.o)或者是$(sources:%.c=%.o)

4.2 notdir

$(nodir 路径名):返回路径名最后一个反斜杠之后的文件名。

4.3 wildcard

$(wildcard Pattern):列出当前目录下所有符合Pattern模式的文件名。

注意:Pattern使用的是shell中的通配符,如?、*等

4.4 foreach

$(foreach Var,List, Text):它是一个循环语句,每一次取出字符串序列List中的一个单词赋值给Var,然后将Var代入到表达式Text中进行运算,得到的结果作为其中一个值。一个找出a、b、c、d4个目录下的所有文件赋值给files变量的如下:

dirs := a b c d

files := $(foreach dir, $(dirs),$(wildcard $(dir)/*))

4.5 suffix

$(suffix 文件名序列):返回文件名序列中各个文件名点号之后的后缀字符串

4.6 重写Makefile

环境:当前目录下有module1和module2两个文件夹,里面存放着若干c文件。

目的:在当前目录下,新建一个build文件夹,将生成的.o中间文件和目标文件mp3都放在里面。

Makefile文件:

#根据ARCH变量的值,选择合适的编译器

ARCH ?= x86

ifeq($(ARCH),x86)

CC=gcc

else

CC=arm-linux-gnueabihf-gcc

endif

#目标文件

TARGET=mp3

#生成文件夹

BUILD_DIR=build

#源文件文件夹列表

SRC_DIR=module1 module2

#所有源文件的路径名列表

SOURCES=$(foreach dir, $(SRC_DIR), $(wildcard $(dir)/*.c))

#所有依赖文件的路径名列表

OBJS=$(patsubst %.c, $(BUILD_DIR)/%.o, $(nodir $(SOURCES)))

#源文件搜寻目录

VPATH=$(SRC_DIR)

#编译目标

$(BUILD_DIR)/$(TARGET) : $(OBJS)

$(CC) $^ -o $@

#创建生成文件夹和中间文件

$(BUILD_DIR)/%.o : %.c | create_build

$(CC) -c $< -o $@

#伪目标(清除生成文件、创建生成文件夹)

.PHONY:clean create_build

clean:

rm -r $(BUILD_DIR)

create_build:

mkdir -p $(BUILD_DIR)

4.7 头文件依赖

-

写一个头文件,并将其添加到编译器的头文件路径中。

-

实时检查头文件更新情况,一旦变化应重新编译相关文件。

-

实例

-

环境:main.c位于./module1文件夹中,funcs.c位于./module2文件夹中。其中main.c会调用到funcs.c中定义的函数func1()和func2()。

-

目标:编译时,main.c能够正确调用funcs文件中的函数和全局变量。

-

解决方案:

- 当前目录下创建./include文件夹,并在里面新建头文件funcs.h

#ifndf __FUNCS_H #define __FUNCS_H void func1(void); void func1(void); #define var "I am a varible" #endif-

更新funcs.c文件,并在其头部添加头文件包含语句

#include "funcs.h" -

更新main.c文件,并在其头部添加头文件包含语句

#include "funcs.h" -

修改Makefile文件,添加头文件包含路径

#根据ARCH变量的值,选择合适的编译器 ARCH ?= x86 ifeq($(ARCH),x86) CC=gcc else CC=arm-linux-gnueabihf-gcc endif #目标文件 TARGET=mp3 #生成文件夹 BUILD_DIR=build #源文件文件夹列表 SRC_DIR=module1 module2 #头文件路径 INC_DIR=include #编译选项 CFLAGS=$(patsubst %, -I%, $(INC_DIR)) #头文件列表 INCLUDES=$(foreach dir, $(INC_DIR), $(wildcard $(dir)/*.h)) #所有源文件的路径名列表 SOURCES=$(foreach dir, $(SRC_DIR), $(wildcard $(dir)/*.c)) #所有依赖文件的路径名列表 OBJS=$(patsubst %.c, $(BUILD_DIR)/%.o, $(nodir $(SOURCES))) #源文件搜寻目录 VPATH=$(SRC_DIR) #编译目标 $(BUILD_DIR)/$(TARGET) : $(OBJS) $(CC) $^ -o $@ #创建生成文件夹和中间文件 #此处在命令行中添加$(INCLUDES),可以确保头文件一有变化,就会重新编译 $(BUILD_DIR)/%.o : %.c $(INCLUDES) | create_build $(CC) -c $< -o $(CFLAGS) $@ #伪目标(清除生成文件、创建生成文件夹) .PHONY:clean create_build clean: rm -r $(BUILD_DIR) create_build: mkdir -p $(BUILD_DIR)

-