? ? ? ? SHIFT RAM IP核,FPGA工程师们也通常称之为移位寄存器,它是一种特殊的RAM,并且在FPGA图像视频加速领域有着非常广泛的应用,甚至被人们称为专门为图像卷积运算而生的IP核。

? ? ? ?在这篇博客里笔者和大家一起去学习实践这个经典的IP核,pg122-c-shift-ram是IP核的官方说明手册,如果朋友们在使用过程中有一些不清楚的细枝末节,可以去及时查阅该手册,以扫清工作中存在的疑问。

? ? ? ?其实大家想想看,在对数字信号处理也好,图像视频加速也好,是不是经常会用到均值滤波、中值滤波等等相关的计算操作,这里核心的计算部分应该就是矩阵运算了,那么在FPGA设计中例如对3*3的矩阵进行运算的时候又有哪些方法呢,其实理论上应该有典型的三种方法可以实施落地:

1.通过2个或者3个RAM的存储来实现3*3像素窗口;

2.通过2个或者3个FIFO的存储来实现3*3像素窗口;

3.通过2行或者3行SHIFT RAM的存储来实现3*3像素窗口;

? ? ? ?在FPGA当中可以通过RAM和FIFO进行矩阵运算,但是明显这不是很好的方法,因为在设计当中需要考虑到很多方面,使得整体设计更加繁琐和复杂,其中很关键的一点,大家都知道卷积运算的时候需要对矩阵很多行进行缓存,比如3*3的卷积核则需要事先同时存入三行像素中每行的三个列数据,而用RAM和FIFO非常难做到这点,程序上几乎很难以实现,所以这时候就引入了移位寄存器这种特殊的RAM IP核。

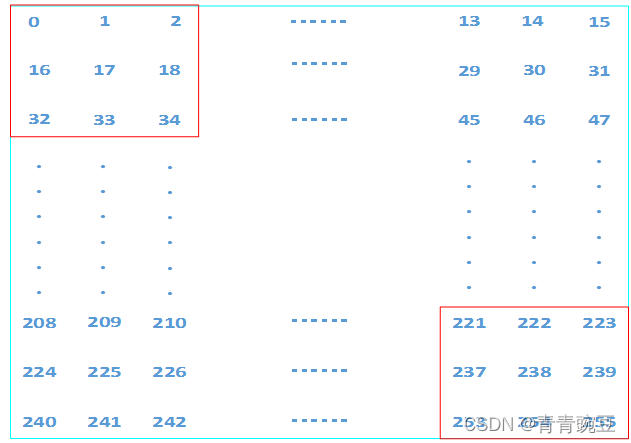

? ? ? 比如这里我们模拟3*3卷积核对16*16像素图片卷积遍历的设计,如图1所示,设计一个模块依次卷积遍历整个16*16的像素图片,然后输出到下游模块,下游模块再依次根据3*3卷积核中的数据实现各类滤波算法等等。

图1? 3*3卷积核对16*16像素图片卷积遍历的设计示意图

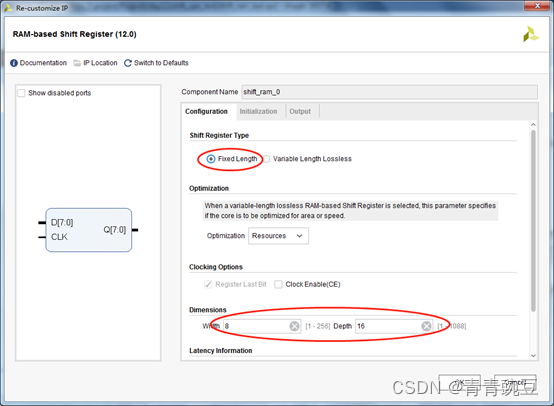

? ? ? 介绍完设计目的和应用场景后,再来说明移位寄存器SHIFT RAM IP核的具体用途和初始化流程,移位寄存器,顾名思义它和RAM IP核的功能非常类似,即缓存数据,但是不同的地方在于它可以实现数据延时的缓存输出。通俗地说,比如向该IP内写入数据位宽为8位的数据,然后可以通过配置IP核的方式,实现很多个周期后再输出缓存数据的目的。如下图2所示,在这个练习中我们配置Dimensions选项中的Depth为16,那么从接口D写入IP核中的数据,会在16个时钟周期后再通过Q依次输出,Altera厂家的EDA环境下移位寄存器IP核可以实现多行的缓存输出,但是Xilinx下的Vivado环境,仅仅支持缓存输出一行数据,不过其实也无关紧要,我们这里可以使用两个SHIFT RAM IP核和正在输入的一行数据三者共同组成3行数据。

图2 移位寄存器SHIFT RAM IP核的配置

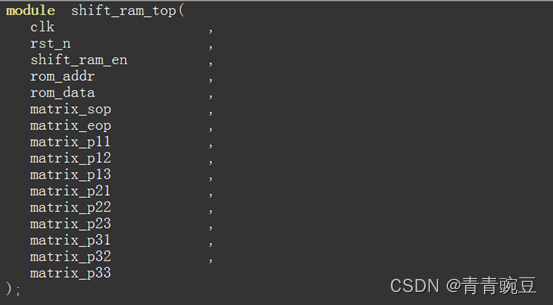

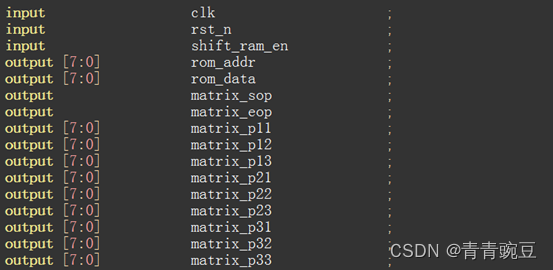

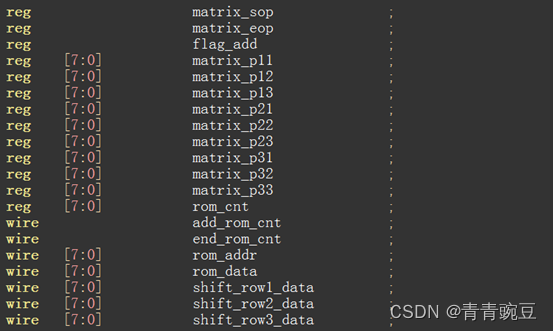

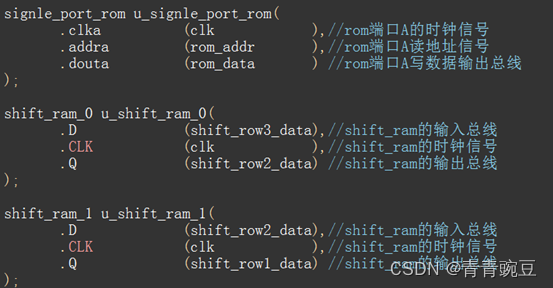

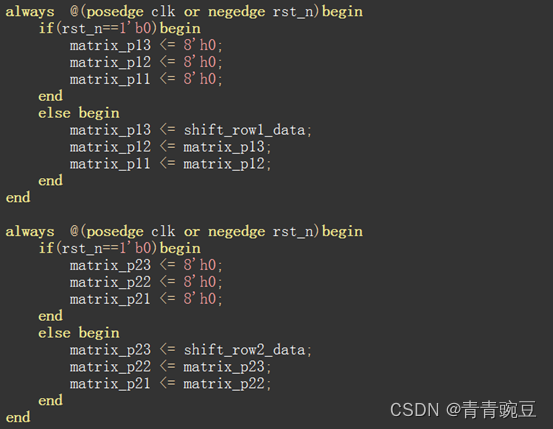

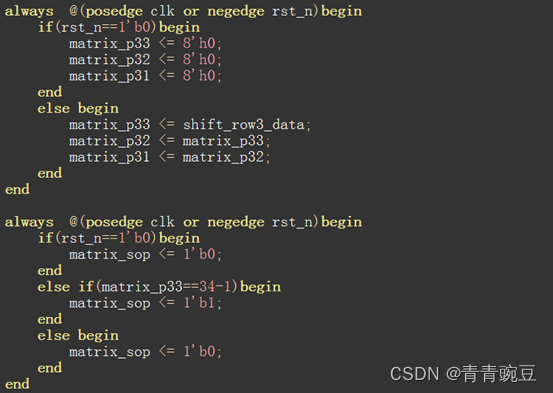

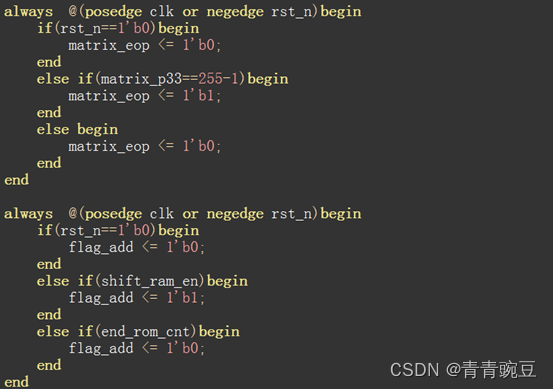

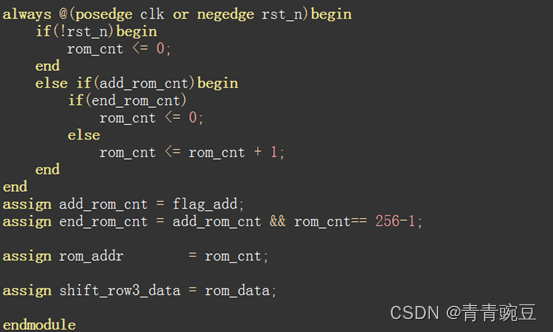

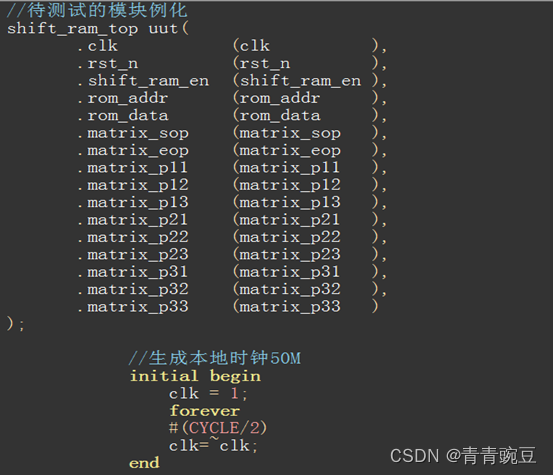

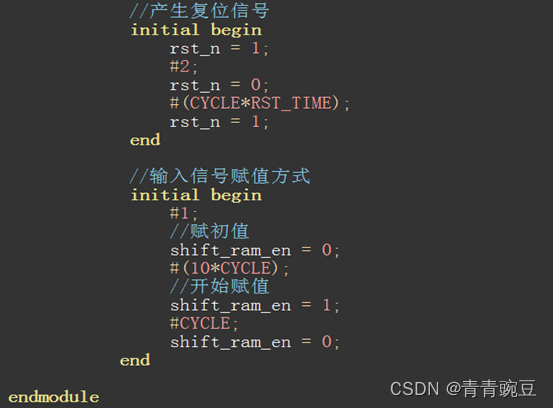

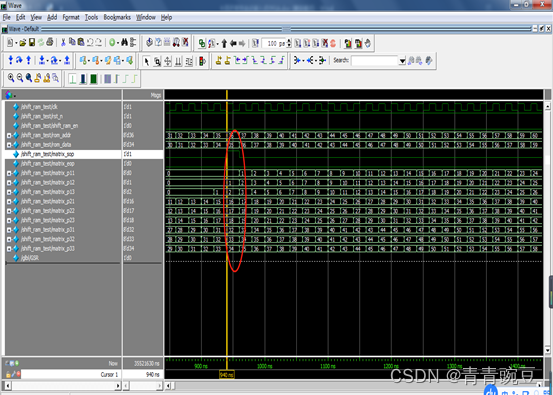

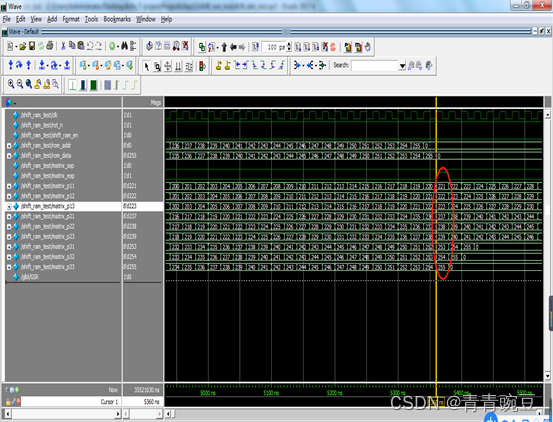

? ? ? 如表1所示,是移位寄存器SHIFT RAM IP练习设计中的信号列表,也引入了sop和eop两个关键的信号量,输出用以告诉下游的计算模块,图片的卷积核何时开始输出、何时停止输出,定义matrix_p11信号代表3*3卷积核的左上角第一个像素点,后面依次类推,matrix_p33代表右下角最后一个像素点,这里我们用前面单口ROM IP核练习中的ROM模拟16*16的像素图片作为输入。接着向第一个移位寄存器中先写入图片第一行的像素数据,这里因为前面IP核设置了延迟16个时钟周期输出,所以第一个移位寄存器输出的像素数据刚好为第二行像素数据,再把第一个移位寄存器的输出作为第二个移位寄存器的输入,又延时了16个时钟周期,所以第二个移位寄存器输出的像素数据刚好为第三行像素数据,将matrix_p13、matrix_p23、matrix_p33数据依次打拍用前面的卷积核的像素点赋值,即可完成对整张图片的卷积遍历,最后输出matrix_sop和matrix_eop两个信号,如上图12-30所示matrix_p33即右下角最后一个像素点为34的时刻去输出matrix_sop,为255的时刻去输出matrix_eop,如图3是本练习的代码设计,供大家参考。图4是其输入信号激励设计,也非常简单直接模拟给出shift_ram_en使能信号即可。

? ? ? ?这里可能有些绕脑,尤其当大家刚接触到这个IP核的时候,但是在代入Modelsim仿真后结合如图5仿真波形结果,就可以很直观地就能理解到移位寄存器的用处。

| 信号列表 | ||

| 信号名 | I/O | 位宽 |

| clk | I | 1 |

| rst_n | I | 1 |

| shift_ram_en | I | 1 |

| rom_addr | O | 8 |

| rom_data | O | 8 |

| matrix_sop | O | 1 |

| matrix_eop | O | 1 |

| matrix_p11 | O | 8 |

| matrix_p12 | O | 8 |

| matrix_p13 | O | 8 |

| matrix_p21 | O | 8 |

| matrix_p22 | O | 8 |

| matrix_p23 | O | 8 |

| matrix_p31 | O | 8 |

| matrix_p32 | O | 8 |

| matrix_p33 | O | 8 |

表1?移位寄存器SHIFT RAM IP练习设计中的信号列表

图3 移位寄存器SHIFT RAM IP核练习的代码设计

图4 移位寄存器SHIFT RAM IP核练习的输入信号激励设计

?

?

图5?移位寄存器SHIFT RAM IP核练习的仿真结果