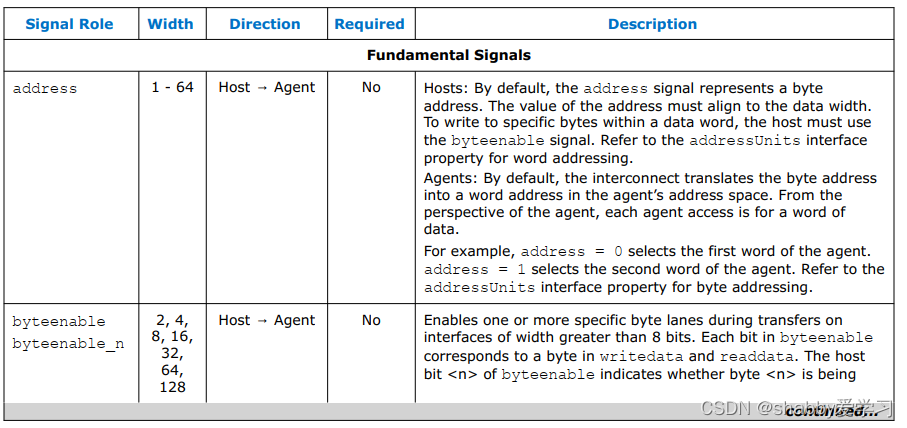

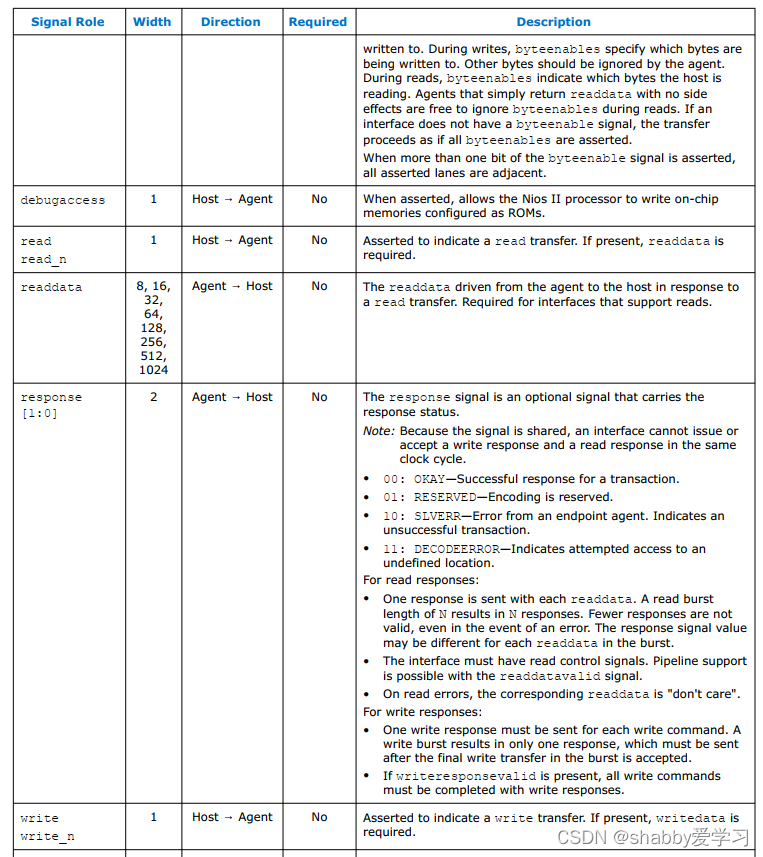

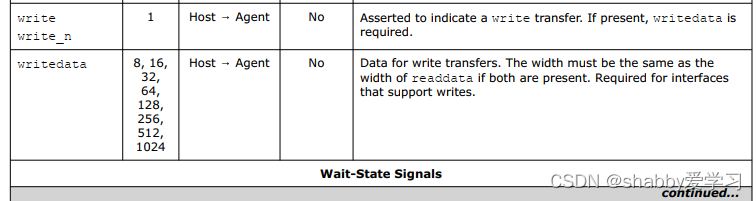

- Avalon是一个总线协议,设计的必须符合接口协议。具体协议上传到资源中,自行下载。

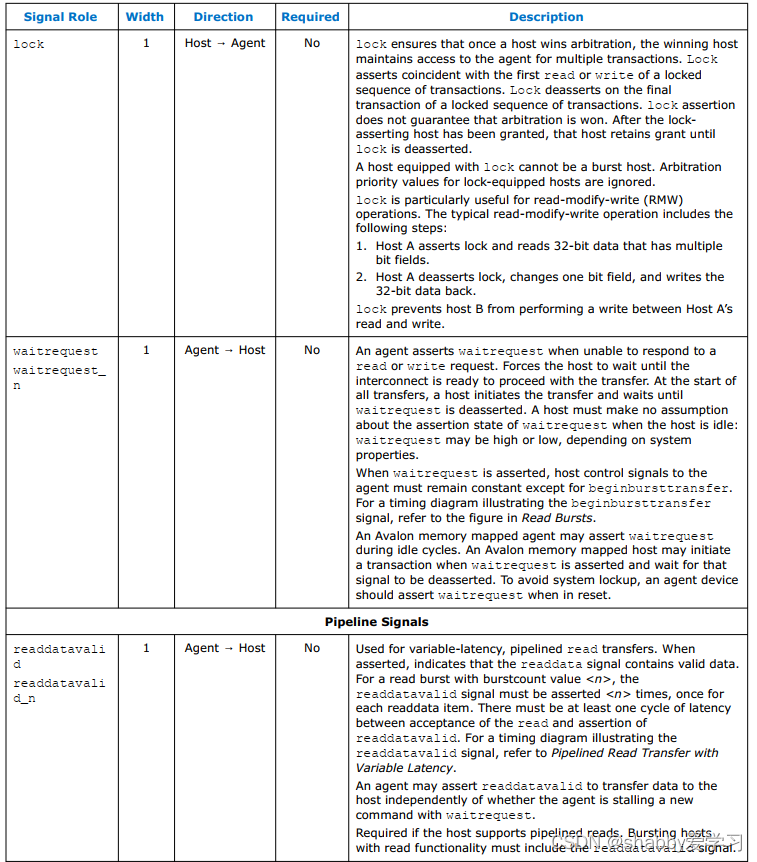

信号定义:

- 示例pwm设计ip并调用

//逻辑设计

module pwm_logic(

input clk ,

input rst_n ,

input en ,

input [31:0] counter_arr , //预重装载值

input [31:0] counter_ccr , //比较值

output reg pwm

);

//

reg [31:0] cnt;

wire add_cnt;

wire end_cnt;

reg [31:0] counter_ccr_r; //用于暂存用的

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 0;

end

else begin

cnt <= cnt + 1;

end

end

end

assign add_cnt = en; //打开使能 开始计数

assign end_cnt = add_cnt && cnt == counter_arr - 1; //计数到预重装载值得最大值就清零

//在一定周期内 修改传入的比较值的值

always @(posedge clk)begin

if(!cnt)begin

counter_ccr_r <= counter_ccr;

end

else begin

counter_ccr_r <= counter_ccr_r;

end

end

//pwm

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

pwm <= 1'b0;

end

else if(cnt >= counter_ccr_r)begin

pwm <= 1'b1;

end

else if(cnt < counter_ccr_r )begin

pwm <= 1'b0;

end

else begin

pwm <= pwm ;

end

end

endmodule

avalone接口协议

module pwm_avalon_port(

input clk ,

input rst_n ,

//avalon mm slave

input as_chipselect, //片选信号

input [1:0] as_address , //地址信号

input as_write , //写使能信号

input [31:0] as_writedata , //写数据

output reg [31:0] as_readdata , //读数据

//pwm

output wire pwm_dout

);

reg control; //控制寄存器 控制什么时候输出PMW波

reg [31:0] counter_arr; //预重装载值寄存器 确定频率

reg [31:0] counter_ccr; //比较寄存器 确定占空比

//counter_arr

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

counter_arr <= 32'b0;

end

else if(as_chipselect && as_write && (as_address == 0))begin

counter_arr <= as_writedata;

end

else begin

counter_arr <= counter_arr;

end

end

//counter_ccr

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

counter_ccr <= 32'b0;

end

else if(as_chipselect && as_write && (as_address == 1))begin

counter_ccr <= as_writedata;

end

else begin

counter_ccr <= counter_ccr;

end

end

//control

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

control <= 1'b0;

end

else if(as_chipselect && as_write && (as_address == 2))begin

control <= as_writedata[0];

end

else begin

control <= control;

end

end

//as_readdata

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

as_readdata <= 32'b0;

end

else if(as_chipselect)begin

case (as_address)

0: as_readdata <= counter_arr ;

1: as_readdata <= counter_ccr ;

2: as_readdata <= control ;

default: as_readdata <= 32'b0;

endcase

end

end

pwm_logic inst_pwm_logic(

.clk (clk ),

.rst_n (rst_n ),

.en (control ),

.counter_arr (counter_arr), //预重装载值

.counter_ccr (counter_ccr), //比较值

.pwm (pwm_dout )

);

endmodule

- 具体操作流程