ƽ̨:Modelsim10.5b,ǰ��Ϊ��װ��Quartus ��һ�汾

��Ȼ˵������ν��Modelsim��������,����Ҫ����Quatyus����Modelsim����,�������ϻ���ʹ�õ�Quartus�ķ���⡣

����֮ǰ�� Modelsim ��������,���������������и����˽ű��ļ���IP�˷����֧��,�������ݼ��·��ļ�:

#/*================================================*\

# Filename �s start.do

# Author �s Adolph

# Description �s Modelsim ����ű��ļ�

# Called by �s No file

#Revision History �s 2022-4-19

# Revision 1.0

# Email �s adolph1354238998@gmail.com

#\*================================================*/

#�˽ű��ļ�����ڹ����ļ����µ�tb���ļ���

#�� modelsim �� transcript ����ִ�е�ʱ��ʹ��

# do filename.do �����,�Զ�ִ�з���

#��������

transcript on

if ![file isdirectory verilog_libs] {

file mkdir verilog_libs

}

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

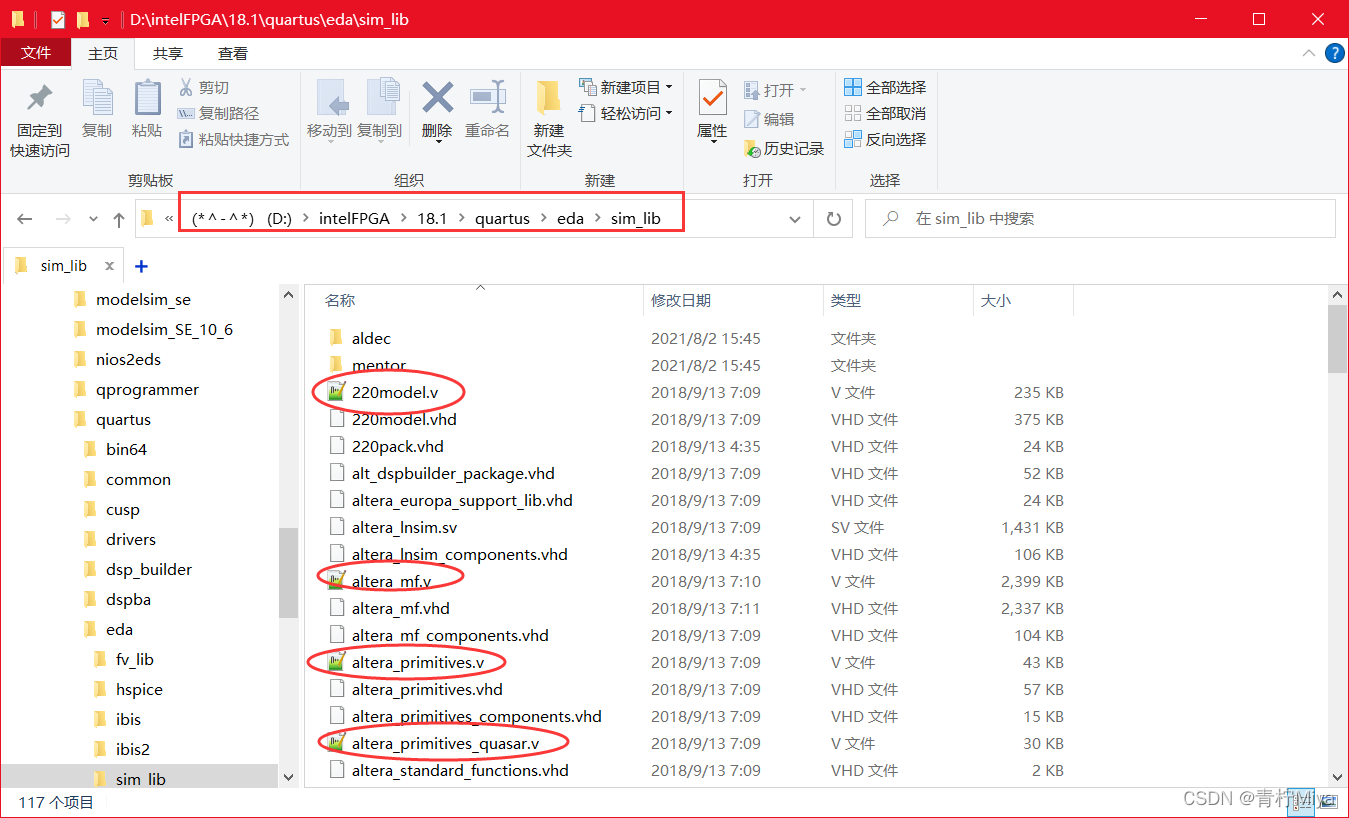

vlog -vlog01compat -work altera_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/altera_primitives.v}

# d:/intelfpga/18.1/quartus/eda/sim_lib/ ǰ����ַΪQuartus ���ذ�װ·��

vlib verilog_libs/lpm_ver

vmap lpm_ver ./verilog_libs/lpm_ver

vlog -vlog01compat -work lpm_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/220model.v}

vlib verilog_libs/sgate_ver

vmap sgate_ver ./verilog_libs/sgate_ver

vlog -vlog01compat -work sgate_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/sgate.v}

vlib verilog_libs/altera_mf_ver

vmap altera_mf_ver ./verilog_libs/altera_mf_ver

vlog -vlog01compat -work altera_mf_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/altera_mf.v}

vlib verilog_libs/altera_lnsim_ver

vmap altera_lnsim_ver ./verilog_libs/altera_lnsim_ver

vlog -sv -work altera_lnsim_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/altera_lnsim.sv}

vlib verilog_libs/cycloneive_ver

vmap cycloneive_ver ./verilog_libs/cycloneive_ver

vlog -vlog01compat -work cycloneive_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/cycloneive_atoms.v}

if {[file exists rtl_work]} {

vdel -lib rtl_work -all

}

vlib rtl_work

vmap work rtl_work

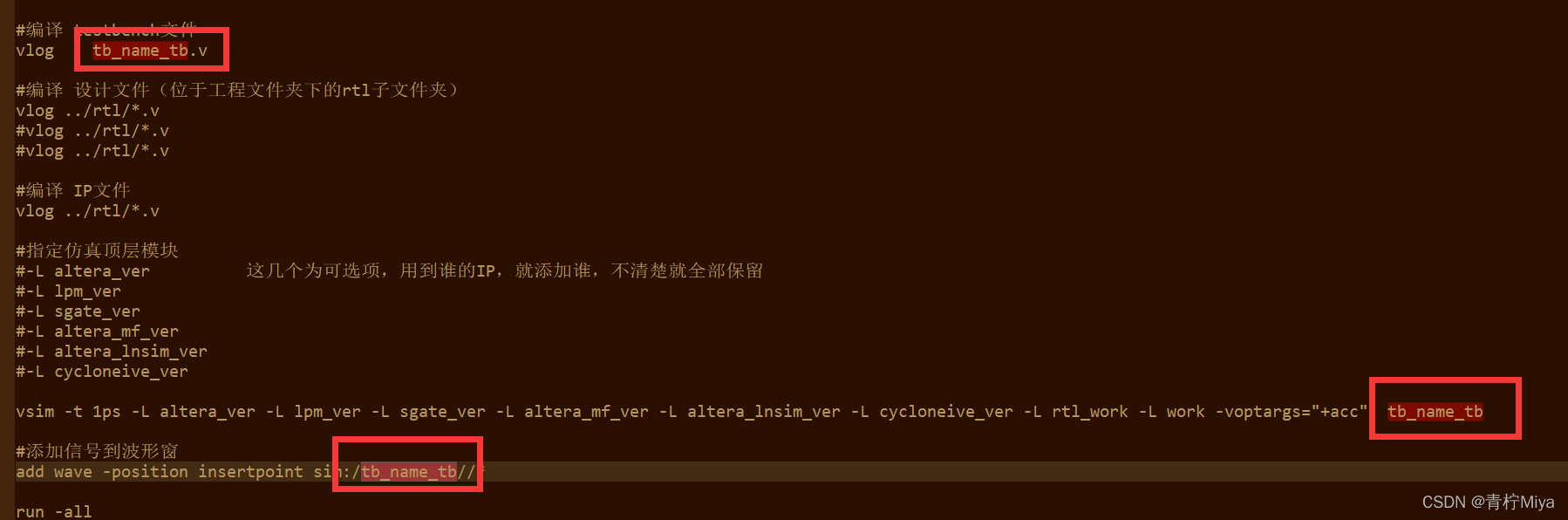

#���� testbench�ļ�

vlog **_tb.v

#���� ����ļ�(λ�ڹ����ļ����µ�rtl���ļ���)

vlog ../rtl/.v

#vlog ../rtl/.v

#vlog ../rtl/.v

#���� IP�ļ�

vlog ../rtl/.v

#ָ�����涥��ģ��

#-L altera_ver �⼸��Ϊ��ѡ��,�õ�˭��IP,������˭,�������ȫ������

#-L lpm_ver �⼸��Ϊ��ѡ��,�õ�˭��IP,������˭,�������ȫ������

#-L sgate_ver �⼸��Ϊ��ѡ��,�õ�˭��IP,������˭,�������ȫ������

#-L altera_mf_ver �⼸��Ϊ��ѡ��,�õ�˭��IP,������˭,�������ȫ������

#-L altera_lnsim_ver �⼸��Ϊ��ѡ��,�õ�˭��IP,������˭,�������ȫ������

#-L cycloneive_ver �⼸��Ϊ��ѡ��,�õ�˭��IP,������˭,�������ȫ������

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -voptargs="+acc" tb_name_tb

#�����źŵ����δ�

add wave -position insertpoint sim:/tb_name_tb//*

run -all

������������:

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

vlog -vlog01compat -work altera_ver {d:/intelfpga/18.1/quartus/eda/sim_lib/altera_primitives.v}

���е�tb_name_tbΪ�����ļ�����

����������ʹ�õ�·��Ϊ����PC��Quartus��װ�����·��,���ڰ�����Ӧ�ķ�����ļ�:����

����Verilog HDL��VHDL�ķ�����ļ�,���ڱ������ÿ�������ΪVerilog,�ʽű��ļ��������õ��ļ�Ϊ.v���͵ġ�

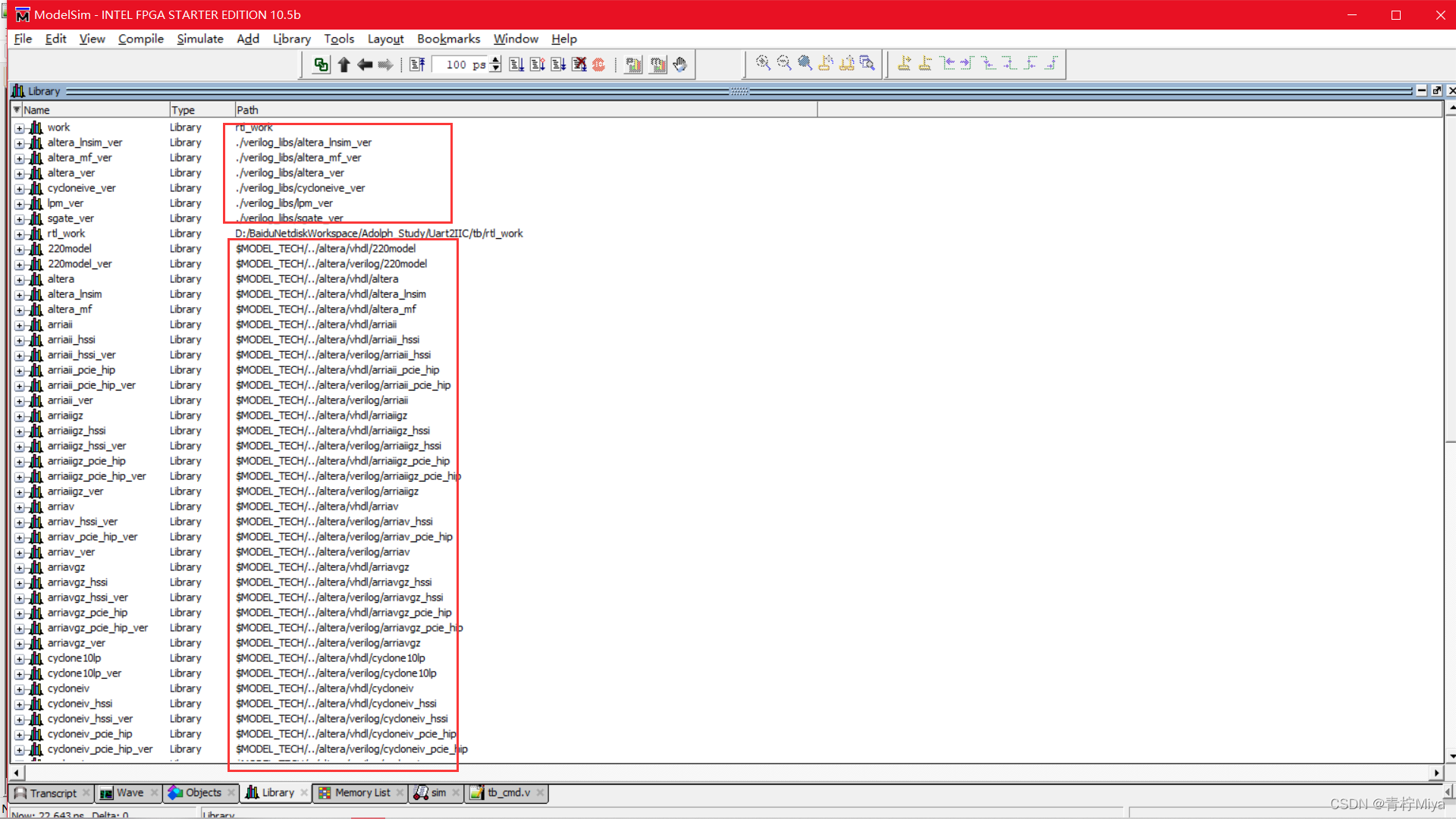

��������֮��,���Լ�����Ӧ�ķ���ⶼ�����ӵ���Modelsim��Library��:

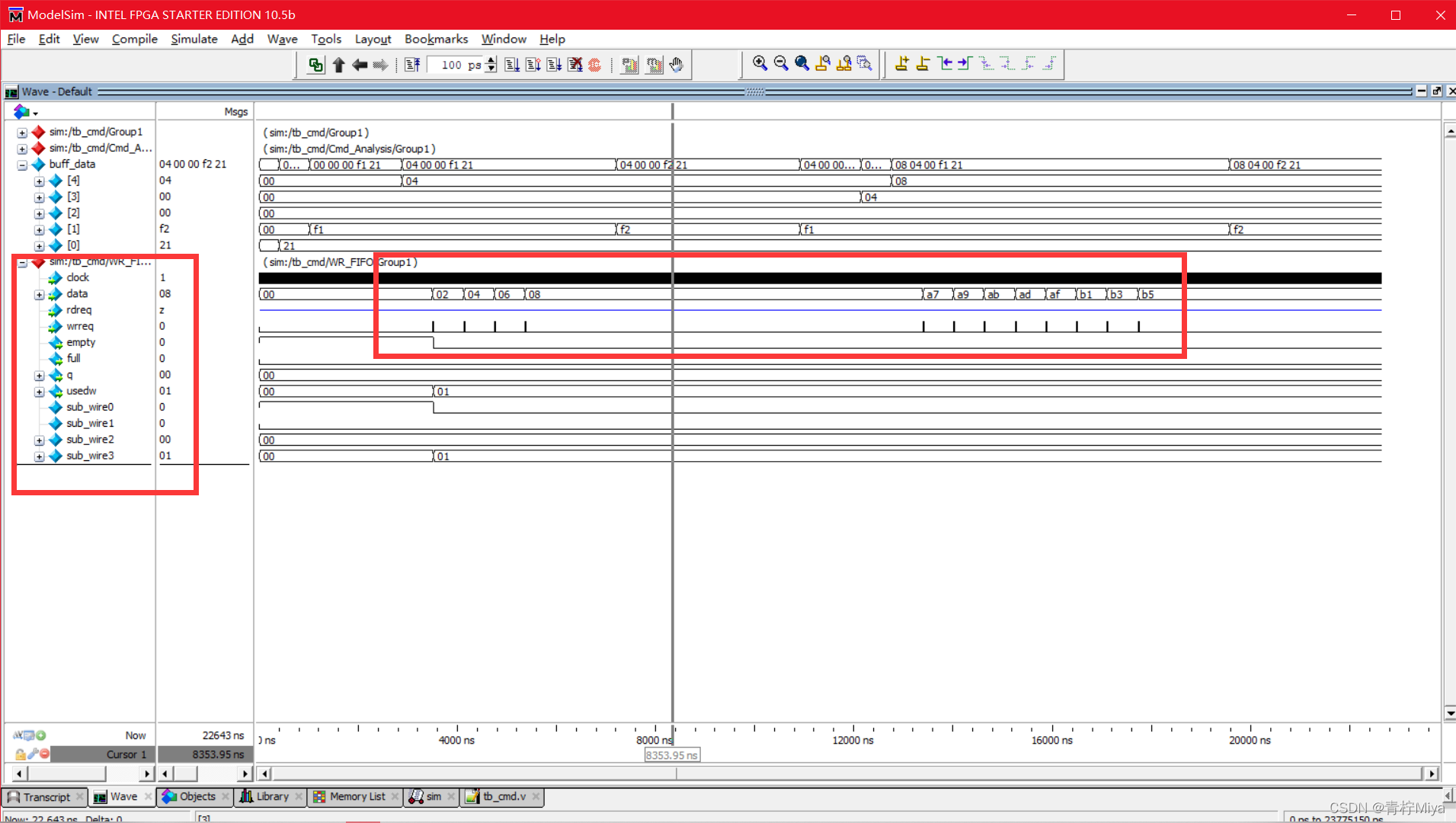

�������FIFO������Ҳ�ɹ�����������:

����Ȥ��ͯЬ������һ��