补发以下以前学习PCIe总结的知识。

PCIe学习笔记系列:

- PCIe基础知识及Xilinx相关IP核介绍

概念了解:简单学习PCIe的数据链路与拓扑结构,另外看看有什么相关的IP核。 - 【PG054】7 Series Integrated Block for PCI Express IP核的学习

基础学习:关于Pcie IP核的数据手册,学习PCIe相关的IP核的配置参数及其对应的含义。 - Xilinx PCIe IP核示例工程代码分析与仿真

基础学习:关于PCIe IP核的仿真,学习PCIe的配置流程以及应用过程。 - Xilinx XDMA 例程代码分析与仿真结果

应用学习:关于Xilinx PCIe DMA IP核的仿真,学习 PCIe DMA 的配置过程以及具体的数据传输流程。 - XDMA linux平台调试过程记录

应用学习:关于XDMA的实际调试过程,可在此基础上定制自己的需求。

1 关于PCIe DMA IP核

1.1 PCIe 基础

PCI Express总线是为了取代PCI总线的第三代I/O技术,但是对于系统软件,PCIe是向前兼容PCI总线的,理解PCIe总线必须建立在深刻理解PCI总线的基础志上,这里由于我也是初学者,不深入展开。

为了完成XDMA的测试,有一些基本的概念就可以,如果需要后面的开发应用,就需要系统的学习一下。

- 点到点的数据传输

- PCIe总线的物理链路的一个数据通路(lane)中,有两组差分信号。

- PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路中没有时钟,在接收端使用时钟恢复模块(clock data recovery,CDR)提取接收时钟。

- PCIe链路可以由多条lane组成,即PCIe x2 x4 x8分别代表有2,4,8条lane。

- PCIe总线使用的信号

- 这里主要是注意PCIe设备与PCIe插槽都具有REFCLK+/-信号,PCIe插槽使用这组信号与处理器系统同步。

- PCIe插槽向下兼容,比如PCIex2,x4都可以插x8的插槽。

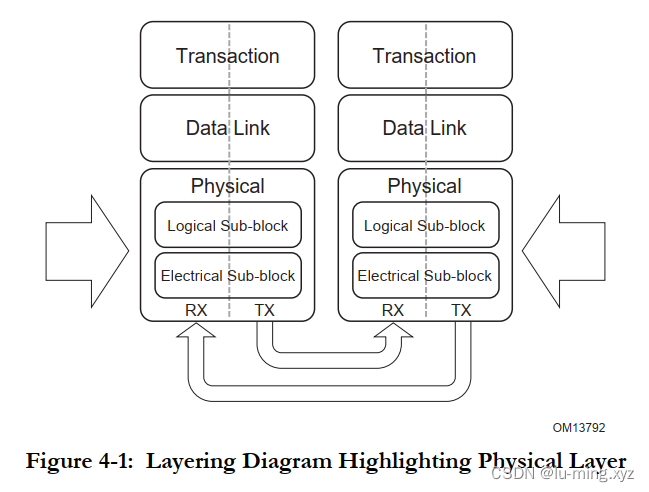

- PCIe总线的层次结构

上面的层次组成结构图展示了PCIe总线的层次组成结构。

数据报文首先经过事务层(Transaction layer),数据链路层(data link layer),和物理层(physical layer),最终发送出去。接收则相反,这里面每一层都会对数据进行处理。我们只是调通DMA的话暂时不用关注这个,但是如果要应用则必须深入学习。

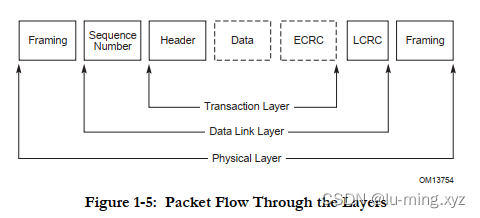

各层的包结构:

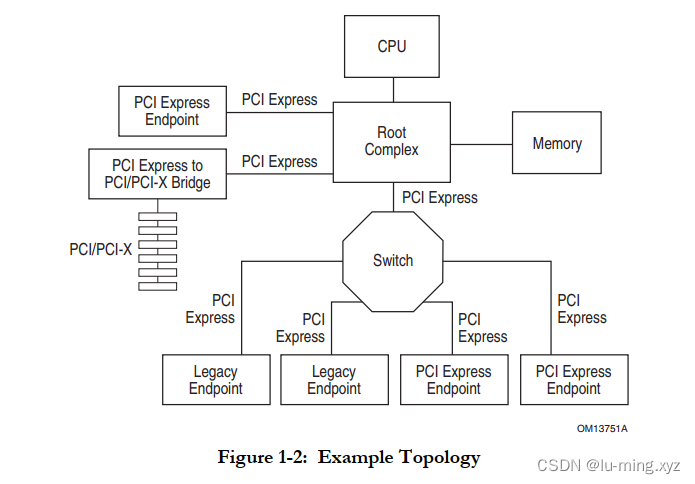

- PCIe的拓扑结构

- Root Complex:RC,将PCIe总线端口,存储器控制器等一系列与外部设备有关的接口都集成在一起,统称为RC。

- Endpoint:EP,基于PCIe总线的设备。

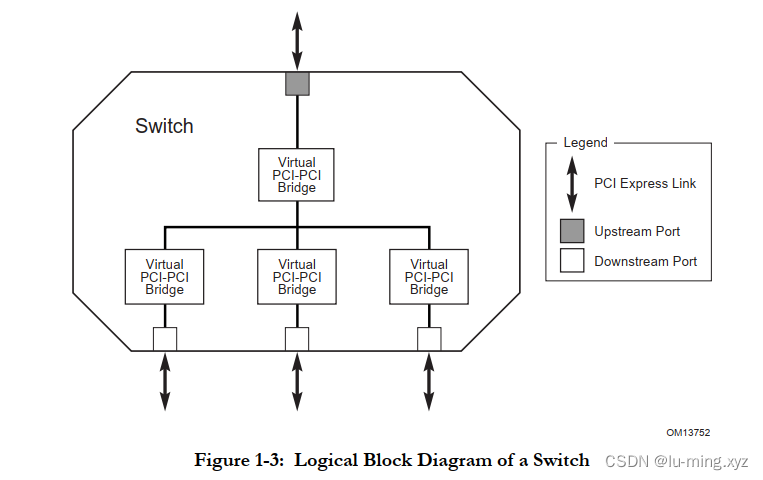

- Switch: 一个特殊的设备,多个虚拟PCI-to-PCI桥接设备的逻辑组件,该设备由1个上游端口和2~n个下游端口组成。

现在知道我们的板卡需要作为拓扑网络中的一个Endpoint与CPU进行通信。

1.2 PCIe相关IP核

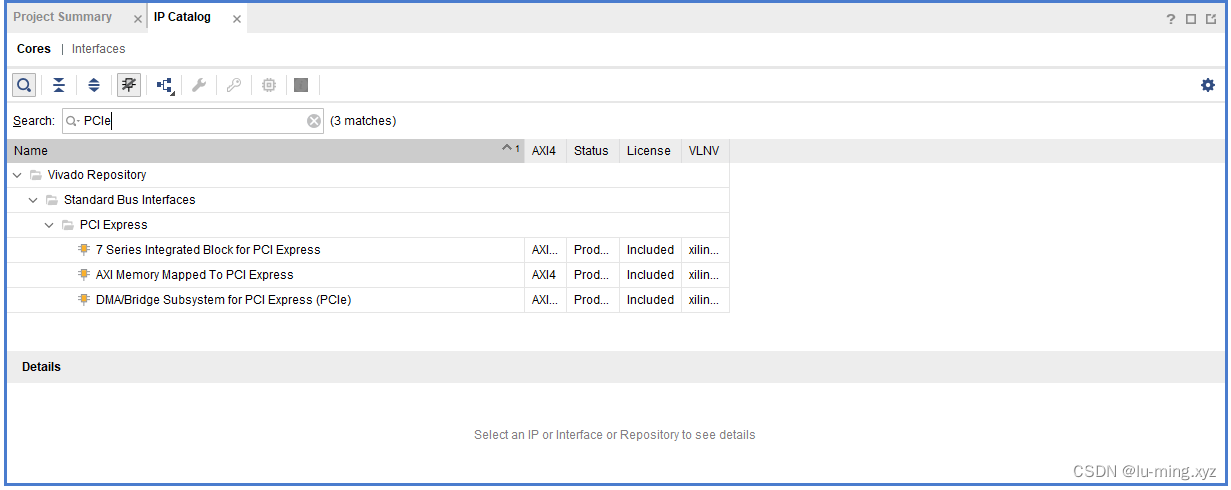

在Vivado IDE 中的 IP Catalog 中搜索 PCIe,有三个结果:

这三个Ip核对应的产品手册分别为:

- PG054:7 Series FPGAs Integrated Block for PCI Express v3.3

- PG055:AXI Memory Mapped to PCI Express (PCIe) Gen2 v2.9

- PG195:DMA/Bridge Subsystem for PCI Express v4.1

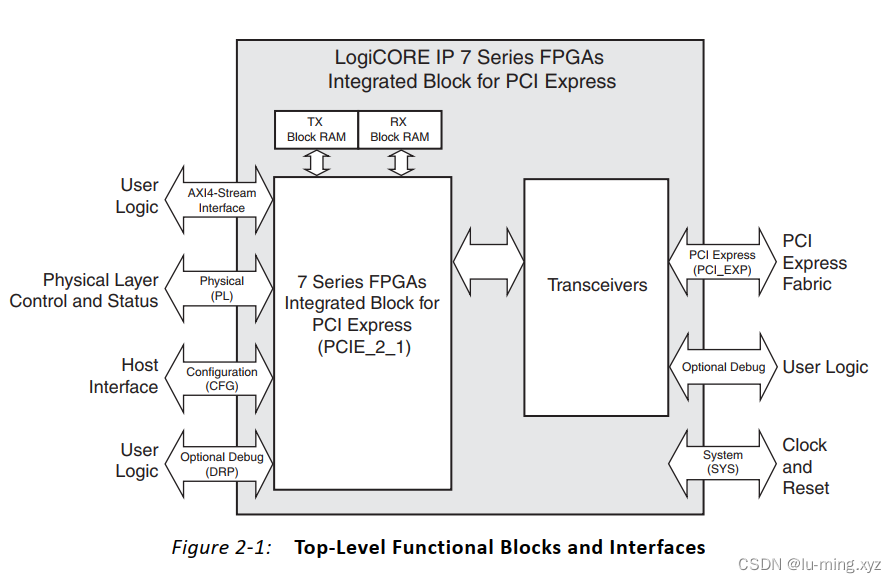

- 7 Series FPGAs Integrated Block for PCI Express

7 Series FPGAs Integrated Block for PCI Express 是一个可靠的、高带宽的、可扩展的串行互连构建块。这个IP 核简化了设计过程,缩短了上市时间。它是可配置的Endpoint和Root Port应用。

这个IP核是实现最底层的PCIe数据收发的模块。

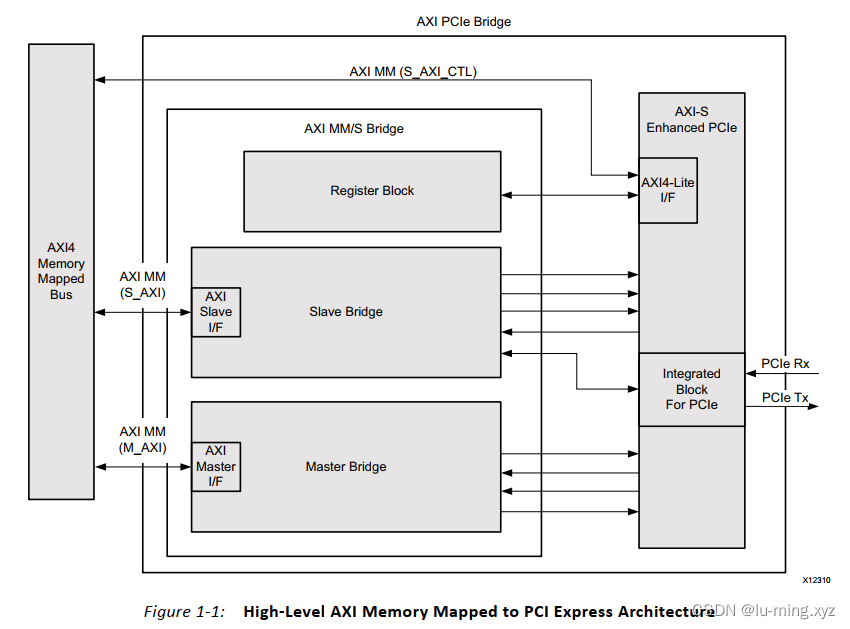

- AXI Memory Mapped to PCI Express (PCIe) Gen2

AXI Memory Mapped to PCI Express IP核 提供了一个【AXI4用户自定义接口】和【Integrated Block for PCI Express】之间的接口。IP 核提供了AXI4内嵌系统到PCI Express 系统之间的转换。将AXI4 内存读写转换成PCIe 的事务层数据包( Transaction Layer Packets ,TLP ),以及将PCIe内存读写的TLP包转换成AXI4接口控制。

结构:

可以看出,这个IP核实在底层核的基础上加上一些转换的桥模块,实现AXI4的内存映射功能。

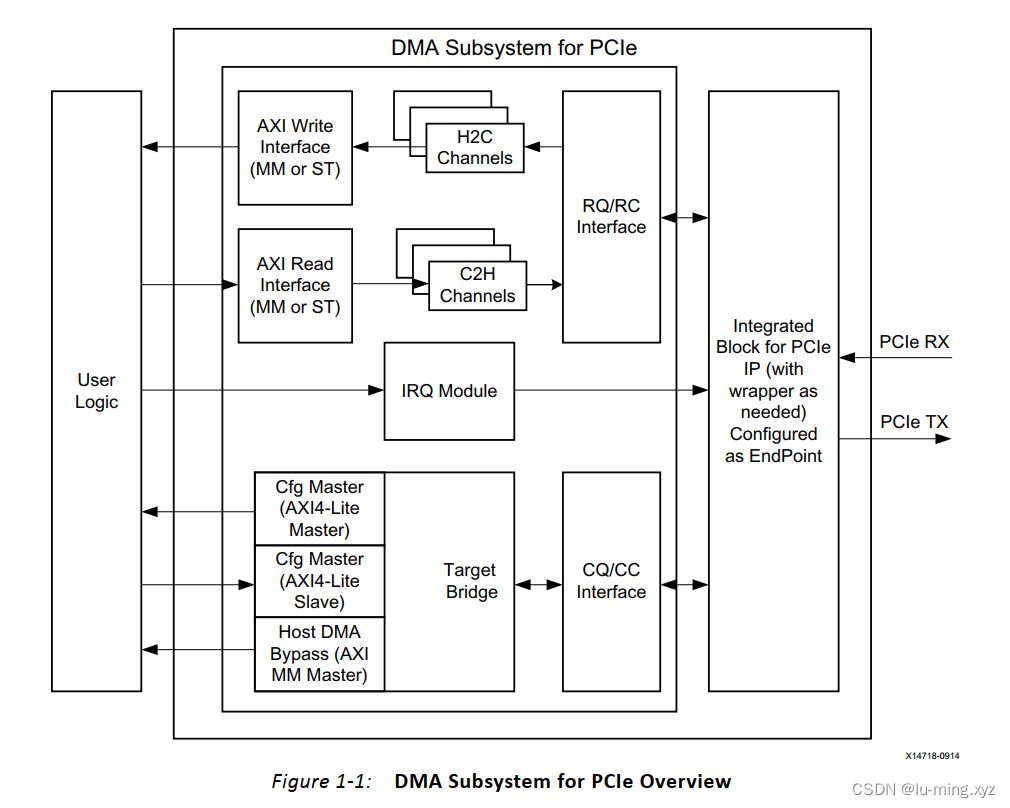

- DMA/Bridge Subsystem for PCI Express

Xilinx DMA/Bridge Subsystem for PCI Express(PCIe)利用PCI Express 2.1 或 3.x 集成块实现了高性能、可配置的Scatter Gather DMA。IP提供了可选的AXI4或AXI4-Stream用户接口。

结构:

可以看出DMA Subsystem fpr PCIe是在一个配置为Endpoint的Integrated Block for PCI Express IP 核的基础上加上一些实现DMA操作的模块。外围的很多功能模块都已经做好直接用就行,如果自己在Integrated Block for PCI Express IP 核的基础上开发一个XDMA应用。我们应用的时候注意,这个IP核已经把TLP相关的寄存器读写事务解析过了,与我们用户逻辑直接使用AXI4 或 AXI4-Stream 接口连接。关于AXI4接口,当然需要提前有个概念,所以我也是提前去稍微学习了一下:AXI4协议学习:架构、信号定义、工作时序和握手机制