????????时钟ip核是一个比较常用的IP核,主要用于对输入的时钟信号进行进行倍频、分频、调整相位。这些功能其实自己去实现也是相对来说比较简单的,但是既然vivado提供了这种封装好的IP核,我们就可以充分的去利用,减少开发者的工作量,而且时钟ip核也有一些比较高级的功能,比如,输出时钟频率和相位的动态调整等等。本篇文章主要记录时钟ip核的基本使用,并附带verilog和vhdl代码及对应的testbench文件,以供同学们相互交流学习。

一、时钟ip简介

? ? ? ? 在介绍时钟管理IP之前,可以先了解一下FPGA全局时钟资源的概念。全局时钟资源是指FPGA内部为实现系统时钟到达FPGA内部各CLB,IOB以及BSRAM等基本逻辑单元的延时和抖动最小化,采用全铜层工艺实现的专用缓冲和驱动结构。

? ? ? ? 全局时钟资源是一种布线资源,在设计中使用的十分普遍。全局时钟资源有多种形式,可以通过vivado的语言模板查看时钟资源的各种原语。

? ?

? ? ? ? 以下就是使用ip核的过程。

二、VIVADO中IP核的设置

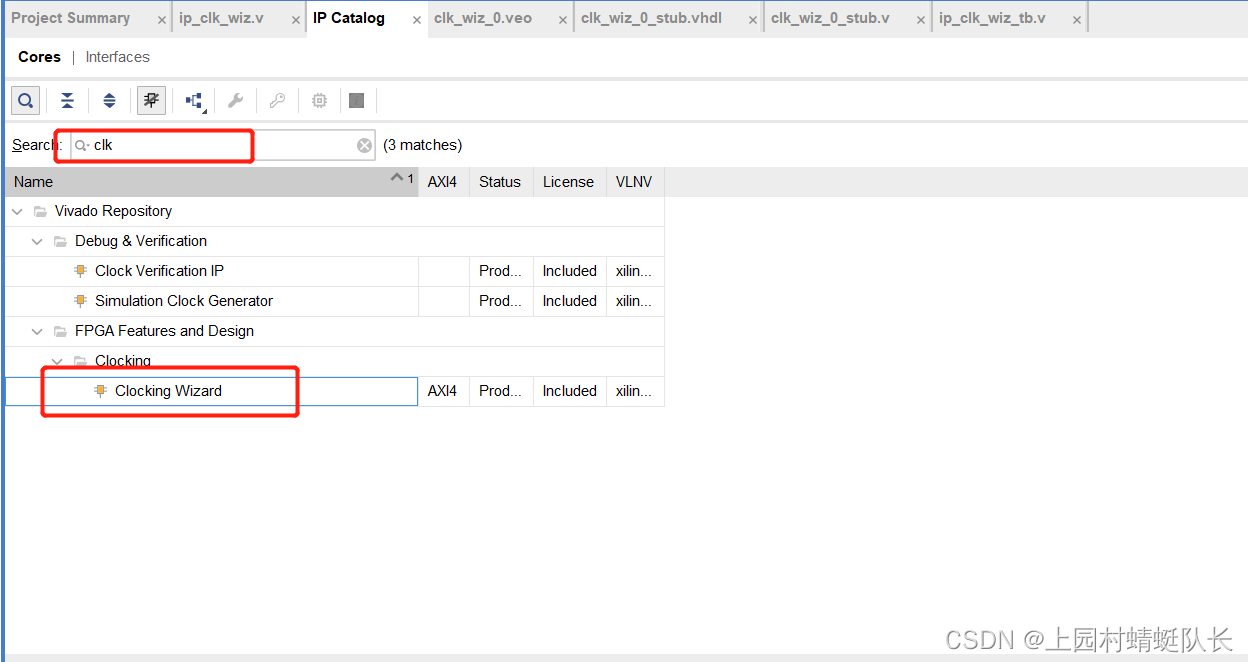

1、在ip catalog 中选择时钟ip核。(左侧)

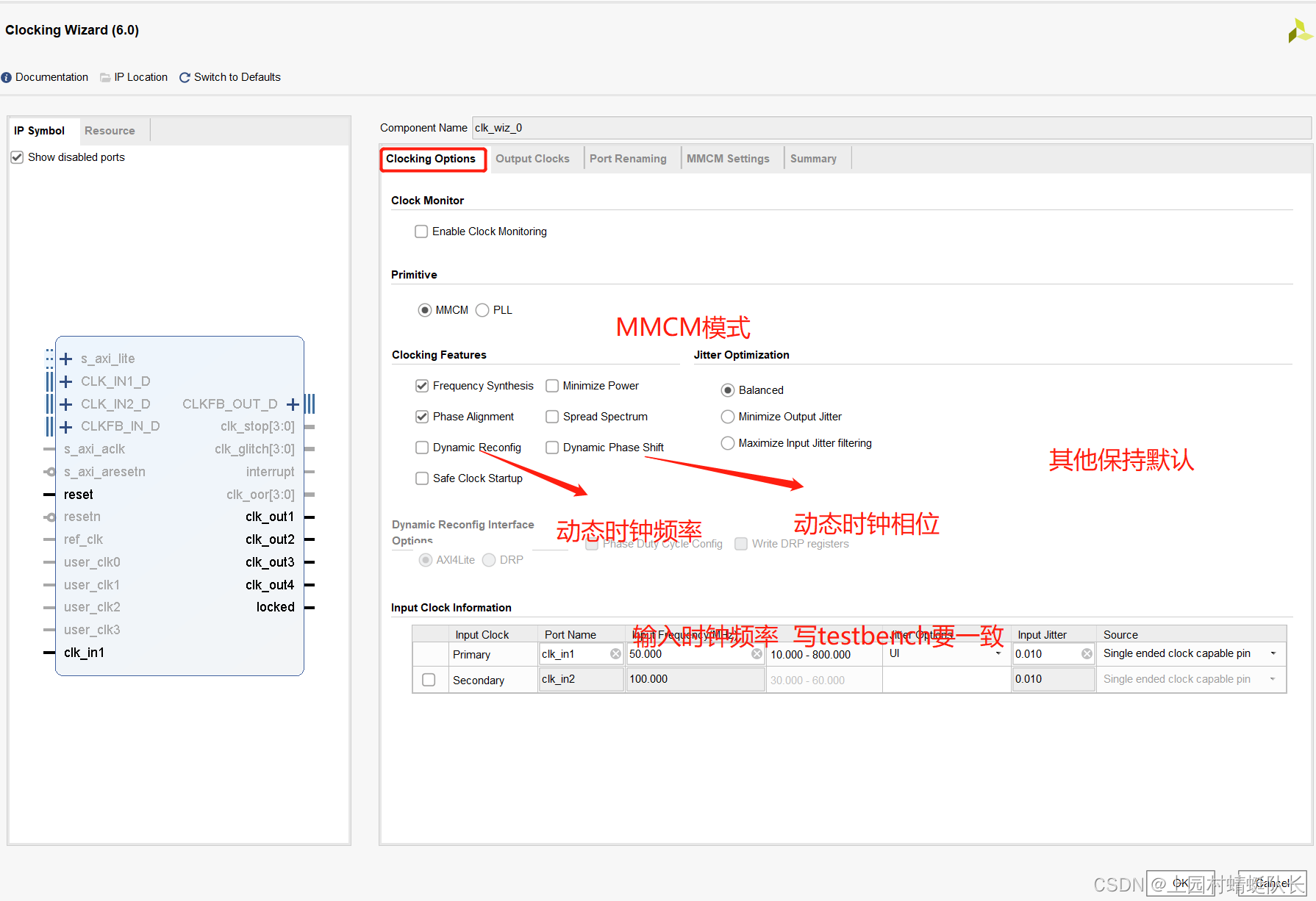

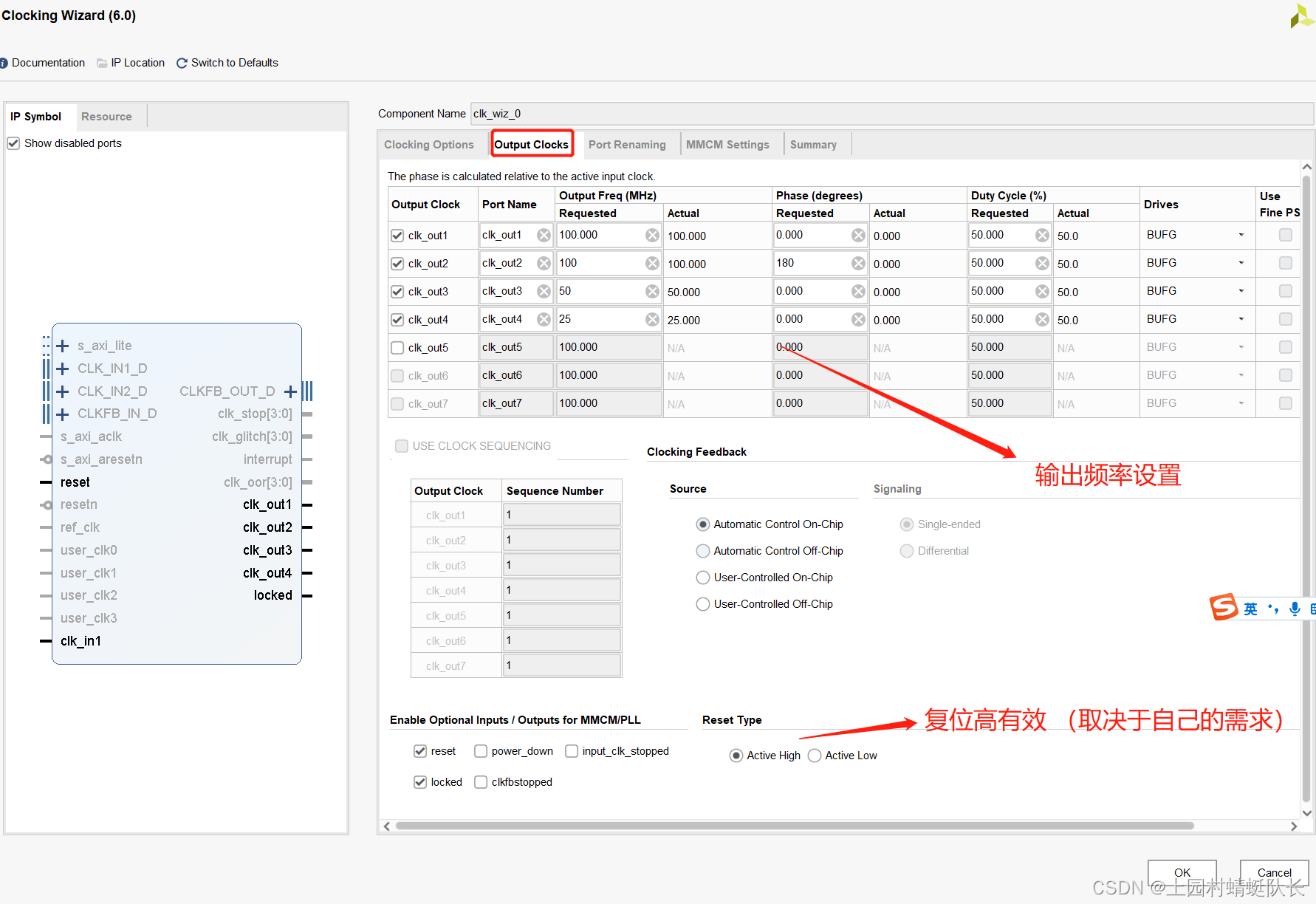

?2、设置ip核

?

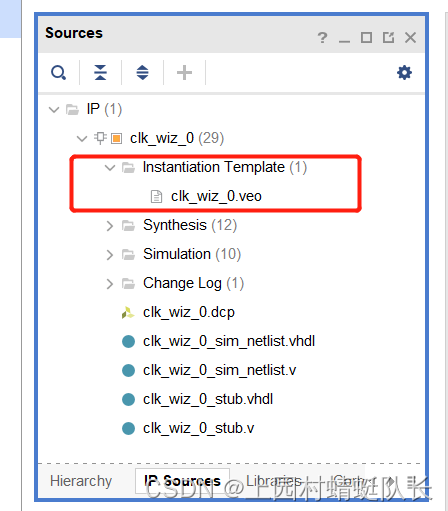

三、例化模板

vivado提供了例化模板,包括verilog和vhdl版本。例化模板在ip_source中获取。

?如果是verilog,点开这个veo文件就可以看见例化模板。

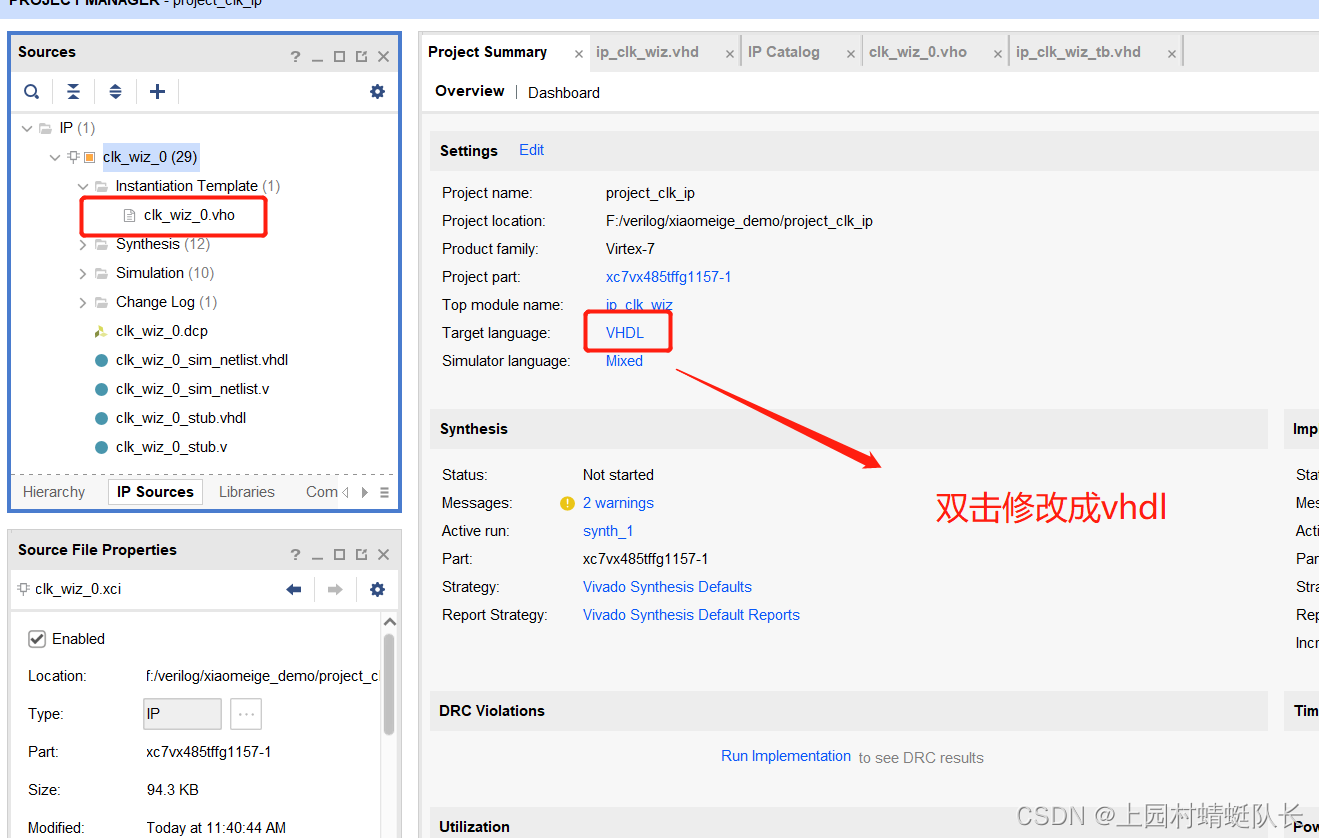

如果是VHDL,需要查看项目的target是不是VHDL,这样例化模板才能出现vhdl的vho文件。

Verilog例化ip核

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

.clk_out4(clk_out4), // output clk_out4

// Status and control signals

.reset(reset), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk_in1)); // input clk_in1VHDL例化ip核

component clk_wiz_0

port

(-- Clock in ports

-- Clock out ports

clk_out1 : out std_logic;

clk_out2 : out std_logic;

clk_out3 : out std_logic;

clk_out4 : out std_logic;

-- Status and control signals

reset : in std_logic;

locked : out std_logic;

clk_in1 : in std_logic

);

end component;

-- COMP_TAG_END ------ End COMPONENT Declaration ------------

-- The following code must appear in the VHDL architecture

-- body. Substitute your own instance name and net names.

------------- Begin Cut here for INSTANTIATION Template ----- INST_TAG

your_instance_name : clk_wiz_0

port map (

-- Clock out ports

clk_out1 => clk_out1,

clk_out2 => clk_out2,

clk_out3 => clk_out3,

clk_out4 => clk_out4,

-- Status and control signals

reset => reset,

locked => locked,

-- Clock in ports

clk_in1 => clk_in1

);四、需求分析和代码

需求介绍:

输入50Mhz时钟,产生100M输出,100M输出(180°相位),50M,25M。

verilog 顶层文件

设置好IP核后,verilog工程的顶层文件:

`timescale 1ns / 1ps

module ip_clk_wiz(

input sys_clk,

input sys_rst,

output clk_100m , //100Mhz时钟频率

output clk_100m_180deg, //100Mhz时钟频率,相位偏移180度

output clk_50m , //50Mhz时钟频率

output clk_25m //25Mhz时钟频率

);

wire locked;

clk_wiz_0 clk_wiz_0

(

// Clock out ports

.clk_out1(clk_100m), // output clk_out1

.clk_out2(clk_100m_180deg), // output clk_out2

.clk_out3(clk_50m), // output clk_out3

.clk_out4(clk_25m), // output clk_out4

// Status and control signals

.reset(sys_rst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(sys_clk)); // input clk_in1

endmodule

verilog testbench文件

`timescale 1ns / 1ps

module ip_clk_wiz_tb(

);

reg sys_clk;

reg sys_rst;

wire clk_100m;

wire clk_100m_180deg;

wire clk_50m;

wire clk_25m;

always #10 sys_clk = ~sys_clk;

initial begin

sys_clk = 1'b0;

sys_rst = 1'b1;

#200//延时200

sys_rst = 1'b0;

end

ip_clk_wiz u_ip_clk_wiz(

.sys_clk (sys_clk ),

.sys_rst (sys_rst ),

.clk_100m (clk_100m ),

.clk_100m_180deg (clk_100m_180deg),

.clk_50m (clk_50m ),

.clk_25m (clk_25m )

);

endmodule

VHDL顶层文件

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity ip_clk_wiz is

Port ( sys_clk: in std_logic;

sys_rst: in std_logic;

clk_100m: out std_logic;

clk_100m_180: out std_logic;

clk_25m: out std_logic;

clk_50m: out std_logic

);

end ip_clk_wiz;

architecture Behavioral of ip_clk_wiz is

signal locked :std_logic;

component clk_wiz_0

port

(-- Clock in ports

-- Clock out ports

clk_out1 : out std_logic;

clk_out2 : out std_logic;

clk_out3 : out std_logic;

clk_out4 : out std_logic;

-- Status and control signals

reset : in std_logic;

locked : out std_logic;

clk_in1 : in std_logic

);

end component;

begin

-- COMP_TAG_END ------ End COMPONENT Declaration ------------

-- The following code must appear in the VHDL architecture

-- body. Substitute your own instance name and net names.

------------- Begin Cut here for INSTANTIATION Template ----- INST_TAG

i_clk : clk_wiz_0

port map (

-- Clock out ports

clk_out1 => clk_100m,

clk_out2 => clk_100m_180,

clk_out3 => clk_50m,

clk_out4 => clk_25m,

-- Status and control signals

reset => sys_rst,

locked => locked,

-- Clock in ports

clk_in1 => sys_clk

);

end Behavioral;

VHDL-testbench文件

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity ip_clk_wiz_tb is

-- Port ( );

end ip_clk_wiz_tb;

architecture Behavioral of ip_clk_wiz_tb is

signal sys_clk:std_logic;

signal sys_rst:std_logic;

signal clk_100m:std_logic;

signal clk_50m:std_logic;

signal clk_100m_180:std_logic;

signal clk_25m:std_logic;

component ip_clk_wiz

Port ( sys_clk: in std_logic;

sys_rst: in std_logic;

clk_100m: out std_logic;

clk_100m_180: out std_logic;

clk_25m: out std_logic;

clk_50m: out std_logic

);

end component;

begin

i1:ip_clk_wiz

port map(

sys_clk => sys_clk,

sys_rst => sys_rst,

clk_100m => clk_100m,

clk_100m_180 => clk_100m_180,

clk_25m => clk_25m,

clk_50m => clk_50m

);

init : process

begin

wait for 10 ns;

sys_clk<='0';

wait for 10 ns; --- 和ip输入保持一致

sys_clk<='1';

end process init;

always : process

-- optional sensitivity list

-- ( )

-- variable declarations

begin

-- code executes for every event on sensitivity list

--- sys_clk <= '0';

sys_rst <= '1';

wait for 201 ns;

sys_rst <= '0';

wait;

end process always;

end Behavioral;

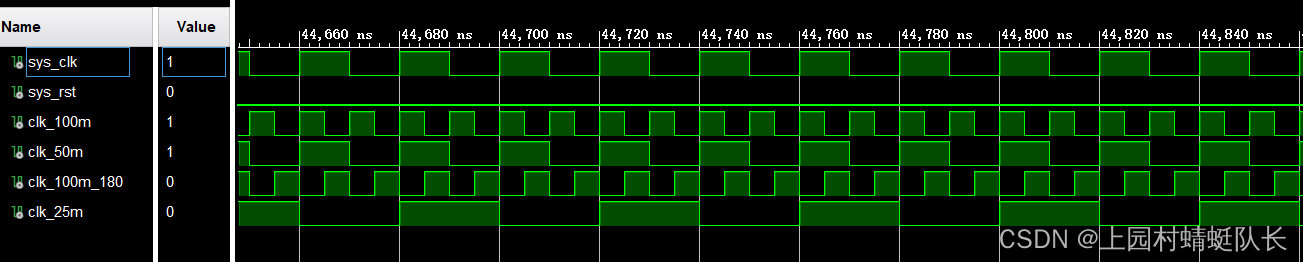

仿真结果:

????????由此图可以看出,完全符合我们的输出要求。