FPGA学习笔记-IP核

本篇文章暂不完整,还需要等后续更新代码部分

一、什么是IP核?

IP核,全称知识产权核(英语:Semiconductor Intellectual Property Core),是在集成电路的**可重用设计方法学**中,指某一方提供的、形式为逻辑单元、芯片设计的可重用模组。

IP核通常已经通过了设计验证,设计人员以IP核为基础进行设计,可以缩短设计所需的周期。[1]IP核可以通过协议由一方提供给另一方,或由一方独自占有。IP核的概念源于产品设计的专利证书和源代码的版权等。设计人员能够以IP核为基础进行特殊应用积体电路或现场可编程逻辑门阵列/FPGA的逻辑设计,以减少设计周期。

IP核分为软核、硬核和固核。软核通常是与工艺无关、具有寄存器传输级硬件描述语言描述的设计代码,可以进行后续设计;硬核是前者通过逻辑综合、布局、布线之后的一系列表征文件,具有特定的工艺形式、物理实现方式;固核则通常介于上面两者之间,它已经通过功能验证、时序分析等过程,设计人员可以以逻辑门级网表的形式获取。[2]

二、RAM

RAM全称是Random Access Memory,即随机存取存储器,他可以把数据写入任一指定地址的存储单元,也可以随时从任一指定中独处数据。其读写速度是由时钟频率决定的。RAM主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。其特点适合双向交换数据。

Quartus II自带的存储器IP核分为RAM IP核和ROM IP核,每种又分为单端口和双端口。其中双端口又分为真双端口与伪双端口/简单双端口。

- 单端口:只有一个端口,读写数据不能同时进行,共用数据通道。

- 伪双端口:拥有两个数据通道,一个用来写一个用来读。

- 真双端口:拥有两个数据通道,两个通道都可以用来读或写。

一片RAM中分为许多小格,每一片容量为36k,根据设定的位宽决定了这片RAM可以存放分为几格,位宽一啊不能设定为1、2、4、8、16、32等,每相邻的两片RAM可以合成一片RAM,这片RAM同样是双端口,可以独立的完成读写操作,且在读和写都可以配置位宽。

RAM读写速度一般都很快,所以通常作为操作系统或其他正在运行中的程序的临时资料存储介质。

RAM 存储器可以进一步分为静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)两大类。SRAM 具有快速访问的优点,但生产成本较为昂贵,一个典型的应用是缓存。而 DRAM 由于具有较低的单位容量价格,所以被大量的采用作为系统的主存。

**其中,集成于芯片中(FPGA)的RAM属于SRAM,**芯片中的SRAM有以下几个用途:

- 作为微控制器的RAM或者cache(通常从32 bytes到128 kilobytes)

- 作为x86等微处理器的缓存(如L1、L2、L3)

- 作为寄存器(参见寄存器堆)

- 用于特定的ICs或ASIC(通常在几千字节量级)

- 用于FPGA与CPLD

1. RAM特点

- 随机存取

? 所谓“随机存取”,指的是当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。相对地,有串行访问存储器包括顺序访问存储器(如:磁带)和直接访问存储器(如:磁盘)。

- 易矢性

? 当电源关闭时 RAM 不能保留数据。如果需要保存数据,就必须把它们写入一个长期的存储设备中(例如硬盘)。RAM 和 ROM 相比,两者的最大区别是 RAM 在断电以后保存在上面的数据会自动消失,而 ROM 则不会。

- 高访问速度(DRAM较高,SRAM则很高)

? 现代的随机存取存储器几乎是所有访问设备中写入和读取速度最快的,访问延迟也和其他涉及机械运作的存储设备(如硬盘、光盘驱动器)相比,也显得微不足道。但 DRAM 速度仍然不如作为 CPU 缓存用的 SRAM。

- 需要刷新(DRAM)

? 现代的随机存取存储器依赖存储器存储资料。电容器充满电后代表 1(二进制),未充电的代表 0。由于电容器或多或少有漏电的情形,若不作特别处理,电荷会渐渐随时间流失而使资料发生错误。刷新是指重新为电容器充电,弥补流失了的电荷。DRAM 的读取即有刷新的功效,但一般的定时刷新并不需要作完整的读取,只需作该芯片的一个列(Row)选择,整列的资料即可获得刷新,而同一时间内,所有相关记忆芯片均可同时作同一列选择,因此,在一段期间内逐一做完所有列的刷新,即可完成所有存储器的刷新。需要刷新正好解释了随机存取存储器的易失性。

- 时钟频率与功耗(SRAM)

? SRAM功耗取决于它的访问频率。如果用高频率访问SRAM,其功耗比得上DRAM。有的SRAM在全带宽时功耗达到几个瓦特量级。另一方面,SRAM如果用于温和的时钟频率的微处理器,其功耗将非常小,在空闲状态时功耗可以忽略不计―几个微瓦特级别。

2. 单端口RAM

单端口RAM只有一个端口,读与写都通过这个端口进行。单端口RAM只有一组数据总线、地址总线、时钟信号以及其他控制信号。

单端口描述如下:

data: RAM写数据端口

address:RAM读写地址端口,读地址与写地址共用同一组地址

wren:写使能信号,高电平有效,高电平时data口的数据才能被写入

rden:读使能信号,高电平有效,高电平时RAM中的数据才能被读出

clken:时钟使能信号,用于控制时钟

aclr:异步复位信号,高电平有效

inclock\outclock:单口RAM端口支持双时钟模式和单时钟模式。

双时钟模式:输入时钟控制存储器模块的所有输入寄存器,包括数据、地址、wren以及rden寄存器;输出时钟控制数据输出寄存器。

单时钟模式:没有inclock与outclock之分,只有一个clock信号,通过单时钟以及时钟使能来控制(M9K)存储器模块中的所有寄存器。

2. 双端口RAM

**伪双口/简单双口:**两组数据通道,一组用来读数据与地址线,一组用来写数据与地址线,能同时进行读和写的操作,但不能同时对同一地址进行读和写。

**真双口RAM:**两组数据通道,每组都能用来读、写数据数据与地址线。能够同时读写两个端口,也能够一个端口写的同时,另一个端口读。

真双口RAM其实就是两个单口RAM组合在一起构成的,只是真双口RAM里的两个单口RAM是操作同一片存储空间。

三、FIFO

FIFO全称为First In First Out即先进先出。FPGA使用的FIFO一般指的是对数据的存储具有先进先出的一个缓存器,常被用于数据的缓存或告诉异步数据的交互,即所谓的跨时钟域信号传递。

它与FPGA内部的RAM和ROM的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带来的缺点就是不能像RAM和ROM那样可以由地址线决定读取或写入某个指定的地址。

FIFO是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。其实,多位宽数据的异步传输问题,无论是从快时钟到慢时钟域,还是从慢时钟到快时钟域,都可以使用 FIFO 处理。

1. 分类

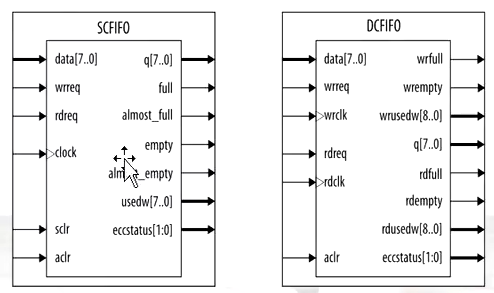

输入时钟的角度分类:单时钟SCFIFO与双时钟DCFIFO;其中,DCFIFO从输出数据的位宽的角度又可以分为普通双时钟DCFIFO和混合宽度双时钟FIFO(DCFIFO_MIXED_WIDTHS)

- SCFIFO:

? 单时钟FIFO具有一个独立的时钟端口clock,因此,所有的输入输出信号都同步于clock信号。双时钟FIFO结构中,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟wrclk,所有与读相关的信号都是同步于读时钟rdclk。

? 通常应用于同步时钟的数据缓存。

- DCFIFO:

? 双时钟FIFO常用于跨时钟域的数据信号的传递,例如时钟域A下的数据datal传递给异步时钟域B,当datal为连续变化信号时,如果直接传递给时钟域B则可能会导致收非所送的情况,即在采集过程中会出现包括亚稳态(数据采样失真)问题在内的一系列问题,使用双时钟FIFO能够将不同时钟域中的数据同步到所需的时钟域中。

2. 参数(请结合代码理解)

FIFO的宽度:FIFO一次读写操作的数据位N;

FIFO的深度:FIFO可以存储多少个宽度为N位的数据;

空标志:对于双时钟FIFO,又分为读空标志rdempty和写空标志wrempty;FIFO已空或将

要空时由FIFO的状态电路送出的一个信号,以阻止继续从FIFO中读出数据而造成无效数据的读出。

满标志:对于双时钟FIFO,又分为读满标志rdfull和写满标志wrfull;FIFO已满或将要写

满时由FIFO的状态电路送出的一个信号,以阻止继续向FIFO中写数据而造成溢出。

读时钟:读FIFO时所遵循的时钟,在每个时钟的上升沿触发。

写时钟:写FIFO时所遵循的时钟,在每个时钟的上升沿触发。

wrusedw:在写时钟域下,FIFO中剩余的数据量;

rdusedw:在读时钟域下,FIFO中剩余的数据量。

3. 原理

工作流程

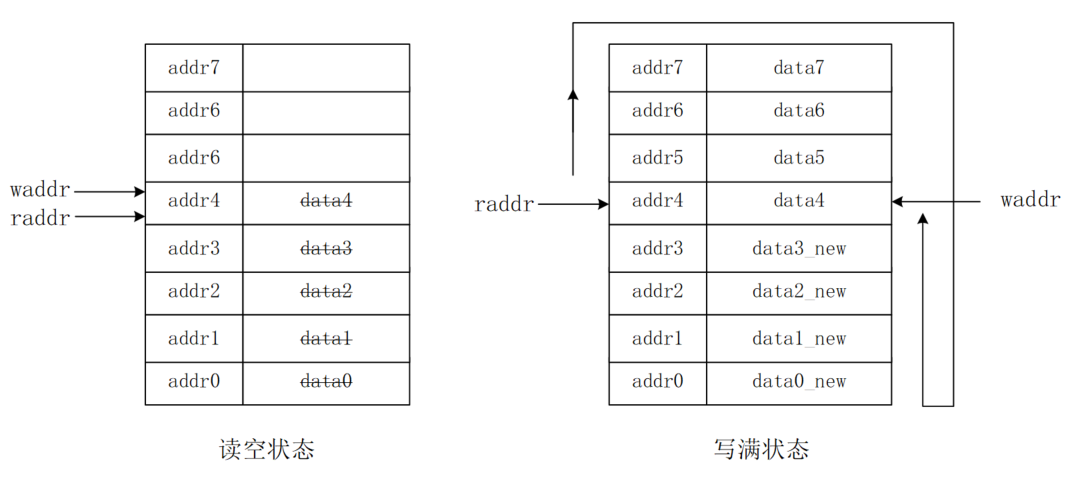

复位之后,在写时钟和状态信号的控制下,数据写入 FIFO 中。RAM 的写地址从 0 开始,每写一次数据写地址指针加一,指向下一个存储单元。当 FIFO 写满后,数据将不能再写入,否则数据会因覆盖而丢失。

FIFO 数据为非空、或满状态时,在读时钟和状态信号的控制下,可以将数据从 FIFO 中读出。RAM 的读地址从 0 开始,每读一次数据读地址指针加一,指向下一个存储单元。当 FIFO 读空后,就不能再读数据,否则读出的数据将是错误的。

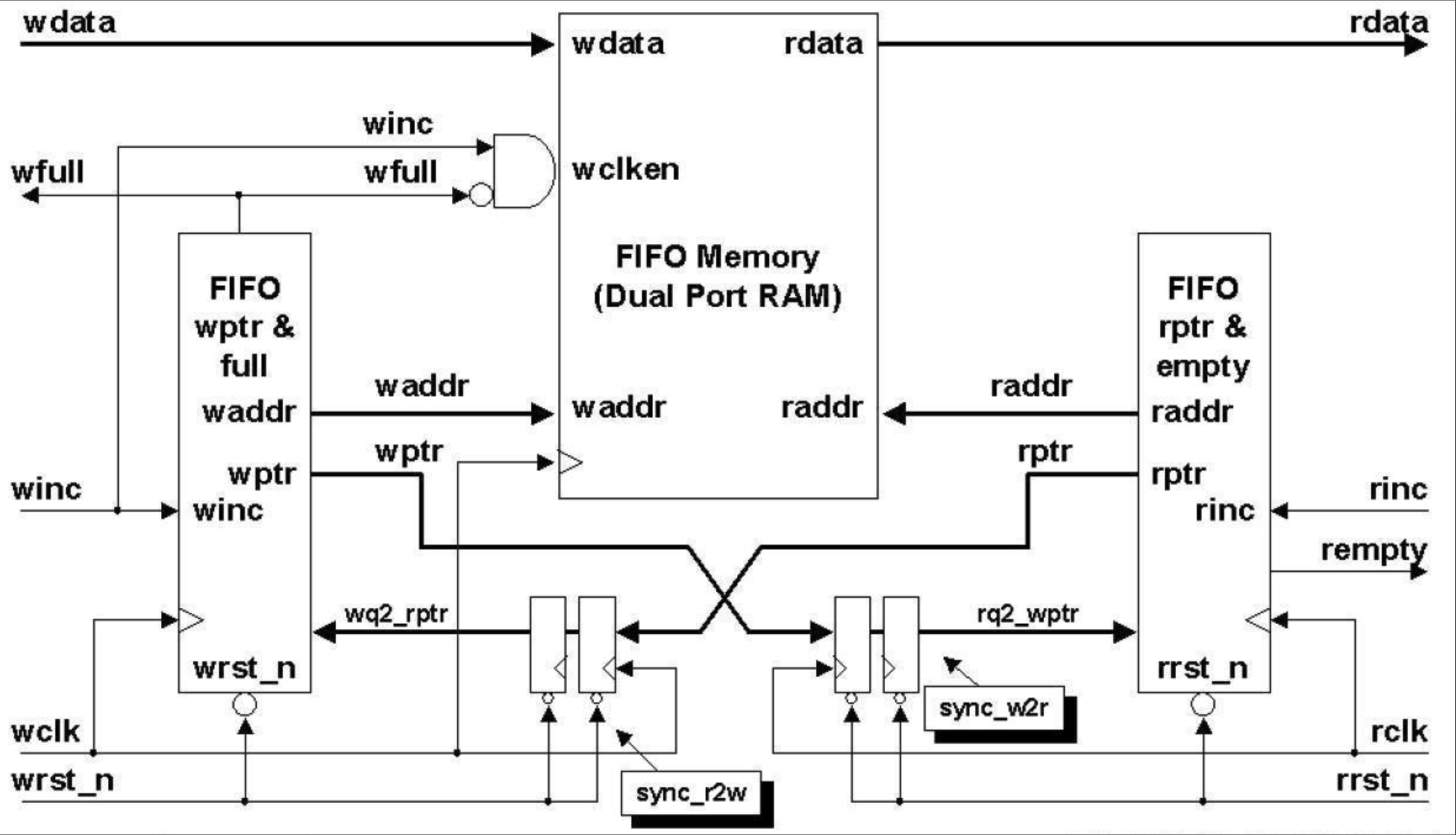

FIFO 的存储结构为双口 RAM,所以允许读写同时进行。典型异步 FIFO 结构图如下所示。端口及内部信号将在代码编写时进行说明。

读写时刻

关于写时刻,只要 FIFO 中数据为非满状态,就可以进行写操作;如果 FIFO 为满状态,则禁止再写数据。

关于读时刻,只要 FIFO 中数据为非空状态,就可以进行读操作;如果 FIFO 为空状态,则禁止再读数据。

不管怎样,一段正常读写 FIFO 的时间段,如果读写同时进行,则要求写 FIFO 速率不能大于读速率。

读空状态

开始复位时,FIFO 没有数据,空状态信号是有效的。当 FIFO 中被写入数据后,空状态信号拉低无效。当读数据地址追赶上写地址,即读写地址都相等时,FIFO 为空状态。

因为是异步 FIFO,所以读写地址进行比较时,需要同步打拍逻辑,就需要耗费一定的时间。所以空状态的指示信号不是实时的,会有一定的延时。如果在这段延迟时间内又有新的数据写入 FIFO,就会出现空状态指示信号有效,但是 FIFO 中其实存在数据的现象。

严格来讲该空状态指示是错误的。但是产生空状态的意义在于防止读操作对空状态的 FIFO 进行数据读取。产生空状态信号时,实际 FIFO 中有数据,相当于提前判断了空状态信号,此时不再进行读 FIFO 数据操作也是安全的。所以,该设计从应用上来说是没有问题的。

写满状态

开始复位时,FIFO 没有数据,满信号是无效的。当 FIFO 中被写入数据后,此时读操作不进行或读速率相对较慢,只要写数据地址超过读数据地址一个 FIFO 深度时,便会产生满状态信号。此时写地址和读地址也是相等的,但是意义是不一样的。

此时经常使用多余的 1bit 分别当做读写地址的拓展位,来区分读写地址相同的时候,FIFO 的状态是空还是满状态。当读写地址与拓展位均相同的时候,表明读写数据的数量是一致的,则此时 FIFO 是空状态。如果读写地址相同,拓展位为相反数,表明写数据的数量已经超过读数据数量的一个 FIFO 深度了,此时 FIFO 是满状态。当然,此条件成立的前提是空状态禁止读操作、满状态禁止写操作。

同理,由于异步延迟逻辑的存在,满状态信号也不是实时的。但是也相当于提前判断了满状态信号,此时不再进行写 FIFO 操作也不会影响应用的正确性。