在vivado平台我们想要使用SelectIO来实现LVDS的功能,我们该如何下手呢,首先当然得先创建IP核了,那对于新手来说大概不知道从哪里下手,当你看到这篇文章时,或许对你有所帮助,在vivado平台上操作和ISE平台大同小异,可能这篇将的就稍微快一点。

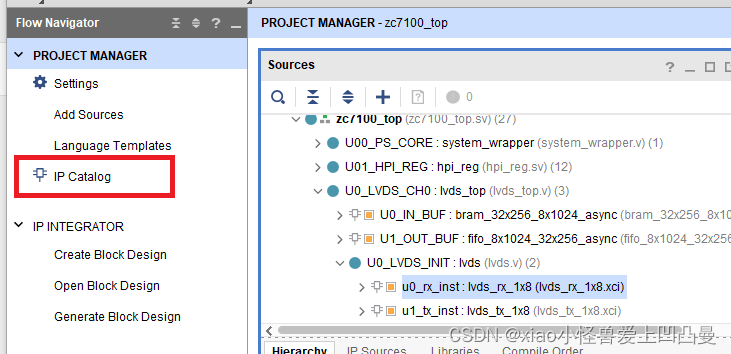

step1: 当我们使用的是vivado平台时,我们直接点击 IP Catalog。

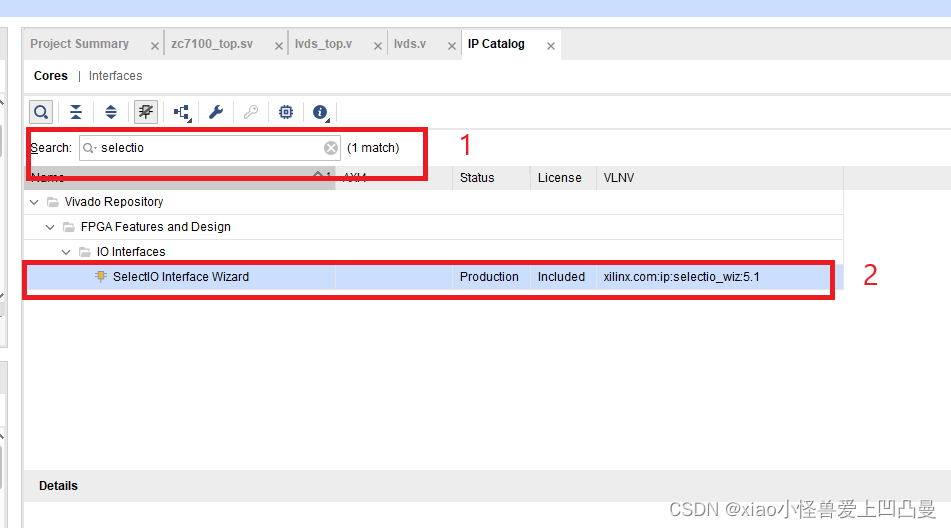

step2: 进入如下界面后直接在Search栏中搜索 selectio,然后就会出现图中标记2出我们想要的IP核了,下面我们直接双击 SelectIO Interface Wizard。

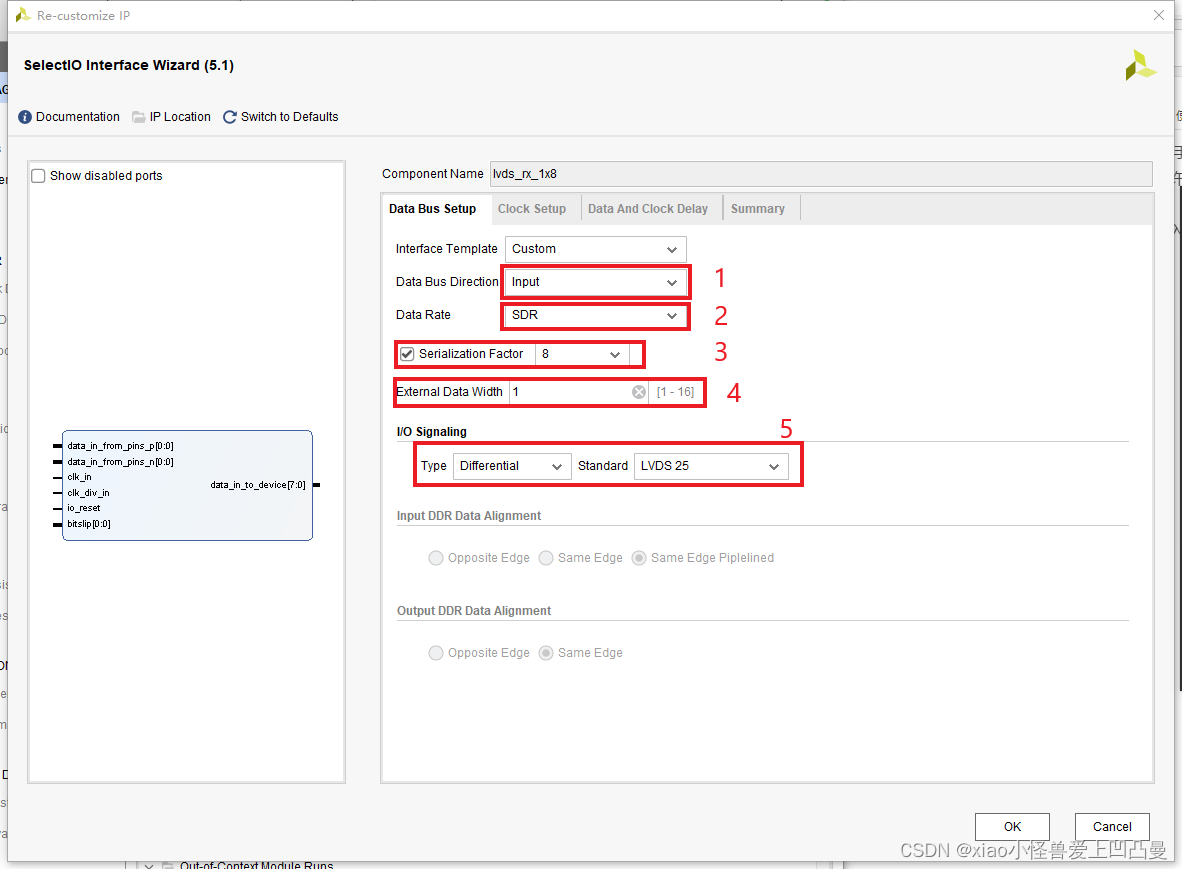

step3: 进入如下界面,就是我们需要重点配置的地方了

1.Data Bus Direction 是配置我们数据总线的方向的,和ISE平台一样,有4种模式选择,input、output、bidirectional、input and output 。(我们这里将 IP 配置成 input模式,即差分端口PIN为输入)

2.Data Rate是选择单倍速率还是双倍速率,单倍速率SDR(single data rate)就是在时钟的上升沿改变数据;双倍速率DDR(double data rate)就是在时钟的上升沿和下降沿都采集数据。(这里就不多说了,我们正常配置SDR)

3. Serialization factor我们还是配置 为 8。

4. External Data Width 我们还是配置为1,代表使用1组差分对。

5. I/O signaling是选择Different信号的类型,因为我们需要使用LVDS差分功能。

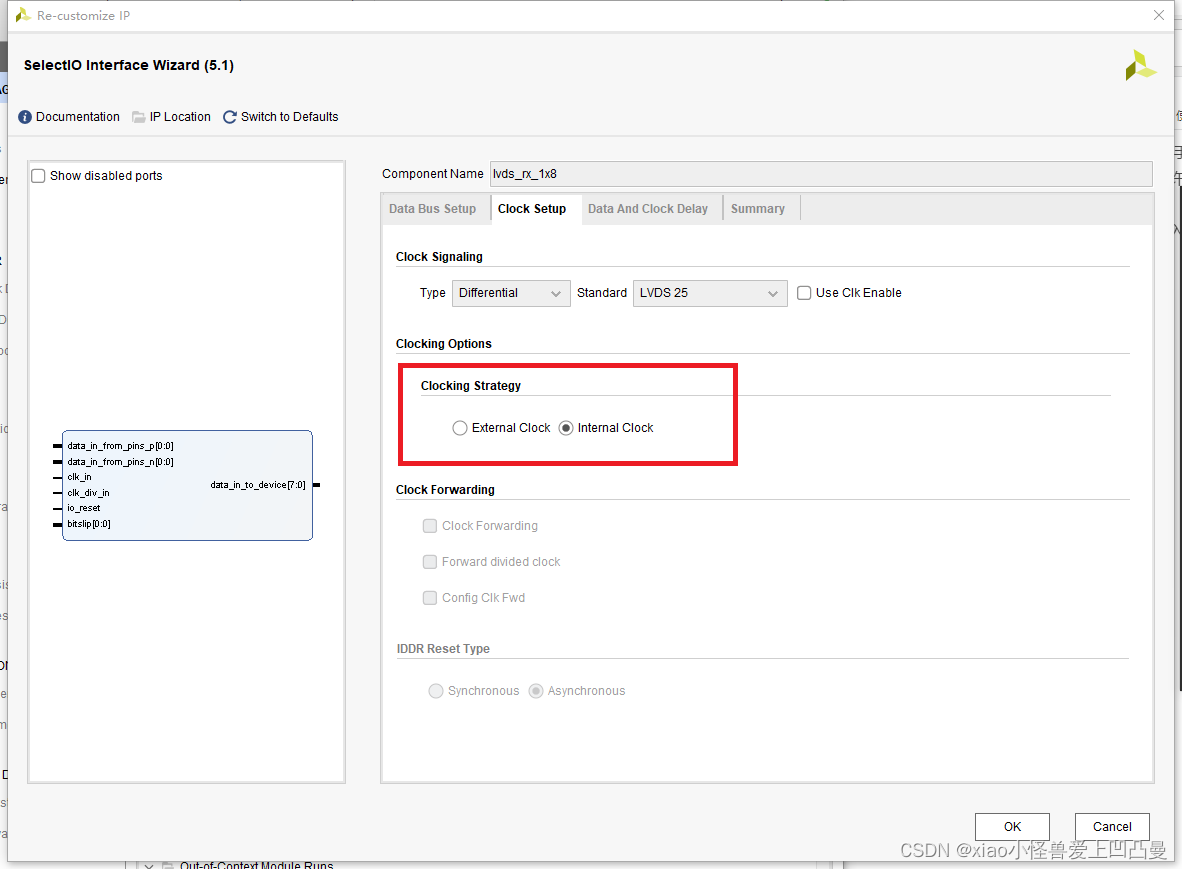

6. 点击 clock setup。

step4: 这里是关于时钟的选择,我还是使用FPGA 的内部时钟,所以勾选 Interal clock。

PS:当我们勾选内部时钟时, Clock 的Type 会自动变成 Differential;在output模式下,例化代码是没有差分时钟端口的,在input模式下,例化代码是有差分时钟端口,至于需不需要用看项目设计。

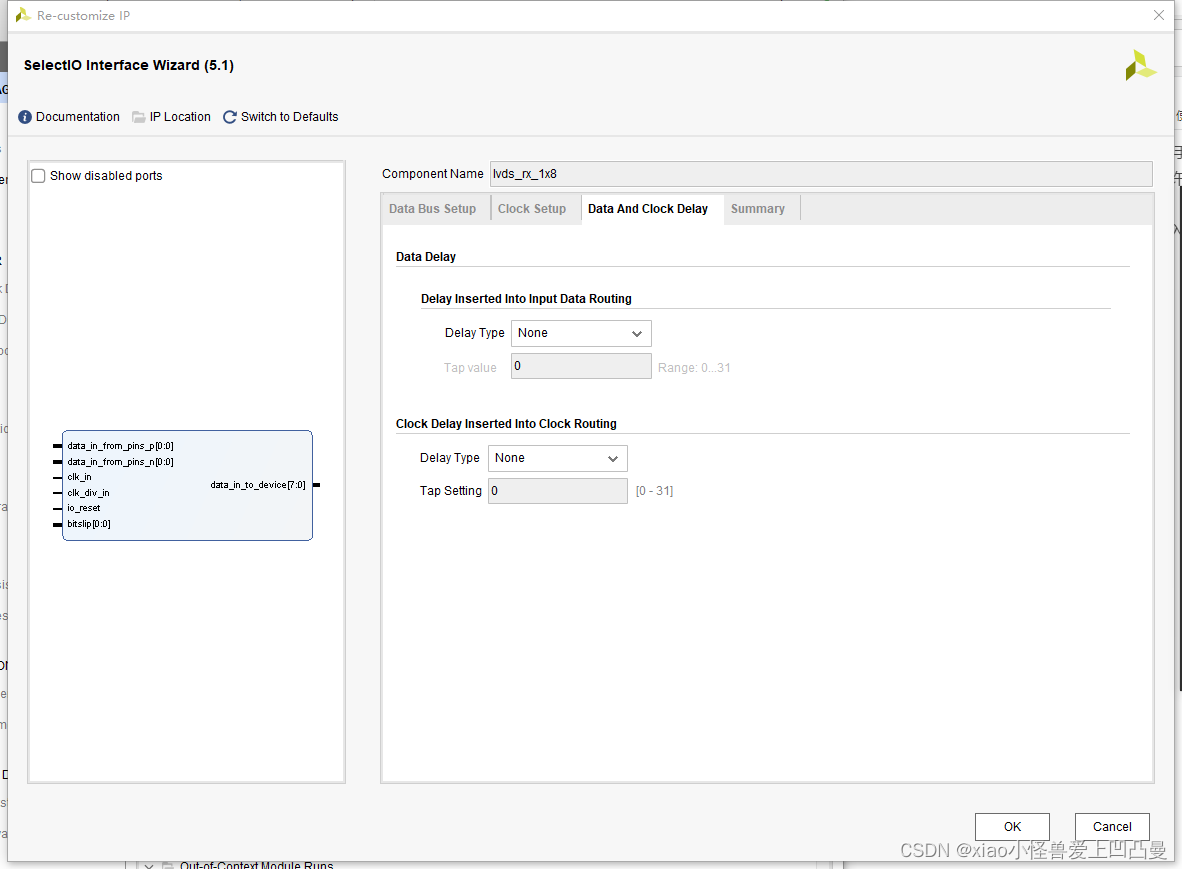

然后点击data and clock delay。

step5: 进入如下界面,这里同样是配置延迟的,一般情况下是不需要设置的。

然后点击Summary。

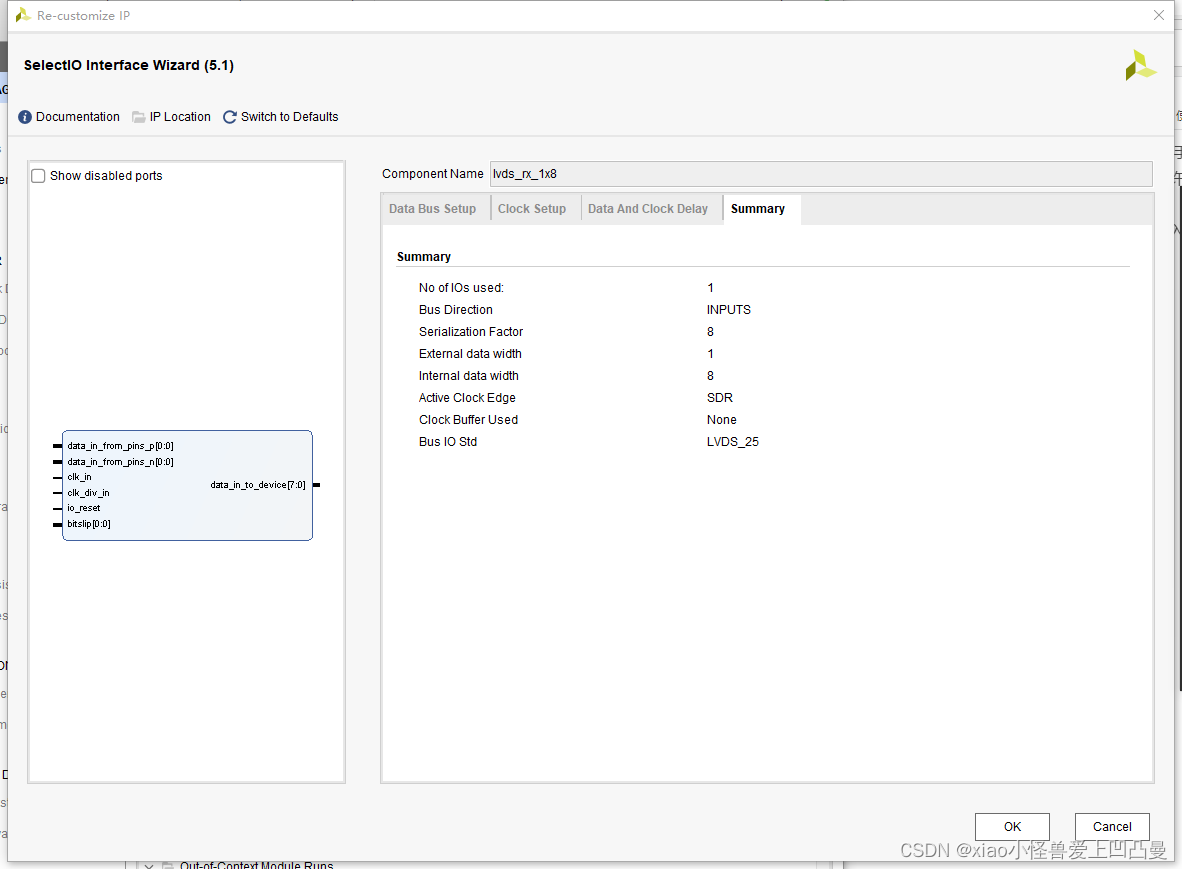

step6: 进入此界面查看自己配置信息是否正确,确认完成就之间点击OK生成IP。

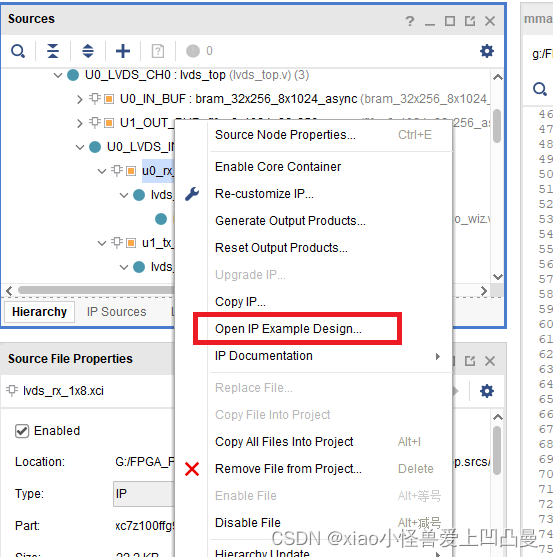

step6: 在IP生成后,我们点击右击我们的IP会出现如下界面,我们可以点击open ip example design就可以添加官方例程,通过官方例程仿真深入学习。

注意注意:在我们Data Bus Direction配置成 input模式时,是没有bitslip的选项的,只有配置成output模式时才有bitslip的选项,因为我们只有在接收数据时需要用 BITSLIP 来做输出数据对齐,获取正确的并行数据序。