参考:pg182 - UltraScale FPGAs Transceivers Wizard v1.7

参考:UG576 - UltraScale Architecture GTH Transceivers

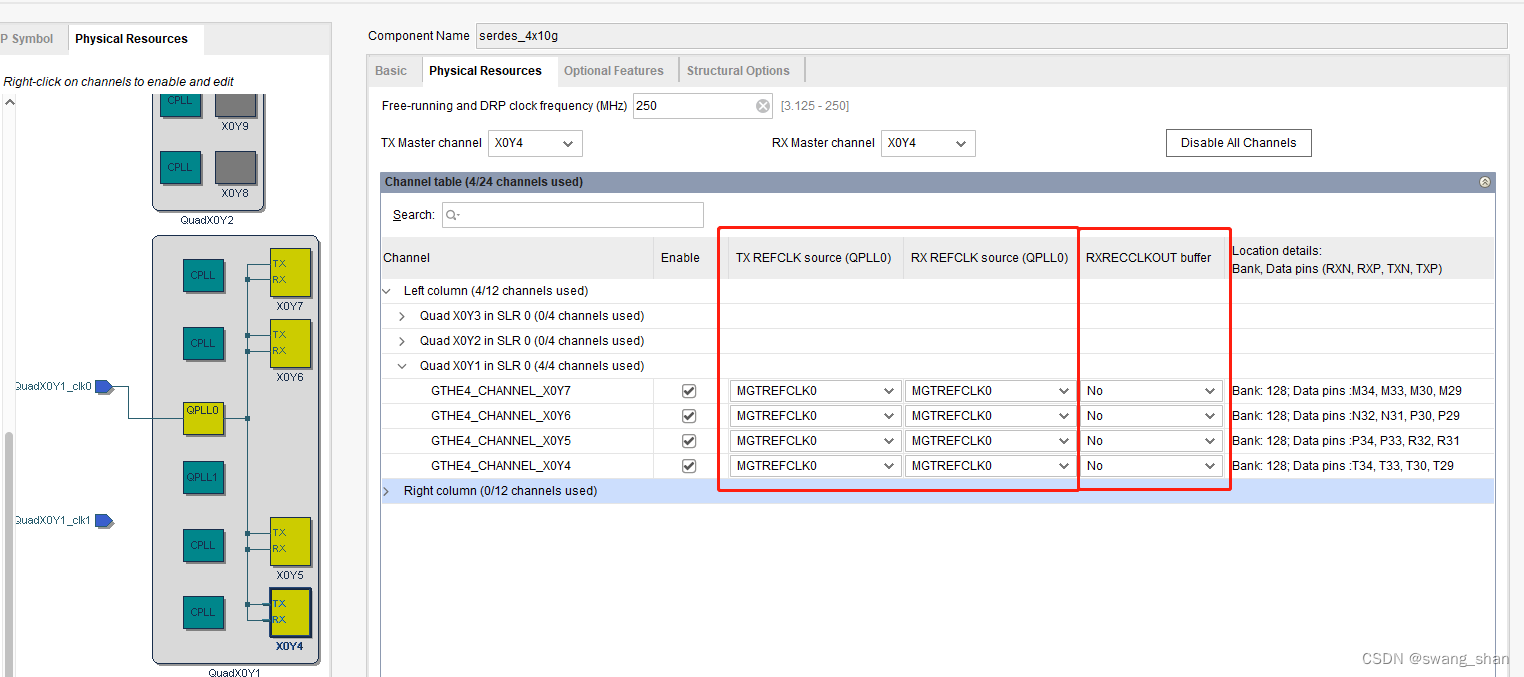

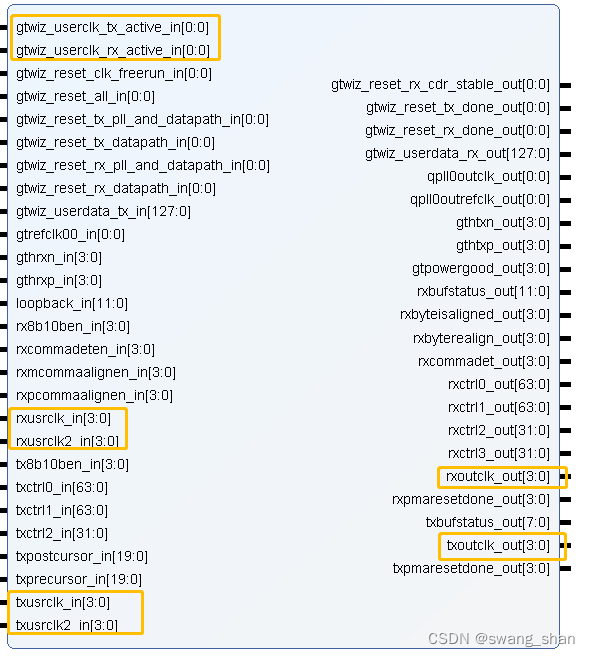

此工程使用 xilinx ZU9eg,下图为gth的channel选择。

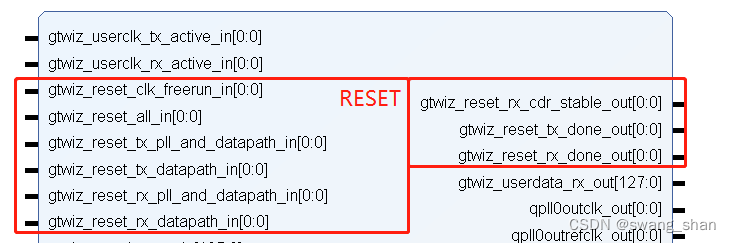

复位模块

gtwiz_reset_clk_freerun_in: 复位控制器辅助块的自由运行时钟,要启用此模块,必须提供此时钟

gtwiz_reset_all_in:复位TX和RX的PLL和Datapath。复位状态机是由其下降沿初始化的。

gtwiz_reset_tx_pll_and_datapath_in:复位TX的PLL和Datapath.

gtwiz_reset_tx_datapath_in:复位TX的Datapath.

gtwiz_reset_rx_pll_and_datapath_in:复位RX的PLL和Datapath.

gtwiz_reset_rx_datapath_in:复位RX的Datapath.

gtwiz_reset_tx_done_out:在完成TX的复位后拉高,与主通道TXUSERCLK2同步。

gtwiz_reset_rx_done_out:在完成RX的复位后拉高,与主通道RXUSERCLK2同步。

gtwiz_reset_rx_cdr_stable_out:标明RX原语的时钟和数据恢复(CDR)电路是稳定的。保留;不使用

注意: 如果 TX和 RX的datapaths 由QPLL0提供时钟,gtwiz_reset_tx_pll_and_datapath_in 和 gtwiz_reset_rx_pll_and_datapath_in这两个输入中的任何一个都将重置共享的QPLL0,从而导致在另一个数据方向上潜在的意外链路丢失。谨慎使用。

时钟模块

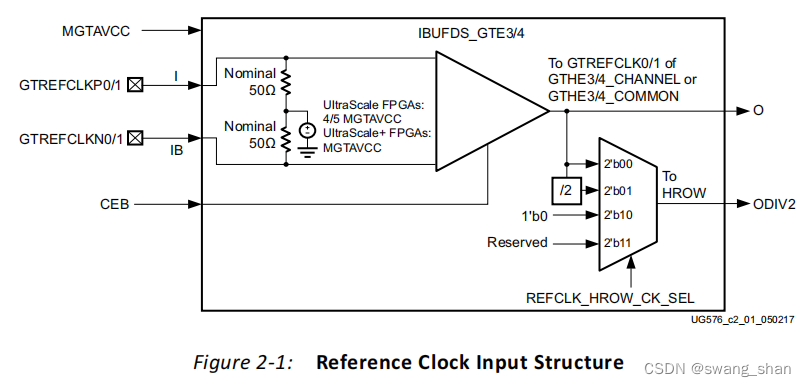

1、reference clock

reference clock 在 GTH 中支持输入和输出两种模式。

在参考时钟输入模式下,在专用参考时钟I/O引脚上提供一个时钟,用于驱动QPLL或者CPLL。使用IBUFDS_GTE4 。在example design中有用法示例,可以直接借鉴。

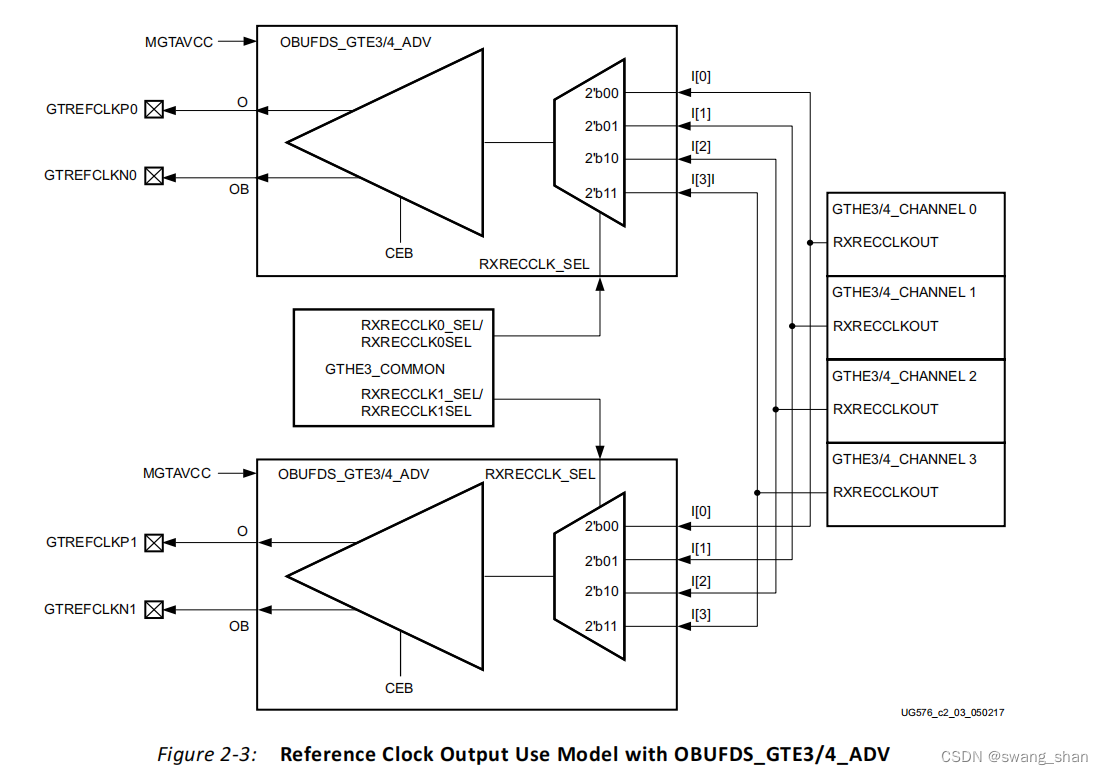

参考时钟输出模式,是从同一QUAD中的四个通道出来的恢复时钟RXRECCLKOUT,可以路由到专用的参考时钟I/O引脚。这个输出时钟可以用作不同位置的参考时钟输入。在运行期间无法更改操作模式。可以通过两个软件原语之一来访问: OBUFDS_GTE3/4和OBUFDS_GTE3/4_ADV。两个原语的选择取决于:

- 当RXRECCLKOUT始终来自同一通道时,使用OBUFDS_GTE3/4。

- 如果提供RXRECCLKOUT的通道在运行期间发生更改,使用OBUFDS_GTE3/4_ADV。

当使用OBUFDS_GTE3/4_ADV原语时,还必须实例化GTHE3/4_COMMON原语。在使用OBUFDS_GTE3/4原语时,不需要实例化GTHE3/4_COMMON。详见图2-3.一般克直接使用example design中的示例。

下图是在此工程里面的REF时钟选择。未使用输出模式。

2、时钟辅助模块

gtwiz_userclk_tx_active_in / gtwiz_userclk_rx_active_in:

标明TX/RX用户时钟网络辅助块产生的时钟处于活动。默认情况下,TX/RX 用户时钟网络辅助器块驱动此端口。

gtwiz_userclk_tx_srcclk_in / gtwiz_userclk_rx_srcclk_in:

输入的源时钟,直接由TXOUTCLK/ RXOUTCLK 驱动。

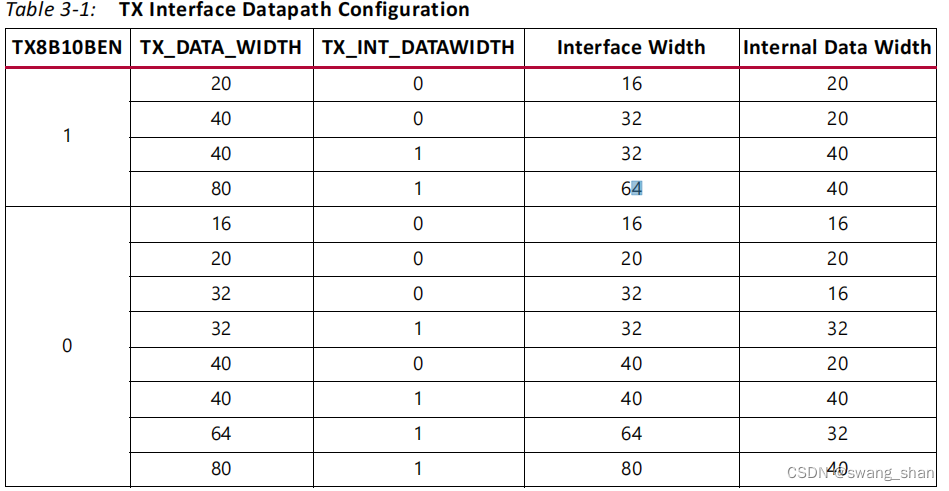

TXUSRCLK and TXUSRCLK2 / RXUSRCLK and RXUSRCLK2:

由gtwiz_userclk_tx_srcclk_in/ gtwiz_userclk_rx_srcclk_in驱动一个/两个BUFG_GT primitive得到。当USRCLK=USRCLK2时,驱动一个primitive,如果USRCLK是USRCLK2的两倍时,驱动两个primitive。USRCLK2给TXDATA/RXDATA提供时钟,USRCLK给内部的PCS logical提供时钟。两个时钟必须positive-edge对齐。 详情见发送机模块。

gtwiz_userclk_tx_reset_in/gtwiz_userclk_rx_reset_in:复位BUFG_GT primitive,高有效。

根据helper block的位置(core/example design),以上字体未加粗的信号的连接和primitive的布线会在core里或者需要启用example design中的时钟模块。

根据helper block的位置(core/example design),以上字体未加粗的信号的连接和primitive的布线会在core里或者需要启用example design中的时钟模块。

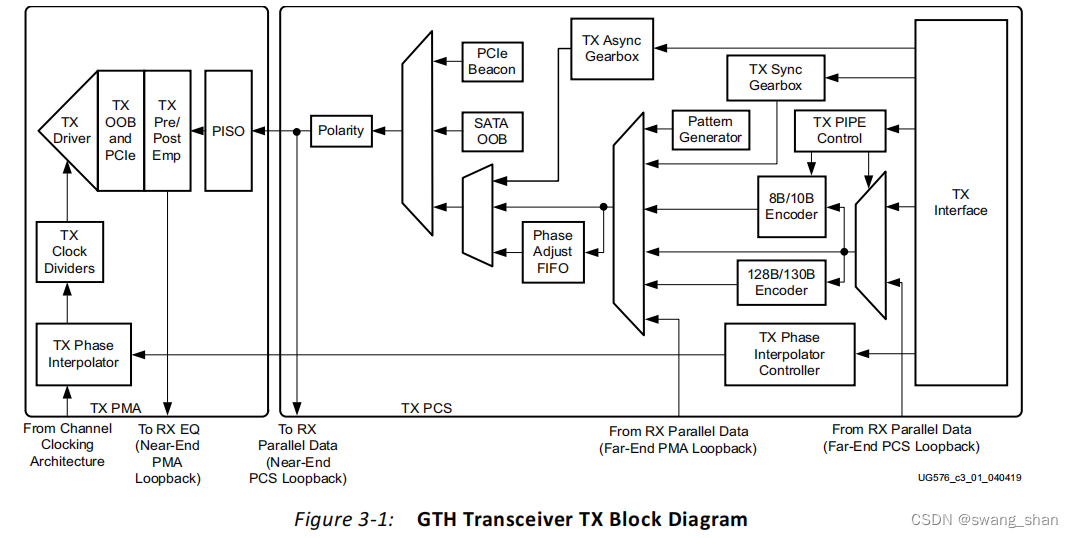

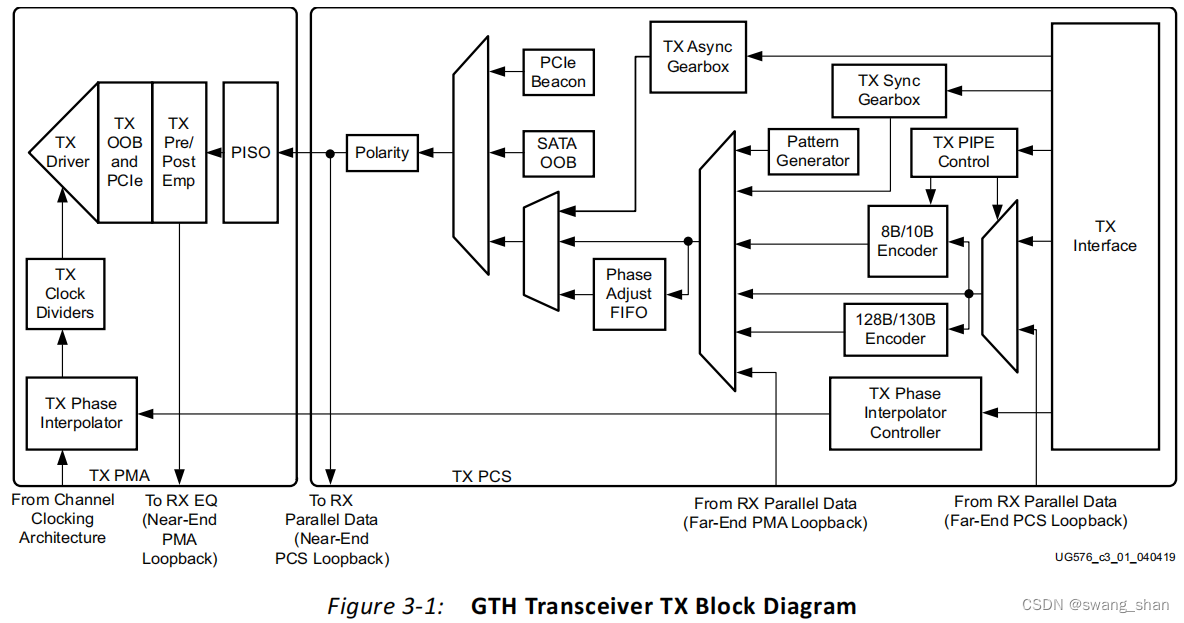

发送机

1、TX接口

每个收发器包括一个独立的发射器,它由一个PCS和一个PMA组成。并行数据从设备逻辑流入TX接口(注意必须与TXUSRCLK2正边缘对齐),通过PCS和PMA后以高速串行数据输出TX驱动程序。详情见图3-1.

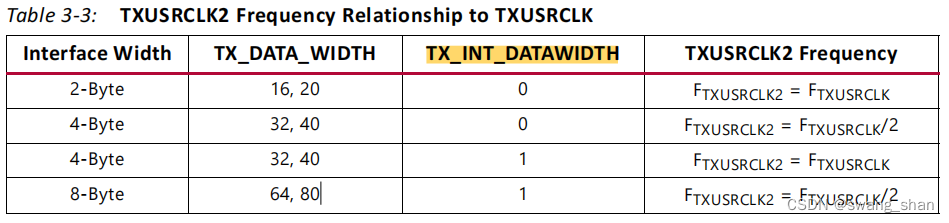

端口的宽度可以配置为2、4或8个字节宽。端口的实际宽度取决于 TX_DATA_WIDTH 和 TX_INT_DATAWIDTH 属性以及 TX8B10BEN 端口设置。端口宽度可以是16、20、32、40、64和80位。表3-1显示了如何选择TX数据路径的接口宽度。

端口的宽度可以配置为2、4或8个字节宽。端口的实际宽度取决于 TX_DATA_WIDTH 和 TX_INT_DATAWIDTH 属性以及 TX8B10BEN 端口设置。端口宽度可以是16、20、32、40、64和80位。表3-1显示了如何选择TX数据路径的接口宽度。

| Attribute | Description |

|---|---|

| TX_DATA_WIDTH | 设置 TXDATA 端口的位宽(interface width)。有效值为16、20、32、40、64和80。 当启用8B/10B编码时,TX_DATA_WIDTH 必须设置为20、40或80。 |

| TX_INT_DATAWIDTH | 控制内部数据路径的宽度(internal data width)。 0:2字节的内部数据路径 1:4字节的内部数据路径。 如果行速率大于8.1875 Gb/s,则设置为1。 |

2、TX 8B/10B编码

GTH收发器有一个内置的 8B/10B TX路径,可以编码TX数据,而不消耗设备资源。启用8B/10B编码器会通过TX路径增加延迟。如果不需要,可以禁用或绕过8B/10B编码器,以最小化延迟。

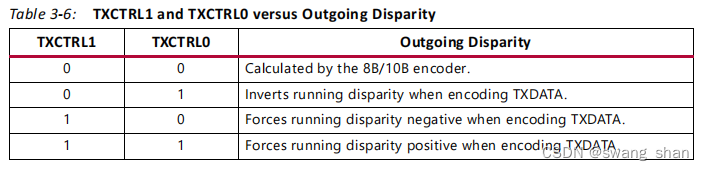

TX 8B/10B 编码端口

| Port | Clock Domain | Description |

|---|---|---|

| tx8b10bbypass_in[7:0] | TXUSRCLK2 | 高有效,一个bit位控制一个字节,允许字节交错的绕过8B/10B。tx8b10ben_in 为高才能使用此模式。 |

| tx8b10ben_in | TXUSRCLK2 | 高有效 |

| txctrl1_in [15:0] | TXUSRCLK2 | 当8B/10B编码旁路时,给TXDATA填充bit。 |

| txctrl0_in [15:0] | TXUSRCLK2 | 当8B/10B编码旁路时,给TXDATA填充bit。 |

| txctrl2_in[7:0] | TXUSRCLK2 | 表示TXDATA上对应的数据字节是有效的K字符。一个bit对应一个byte, 例如:TXCTRL2[0] corresponds to TXDATA[7:0] |

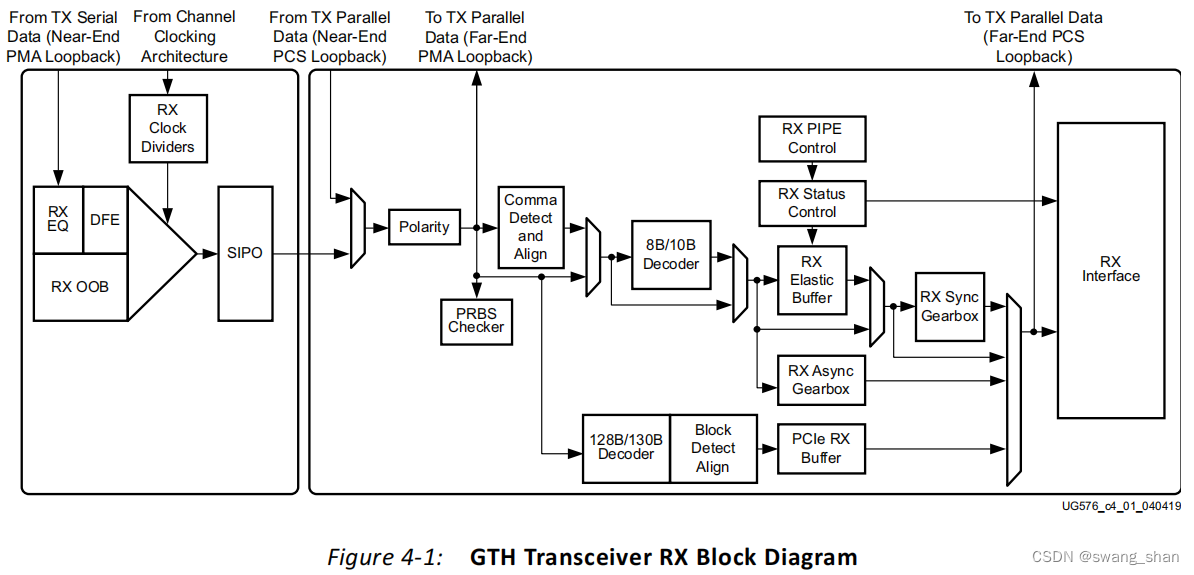

接收机

1、RX 字节和字对齐

接收到的串行数据必须与符号边界对齐,然后才能用作并行数据。运行机制:发射机发送一个可识别的序列,通常称为逗号。接收方在传入数据中查找逗号。当它找到逗号时,它将逗号移动到字节边界,以便接收到的平行字与传输的平行字匹配。下表为常用 K28.5 。

| Special Code Name | Bits HGF EDCBA | Current RD- abcdei fghj | Current RD + abcdei fghj |

|---|---|---|---|

| K28.5 | 101 11100 | 001111 1010 | 110000 0101 |

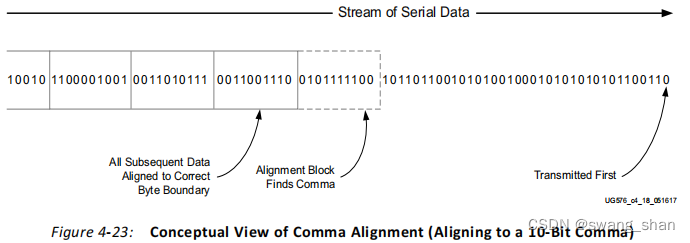

图4-23显示一个10-bit 逗号的对齐方式。右侧为接收未对齐位的bits。中间虚线框显示为带有逗号的串行数据。左侧为字节对齐的RX并行数据。

图4-24显示左侧TX并行数据,右侧逗号对齐后接收可识别的并行数据。

1、启用 Comma 对齐

| Port | Clock Domain | Description |

|---|---|---|

| rxcommadeten_in | TXUSRCLK2 | 高有效,表示启用comma对齐模块。 启用会加大RX数据路径延迟 |

2、配置comma图形

| Attribute | Type | Description |

|---|---|---|

| ALIGN_COMMA_ENABLE | 10-bit Binary | 设置MCOMMA/PCOMMA中哪些位必须与传入的数据相匹配,哪些位可以忽略。 此属性是一个10位掩码,默认值为11111111111。 |

| ALIGN_MCOMMA_VALUE | 10-bit Binary | 定义 mius comma ,接待顺序是从右到左的(首先收到ALIGN_MCOMMA_VALUE[0])。 默认值为10‘b1010000011(K28.5 与附录相反)。此定义不影响8B/10B的编解码。 |

| ALIGN_PCOMMA_VALUE | 10-bit Binary | 定义plus comma,接待顺序是从右到左的(首先收到ALIGN_PCOMMA_VALUE[0])。 默认值为10’b0101111100 (K28.5 与附录相反)。此定义不影响8B/10B的编解码。 |

| ALIGN_COMMA_DOUBLE | Boolean | 为高时表明同时启用PCOMMA和MCOMMA。 |

上表为需要的信号。下图为在 IP核中配置的位置:

ALIGN_COMMA_ENABLE 与 COMMA 的匹配实现如下图 4-25。

当 ALIGN_COMMA_DOUBLE 为 1 时,PCOMMA 和 MCOMMA 的组合顺序为下图 4-26。

3、启动 COMMA 对齐

| Port | Clock Domain | Description |

|---|---|---|

| rxmcommaalignen_in | TXUSRCLK2 | 当要对齐MCOMMA时,拉高 |

| rxpcommaalignen_in | TXUSRCLK2 | 当要对齐PCOMMA时,拉高 |

4、对齐状态信号(了解)

| Port | Clock Domain | Description |

|---|---|---|

| rxbyteisaligened_out | TXUSRCLK2 | 为高标志着根据COMMA检测,并行数据流在字节边界正确对齐 |

| rxbytealign_out | TXUSRCLK2 | 为高表示包含串行数据流的字节对齐由于COMMA检测已经发生变化 |

| rxcommadet_out | TXUSRCLK2 | 当检测到COMMA时拉高。在RX接口COMMA可用之前,断言会进行几个时钟周期 |

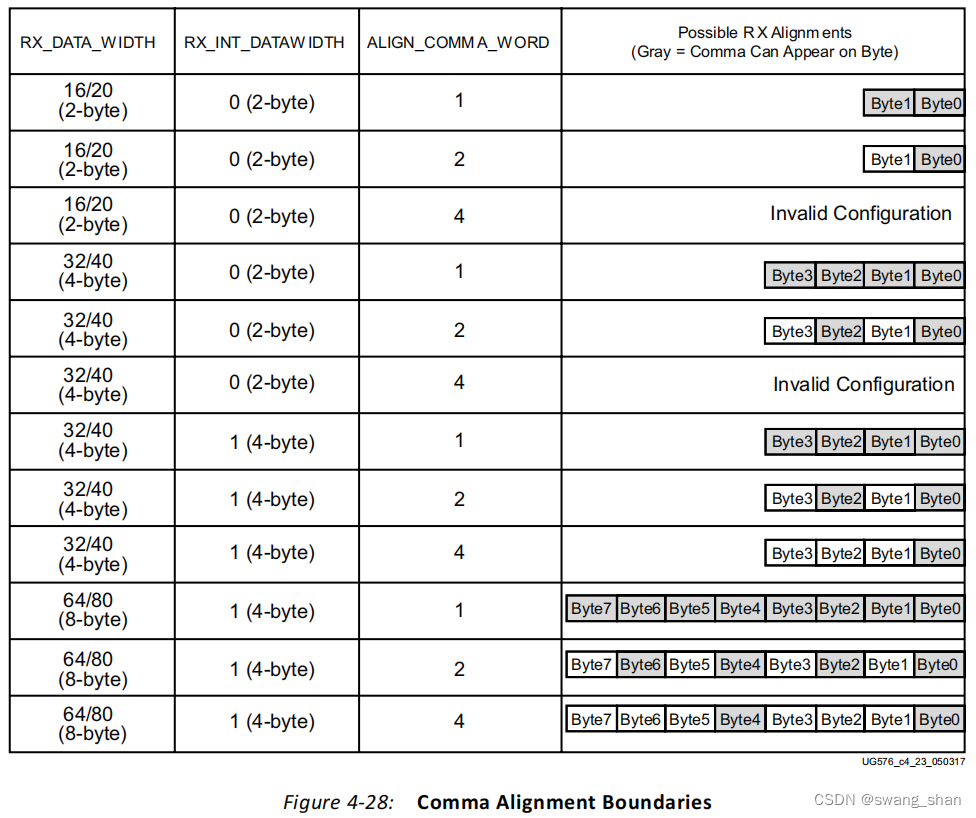

5、对齐边界

允许的对齐边界由ALIGN_COMMA_WORD和RX_INT_DATAWIDTH定义。

| Attribute | Type | Description |

|---|---|---|

| ALIGN_COMMA_WORD | Integer | 此属性控制在多字节数据路径检测到的commas的对齐方式。 1: 可以实现TXDATA输出的奇数字节或偶数字节comma对齐。 ??????2字节接口,对齐全部2字节 ??????4字节接口,对齐全部4字节; ?????? 8字节接口,对齐全部8字节 2: 仅对奇数字节对齐comma。 ??????2字节接口,对齐RXDATA[9:0]; ??????4字节接口,对齐RXDATA[9:0]/ RXDATA[29:20]; ?? ???8字节接口,RXDATA[9:0]/ RXDATA[29:20]/RX[49:40]/RX[69:60];; 4: 在4字节边界进行对齐,在RX_INT_DATAWIDTH = 0时禁用。 ??????4字节接口,对齐RXDATA[9:0]=8字节接口,对齐RXDATA[9:0]/ RX[49:40] |

2. 8B/10B 解码器

1、8B/10B位和字节排序

B/10B解码要求首先接收位a0,但GTH收发器总是首先接收最右边的位。因此,8B/10B解码器在解码之前自动反转接收到的数据的位序。解码后,将这些数据提供给RXDATA端口。

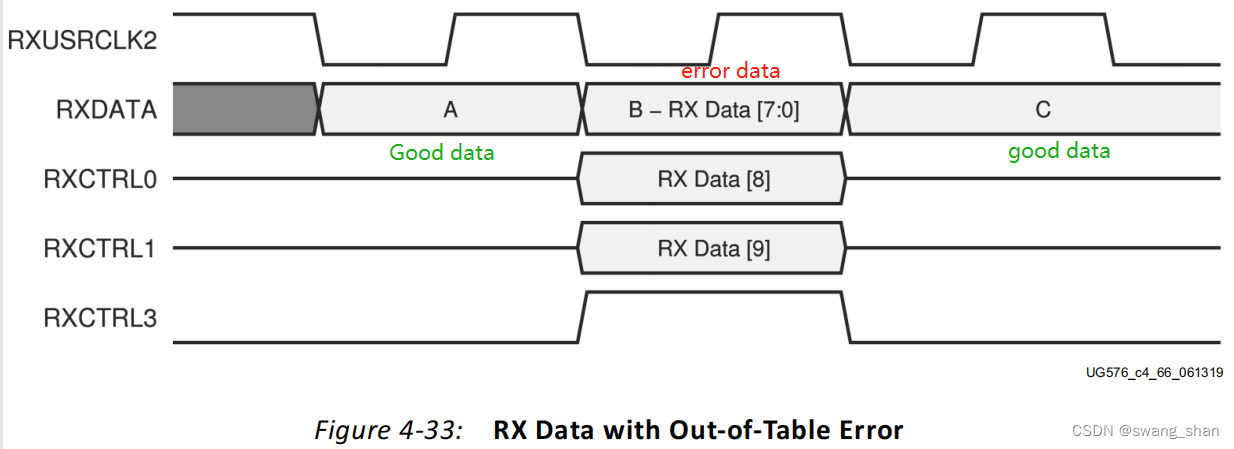

2、解码错误检测

解码器提供差异检查和表外错误检测。

差异检查:当RXDATA的数据字节到达有错误,RXCTRL1拉高。具体实现如图4-32.

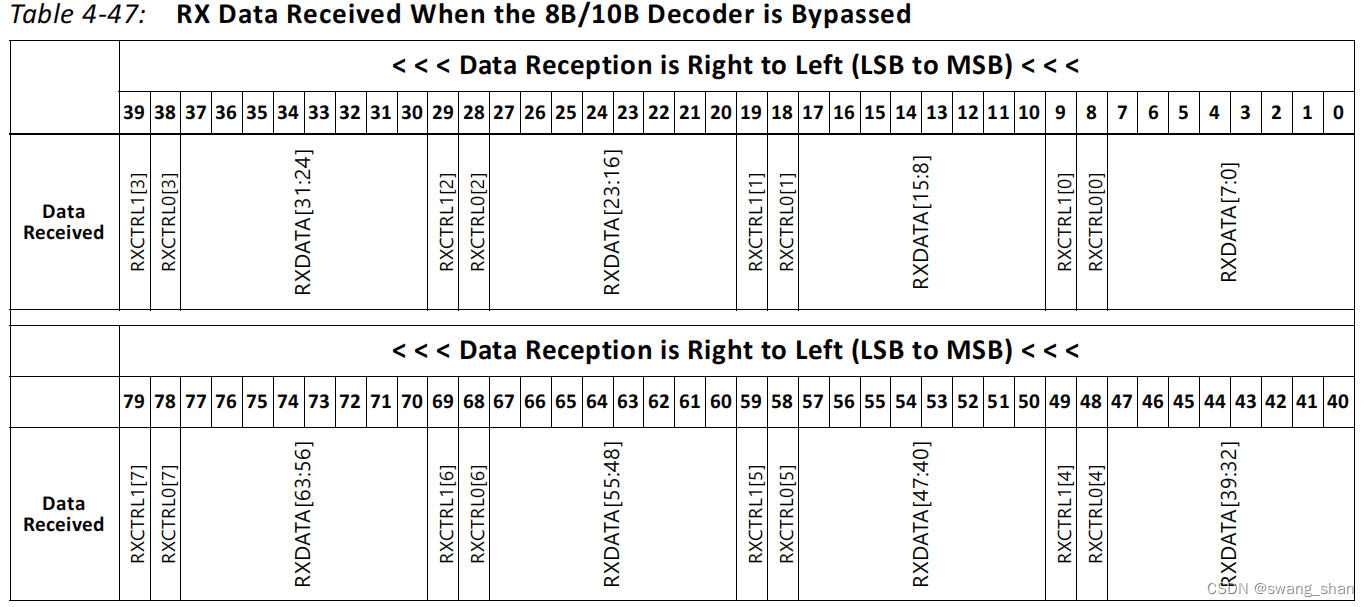

表外错误检测:当RXCTRL3启用,但接收到的10位字符无法映射到有效8B/10B字符时,驱动RXCTRL3为高。发生这种情况时,未解码的10位字符通过以下格式的RX数据接口从解码器输出:

?对应的RXCTRL1表示第9位

?对应的RXCTRL0表示第8位

?相应的RXDATA字节表示[7:0]位

?相应的RXCTRL3表示发生了无效的8B/10B字符错误

3、特殊字符

8B/10B解码包括常用于控制功能的特殊字符(K码)。当RXDATA为K字符时,解码器驱动RXCTRL0 High。

如果DEC_PCOMMA_DETECT设置为TRUE,当RXDATA是 plus comma,解码器就会驱动相应的RXCTRL2为高。

如果DEC_MCOMMA_DETECT设置为TRUE,当RXDATA为minus comma,解码器驱动相应的RXCTRL2为高。

RXCTRL2的bit位与RXDATA的byte一一对应。

RXCTRL2[7]对应RXDATA[63:56]

RXCTRL2[6]对应RXDATA[55:48]

RXCTRL2[5]对应RXDATA[47:40]

RXCTRL2[4]对应RXDATA[39:32]

RXCTRL2[3]对应RXDATA[31:24]

RXCTRL2[2]对应RXDATA[23:16]

RXCTRL2[1]对应RXDATA[15:8]

RXCTRL2[0]对应RXDATA[7:0]

4、启用和禁用8B/10B解码

rx8b10ben_in控制启动8B/10B解码器的启用与否。

5、端口及属性

| Port | Clock Domain | Description |

|---|---|---|

| rx8b10ben_in | TXUSRCLK2 | 高表示启动8B/10B解码器。 低表示接收到的10-bit数据显示为 { RXCTRL1, RXCTRL0, RXDATA[7:0] }。 |

| RXCTRL2[7:0] | TXUSRCLK2 | 为高表示在RXDATA上显示的相应字节是一个COMMA。 |

| RXCTRL0[15:0] | TXUSRCLK2 | RXCTRL0[15:8]未使用。 1.解码器被绕过或RXCTRL3为高,为非解码数据的第8位。请参见表4-47。 2.启用解码器,高表示RXDATA的对应字节为K码。例:RXCTRL0[0] 对应RXDATA[7:0] |

| RXCTRL1[15:0] | TXUSRCLK2 | RXCTRL1[15:8]未使用。 1.解码器被绕过或RXCTRL3为高,为非解码数据的第9位。请参见表4-47。 2.启用解码器,高表示RXDATA的对应字节有差异错误。例:RXCTRL1[0] 对应RXDATA[7:0] |

| RXCTRL3[7:0] | TXUSRCLK2 | 高表示在RXDATA上显示的相应字节不是8B/10B表中的有效字符。例:RXCTRL3[0] 对应RXDATA[7:0] |

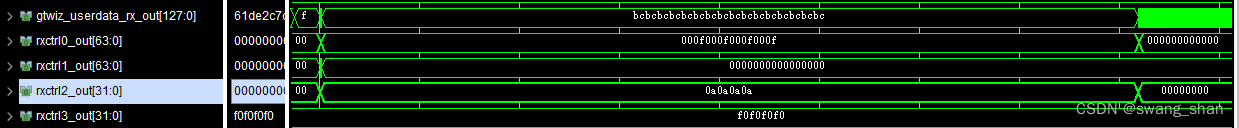

仿真图如下,RXCTRL2 = a,有人能解释一 下吗?

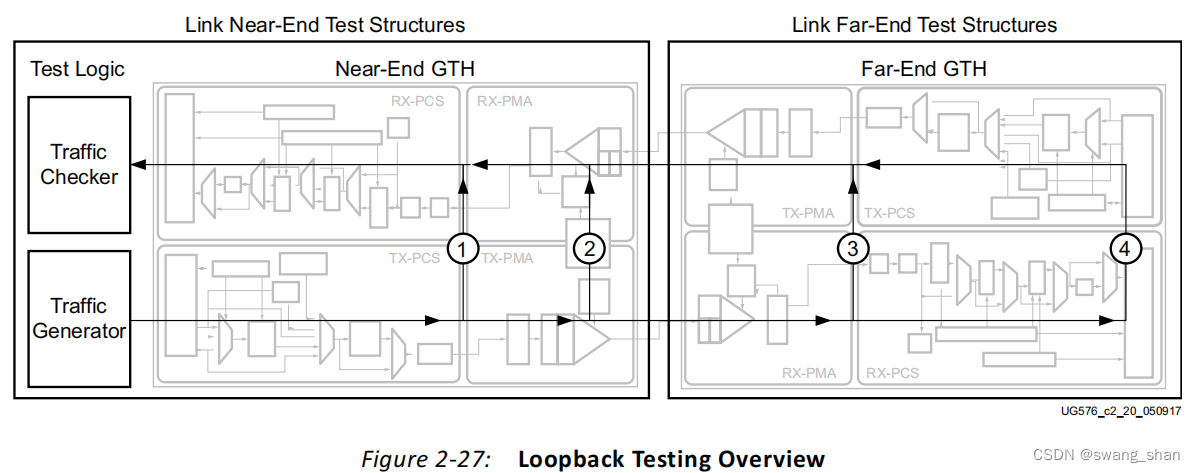

自环

| Port | Clock Domain | Description |

|---|---|---|

| LOOPBACK[2:0] | Async | 000: Normal operation 001: Near-end PCS Loopback 010: Near-end PMA Loopback 100: Far-end PMA Loopback 110: Far-end PCS Loopback |

持续补充ing