- 关于RAM IP的延迟:[1]

- 选择了output registers;可以在RAM输出端口添加register,也可以在core的输出添加。

?

在primitives添加:降低clock-to-out到primitive的延迟

在core添加register:改善clock-to-out到Block Memory Generator core的延迟。

没添加一个register read操作都要加一个时钟周期。

但是添加primitives不会占用fpga多余的资源,图中显示在两处均添加了register,当读地址进来之后会数据经过三排之后输出。

- 可选的pipeline stages

可以在muc处增加pipeline增加core的性能。最多可以增加三级流水,不包括core输出的寄存器。具体几级流水由组成的RAM有几个决定。(IP自动插入)

- Memory的输出流控

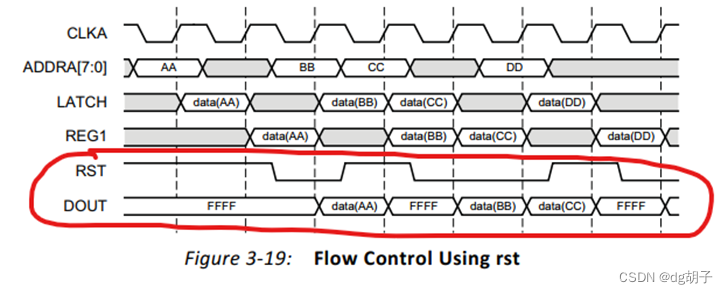

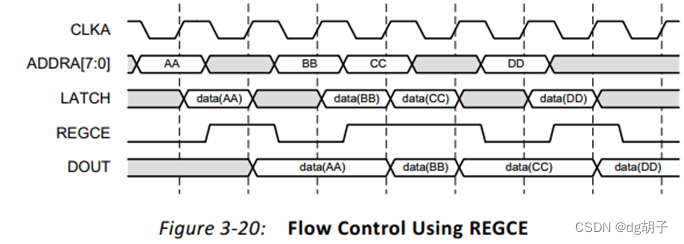

对于enable(en),reset(rts),register enable(REGCE) 三个pin不同的组合输出会有不同。

Reset:当复位拉起时,port输出在gui中定义的复位值。

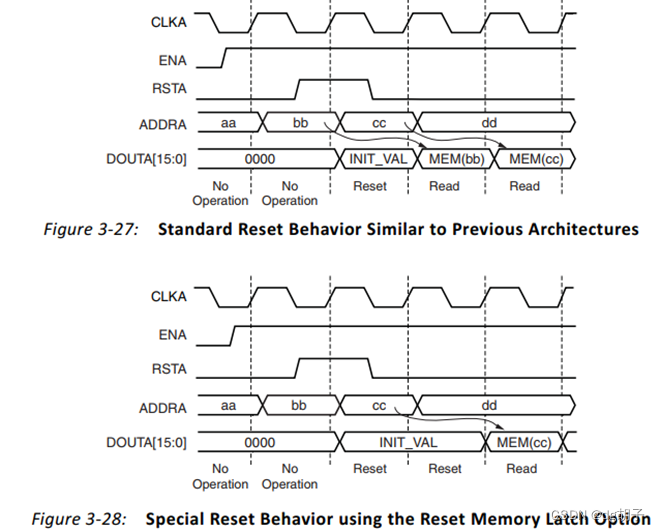

特殊的复位行为:Page60,当没有core output register复位作用域primitives register。但是当你选择复位memory latch以及primitives register时,复位信号会延后两个时钟周期才释放。复位最小要保持一个周期才有效。复位结果作用于最后的out register,立马相应的。

?

?

REGCE能够latch数据。

?

正常情况下没有core output register latch数据==输出数据,没有延迟。

IP两种复位方式,rsta/rstb(set/reset)控制最后一个output register,如果没有勾选core output register那么控制数据的memory latches.

?

Set/reset复位行为不同于reset priroty行为。

Reset priority: reset优先级可以选择是SR(set reset)或CE(clock enable)优先,默认是CE。即CE优先级>reset.

?

?

真实的仿真情况。符合图示,图中3-27实际中地址到输出会经过两拍(有primitive output register),若复位保持一个clock,那么不会影响后续的值继续输出,我的初始数据为1010。但是在图3-28中复位是复位的latch,latch直接连接dout,所以会把当前的值覆盖掉,并延续一拍,相当于是en信号不使能的情况。

?

[1] Pg058 Page-30