Makefile

前言

1.编译并运行一个程序

- Windows:点击build and run按钮自动编译运行。由于自动挡汽车一样,一切都是自动化的。

- Linux:通过

GCC编译器编译。犹如开手动挡的汽车一样。

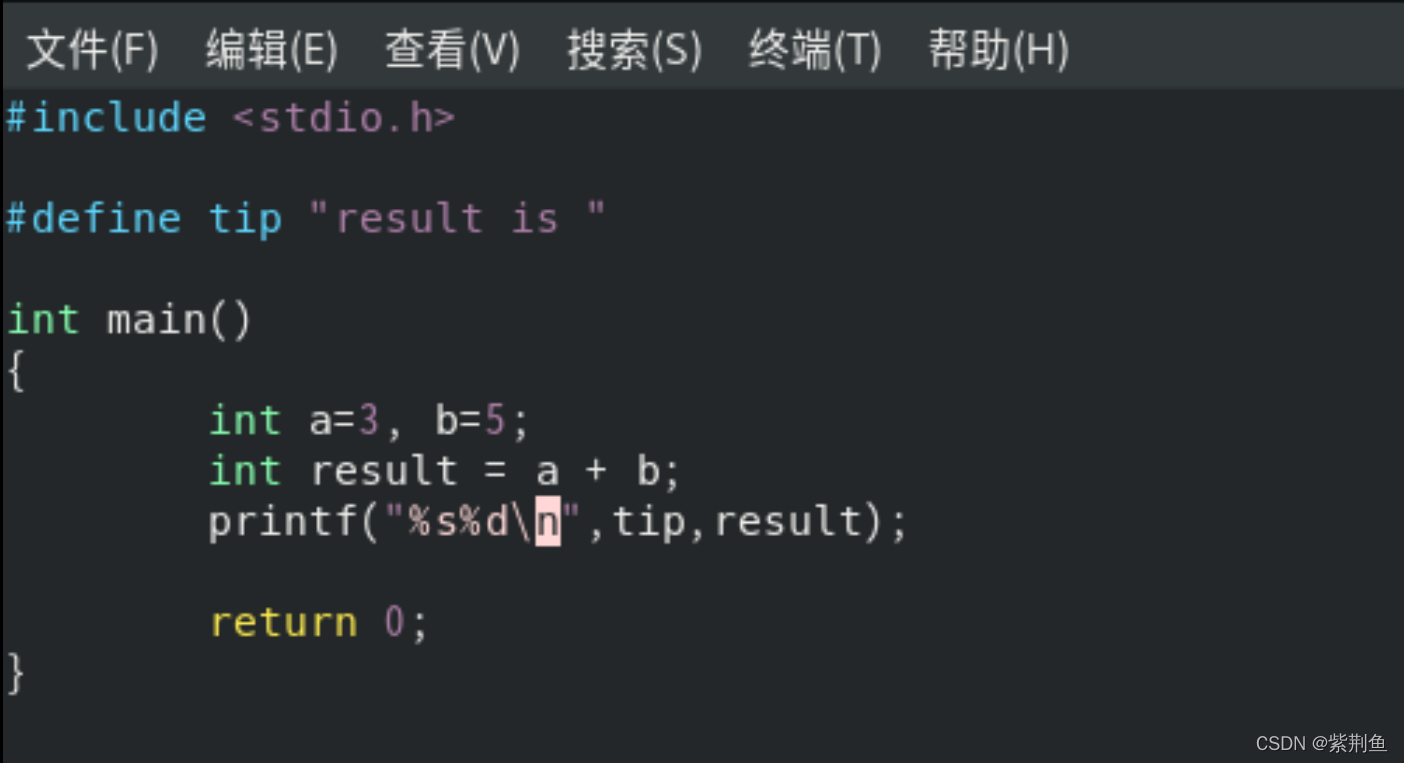

如上图程序,我们通过GCC编译指令,如下,就可以编译运行该程序。

//通过该指令得到可执行文件add

gcc -o add add.c

//运行该程序

./add

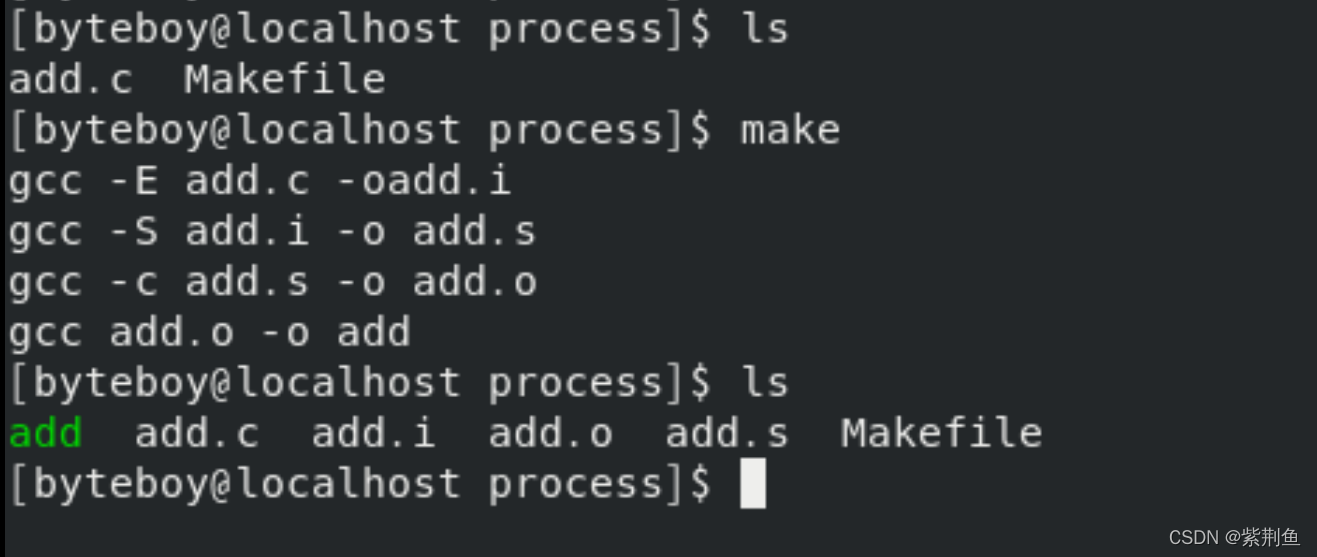

2.编译过程简介

编译过程:

- 第一步:预编译

指令:gcc -E add.c -o add.i - 第二步:汇编

指令:gcc -S add.i -o add.s - 第三步:编译

指令:gcc -c add.s -o add.o - 第四步:链接

指令:gcc add.o -o add

3.📑规则一:显示规则

写一个简单地Makefile

语法:

目标文件:依赖文件

[ Tab ] 指令

例子: 以上述编译过程为例

add:add.o

gcc add.o -o add

add.o:add.s

gcc -c add.s -o add.o

add.s:add.i

gcc -S add.i -o add.s

add.i:add.c

gcc -E add.c -oadd.i

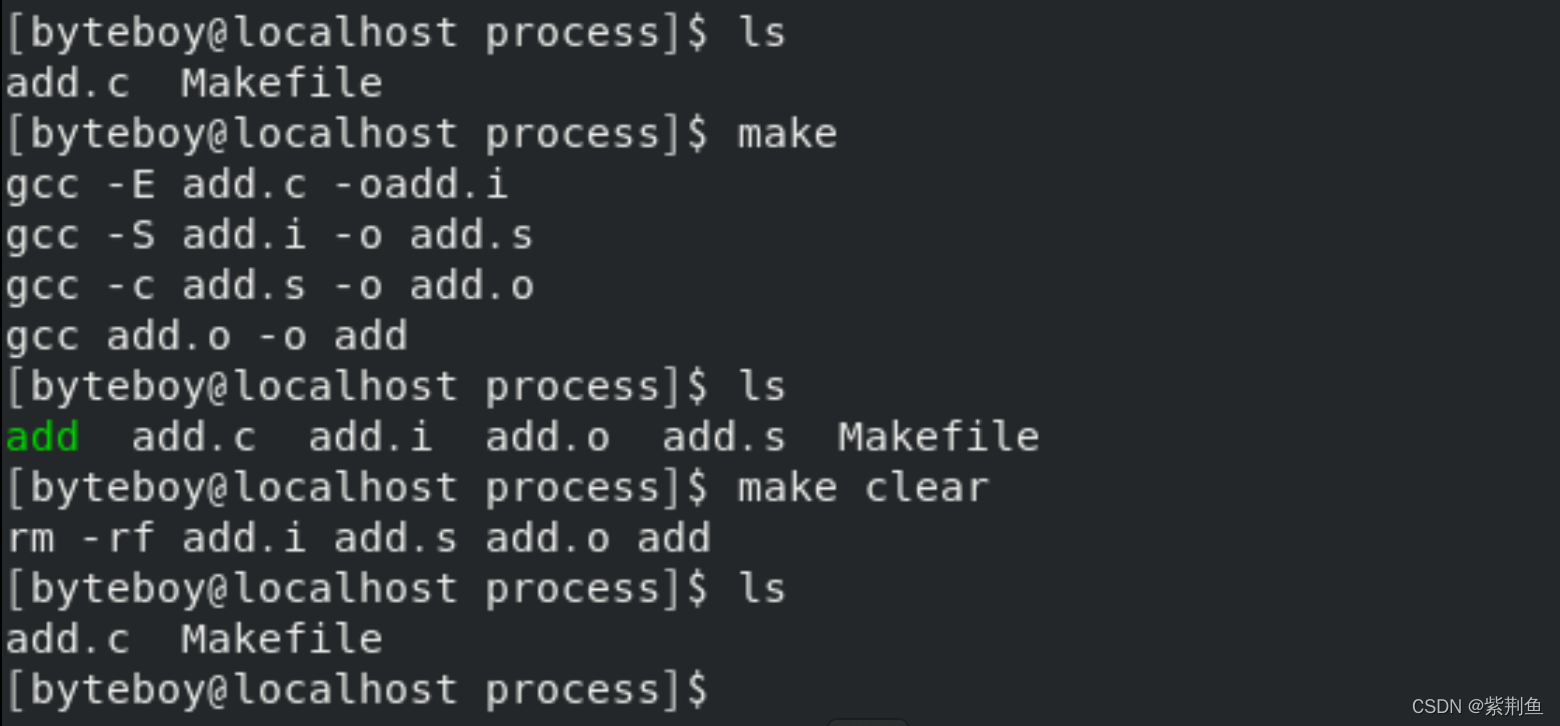

在Makefile文件中我们也已添加一些非编译的指令,他的目的只是“do something” ,不参加编译过程。我们称这段指令为伪目标。用.PHONY:指代,例如:删除编译产生的文件

.PHONY:

clear:

rm -rf add.i add.s add.o add

4.📑规则二:变量替换

例子2:

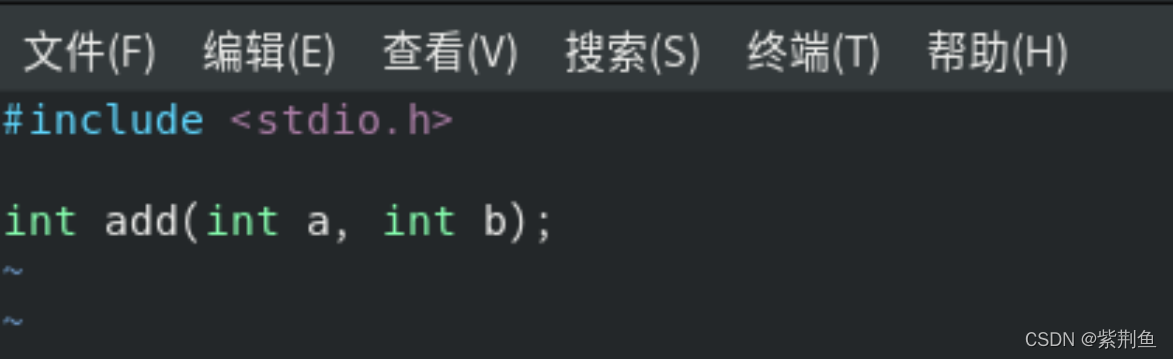

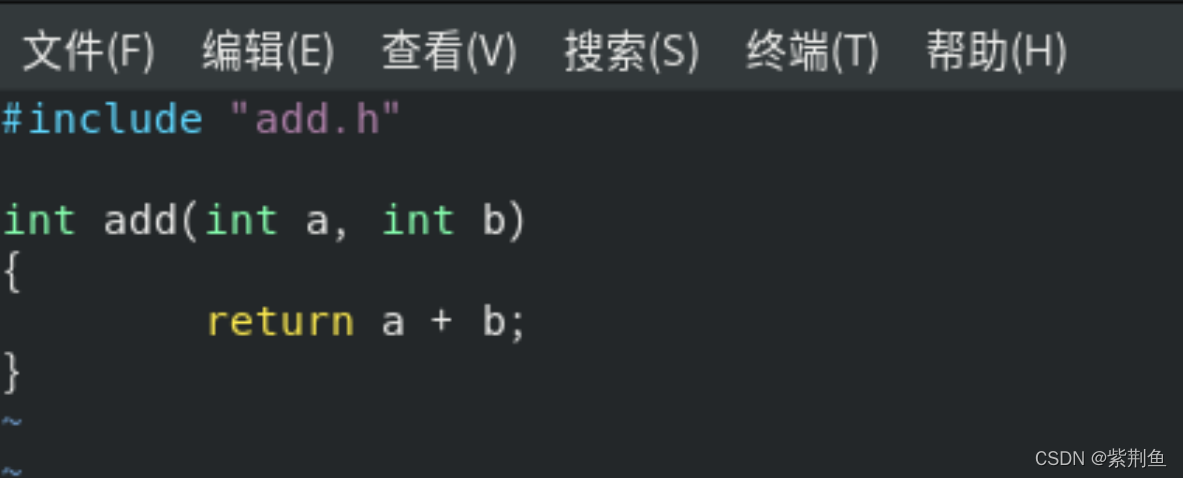

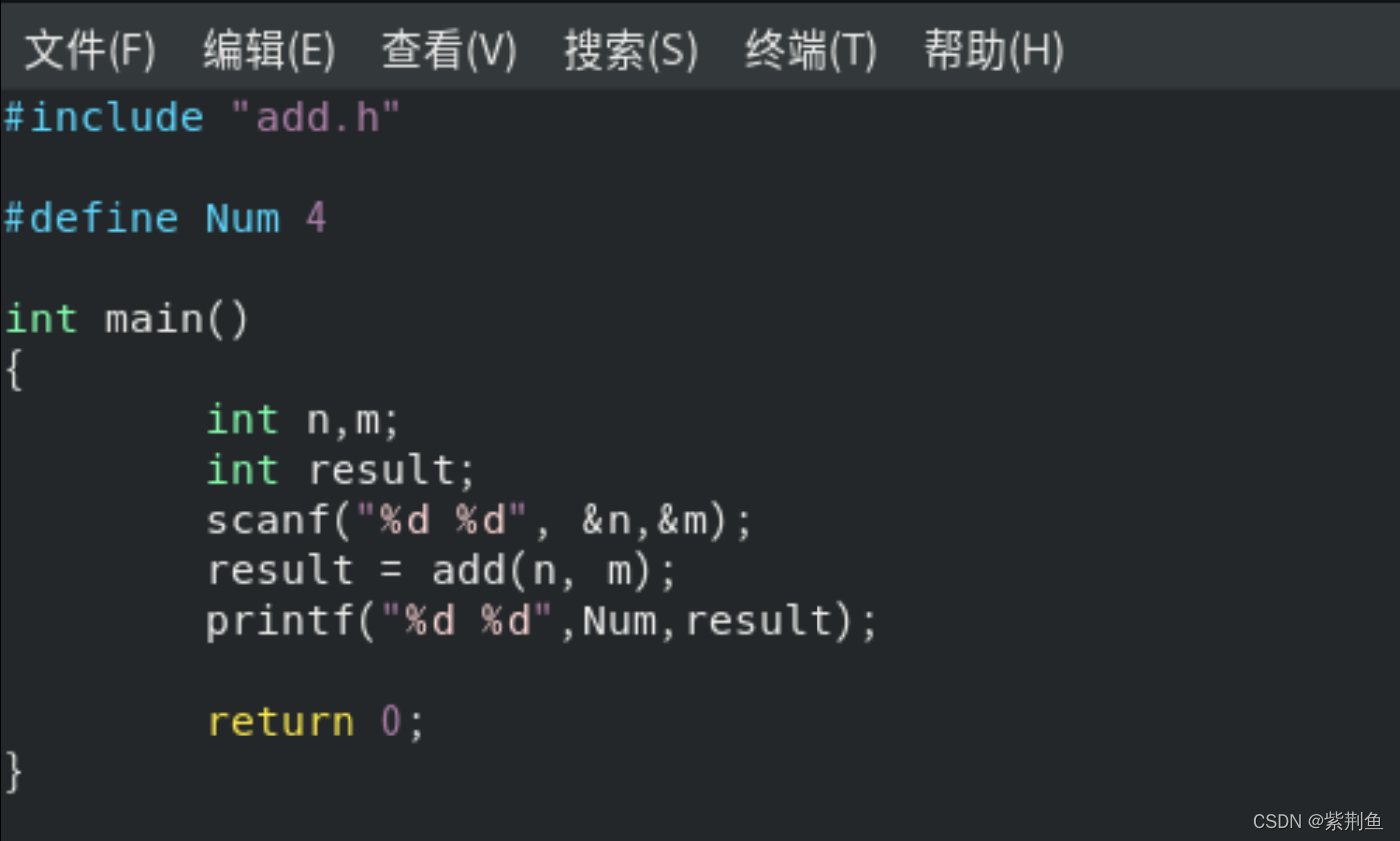

add.h

add.c

main.c

利用显示规则编写Makefile如下:

app:main.o add.o

gcc -o app main.o add.o

main.o:main.c add.h

gcc -c main.c

add.o:add.c add.h

gcc -c add.c

变量替换语法:

= (替换)

+= (追加)

:= (恒等于)

$(使用)

改写上述Makefile:

TAR = app

OBJ = main.o add.o

CC = gcc

$(TAR):$(OBJ)

$(CC) -o $(TAR) $(OBJ)

main.o:main.c add.h

$(CC) -c main.c

add.o:add.c add.h

$(CC) -c add.c

5.📑规则三:隐含规则

语法:

%.x :任意的.x文件,.x为某文件后缀名

*.x : 所有的.x文件,x为某文件后缀名

TAR = app

OBJ = main.o add.o

CC = gcc

$(TAR):$(OBJ)

$(CC) -o $(TAR) $(OBJ)

%o:%.c %.h

$(CC) -c %.c

6.📑规则四:通配符规则

语法:

$@ : 所有的目标文件

$^:所有的依赖文件

$< : 所有的依赖文件的第一个

TAR = app

OBJ = main.o add.o

CC = gcc

$(TAR):$(OBJ)

$(CC) $^ -o $@

%o:%.c %.h

$(CC) -c $^ -o $@

感谢您的阅读,如有帮助送小编一个三连,十分感谢