1. ʲô��MMU?

MMU��Memory Management Unit����д,��������Ϊ�ڴ������Ԫ��MMU�Ǹ�������(CPU)���ڴ��������ļ����Ӳ��,�书�ܰ��������ַ��������ַ��ת��(�������ڴ����)���ڴ汣��������cache�Ŀ��Ƶȡ�

MMU��һ��������������ص�Ӳ������,Ҳ������linux������MMU�ڴ������Ԫ����ϵͳ�ں˻��Ƶ����֮һ�����������û��MMU,CPU�ڲ�ִ�е�Ԫ�������ڴ��ַ�źŽ�ֱ��ͨ����ַ���߷��͵�оƬ����,���ڴ�оƬ����,�����������ַ(physical address),���PA��Ӣ��physical���������ĽӴ�,����PA�������ڴ�оƬphysically connected�������ϵ��źš�

���MMU����������,CPUִ�е�Ԫ�����ĵ�ַ�ź��ڷ��͵��ڴ�оƬ֮ǰ����MMU�ػ�,�����ַ�źų�Ϊ�����ַ(virtual address),���VA,MMU�Ḻ���VA�������һ����ַ,Ȼ���ڴ�оƬ��ַ������,��VAӳ���PA��

2. PowerPC E500 MMU

PowerPC(Performance Optimization With Enhanced RISC �C Performance Computing,��ʱ���PPC)��һ������ָ�(RISC)�ܹ������봦����(CPU),����������Դ��IBM(�������û�����˾)��POWER(Performance Optimized With Enhanced RISC)��

PowerPCоƬƾ�����ɫ�����ܺ߶����Ϻͼ����Ƚ�����������ͨ��Ӧ��,��ҵ����Ӧ��,�������ֻ�,����洢����,��������,����ϵͳ���Ƶȶ����зdz��㷺��Ӧ�á�

PowerPC��E500�Ƿ�˼����(FreeScale)����Power Architecture��32λ���������ġ�E500ϵ�к����������汾,��E500v1,E500v2��E500mc��64λ�汾��E500mc�ݱ�ΪE5500����,����2010���Ƴ���

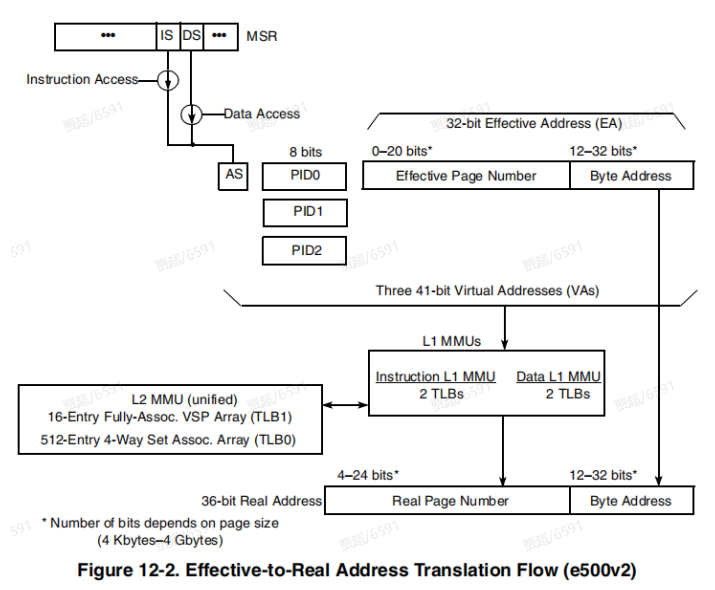

PowerPC E500 ����(���ơ�E500��)�����������ڴ������Ԫ(MMU)��ϵ�ṹ��L1-MMU��L2-MMUΪ�ýṹ�е�����Ӳ����Ԫ��E500ͨ��L1-MMU��L2-MMU,�Լ�һЩ�����Ĵ�����ָ����ʵ����ʵ��ַ��ת����E500v1�����ǰ�32λ��Ч��ַת��Ϊ32λ������ַ(ʹ��41λ��ʱ�����ַ);E500v2�����ǰ�32λ��Ч��ַת��Ϊ36λ������ַ��

L1-MMU����:

1. ����4��Ŀ��ȫ����TLB����(һ������ָ�����,һ���������ݷ���֧��9��(E500v1)��11��(E500v2)ҳ���С,��I-L1VSP��D-L1VSP

2. ����64 entry, 4·set-associative TLB����(һ������ָ�����,һ���������ݷ���),��֧��4kbyteҳ��,��I-L1TLB4K��D-L1TLB4K��

3. L1 MMU������L1�������(��ַת��/L1����)���з��ʿ�����ȫ��ˮ��,����ÿ��ʱ�Ӷ��������һ������/�洢��

4. ִ��L1 TLB���ҵ�ָ����������ݷ����Dz��еġ�

5. ����L1 TLB��Ŀ����פ����L2 MMU�е�TLB��Ŀ��һ���ʵ��Ӽ���

6. �Զ�ִ��ʧЧ����,�Ա���L2 TLB��һ���ԡ�

L2-MMU����:

1. 16����Ŀ,��ȫ������ͳһ��L2 TLB����(����ָ������ݷ���)TLB1֧��9��(E500v1)��11��(E500v2)ҳ���С,��TLB1,���ڶ�ʽӳ�䡣

2. 256����2-way (E500v1)��512-entry 4-way (E500v2)������ͳһL2 TLB array (TLB0)��֧��4kbyte��ҳ��,��TLB0,���ڽ���ҳʽӳ�䡣

3.�� TLB miss�쳣��֧�֡�

4. TLB1��TLB0��tlbre, tlbwe, tlbsx, tlbsync, tlbivax��mtsprָ����й�����

5. ִ���ɵ�ǰ����tlbivaxָ�������TLB1��TLB0ʧЧ��֧��TLB1��TLB0����������ִ�е�tlbivaxָ��µ�ʧЧ������

6. TLB1��ʵ�ֵ�IPROTλ��ֹ����Ч,�Ӷ������ؼ�����(ͨ������IPROTλ��ָ��)����ʧЧ��

2.1 Effective-to-Real Address Translation����

Effective-to-Real Address Translation(�����ַ��������ַ�ķ���)����������ʾ:

��ΪE500��Сҳ�Ĵ�С��4 Kbytes,���Ե�12λͨ��������4Kҳ�ڵ��������Ҳ���Ҫ���з��롣���ȼ��L1 MMU(ָ�������)�Ƿ����е�ַ���롣���û��,��������ת����(ָ�������)L2 MMU�н��д�����

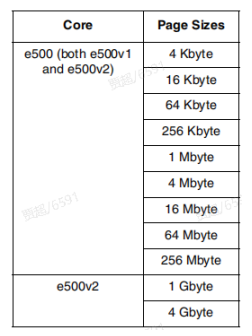

E500v1���ĺ�E500v2����֧�ֵ�ҳ��С�ɼ��±�,E500v2���ı�E500v1���Ķ�֧����1Gbyte��4Gbyteҳ�Ĵ�С��

2.2 MMU entry�ֶ�

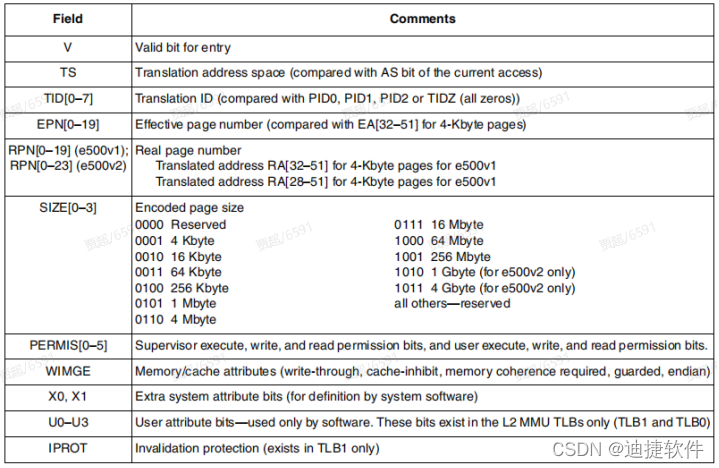

��TLB��,���ݶ��ǰ��д�ŵ�,һ�г�֮Ϊһ��entry��һ��entry����������bitλ������MMU entry��bitλ��������:

V:������ʾ��ǰentry�Ƿ���Ч��Ϊ0ʱ��ʾ��Ч,Ϊ1ʱ��ʾ��Ч����ϵͳreset֮��,����entry��Vλ����Ϊ0��

TS:�����ַ�ռ��е�AS��Ϊ0��ʾ��ַ�ռ�0,Ϊ1��ʾ��ַ�ռ�1��

TID[0:7]:�����ַ�ռ��е�PID��TIDΪ0ʱ,����PID�ıȽϡ���Linux��,ȫΪ0��

EPN[0:19]:����ҳ��š�����ҳ��С��ͬ,��Ч��λ��ҳ��ͬ��

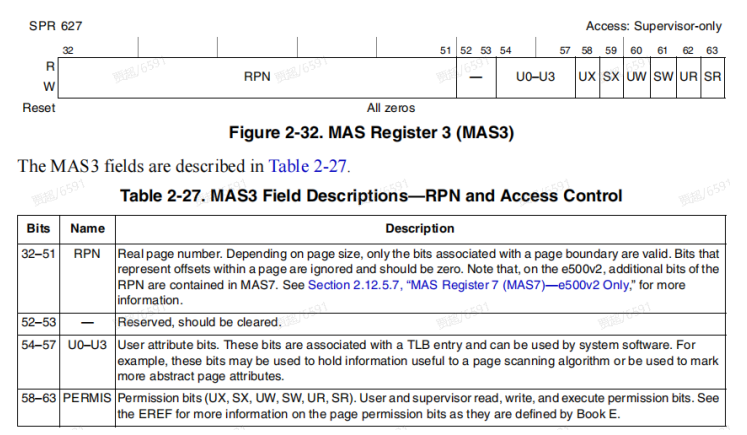

RPN[0:19]:����ҳ��š�

SIZE[0:3]:��ʾ��ǰentry��ҳ��С��

PERMIS[0:5]:����������ǰentry�ķ��ʿ���λ���ֱ���UR,SR,UW,SW,UX,SX���ֱ��ʾ�û�̬���ں�̬�Ķ�/д/ִ��Ȩ�ޡ�

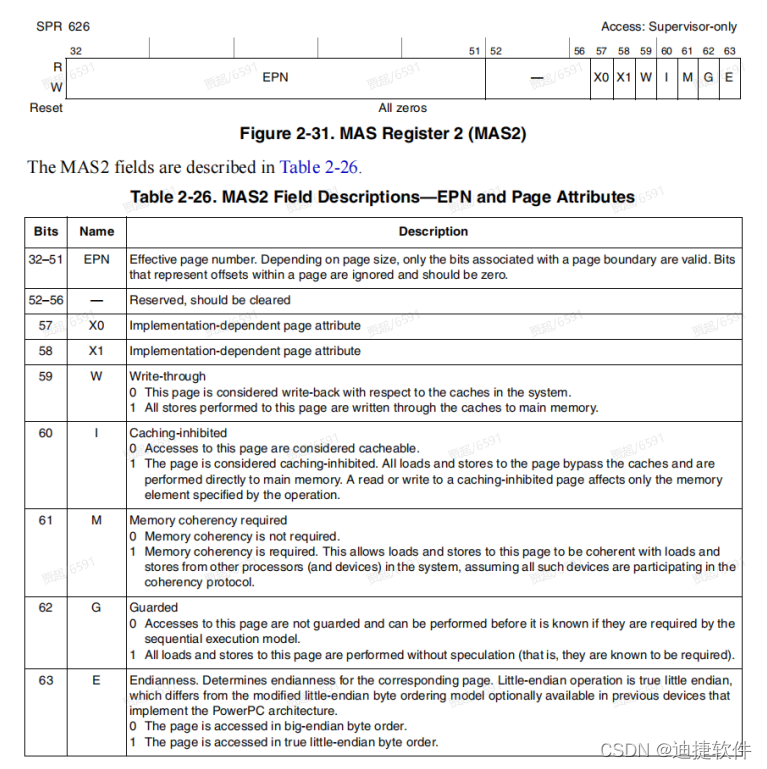

WIMGE[0:4]:W��ʾ��ǰentry��write through����write back��I��ʾ��ǰentry�Ƿ����Cache��M��ʾ�Դ��������ķ�����Ҫ���д洢һ���Դ�����G��ʾ����Ӧ�洢��������б�����E��ʾ��ǰentry��С�˻��Ǵ�ˡ�

X0,X1:����һЩ�������ԡ�

U[0:3]:�Զ�����;��

IPROT:��IPROTΪ1ʱ,��ʾ��ǰentry������������ʹ��tlbivaxָ����Ч��entry��ֻ����tlbweָ���������E500��ֻ��TLB1֧�ָ�λ,��TLB0��,��λһֱΪ0��

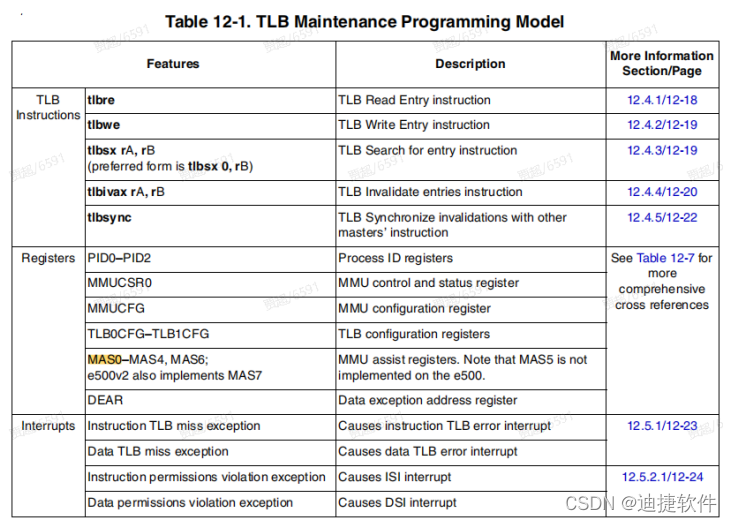

TLB���ָ��Ĵ������쳣���±���ʾ:

2.3 MMU��ؼĴ���

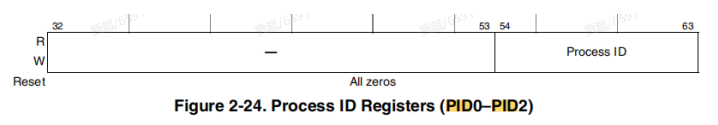

PID0-2�Ĵ���:���ڱ��浱ǰ���̵�PID,�üĴ���ֻ��54-63λ��Ч��

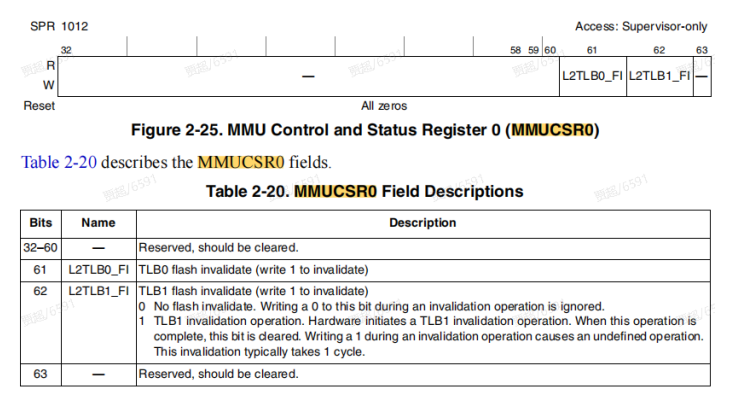

MMUCSR0�Ĵ���:����ʹTLB0��TLB1������entry��Ч���üĴ���L2TLB0_FIλʹ��ЧTLB0������entry;L2TLB1_FIλʹ��ЧTLB1������entry��

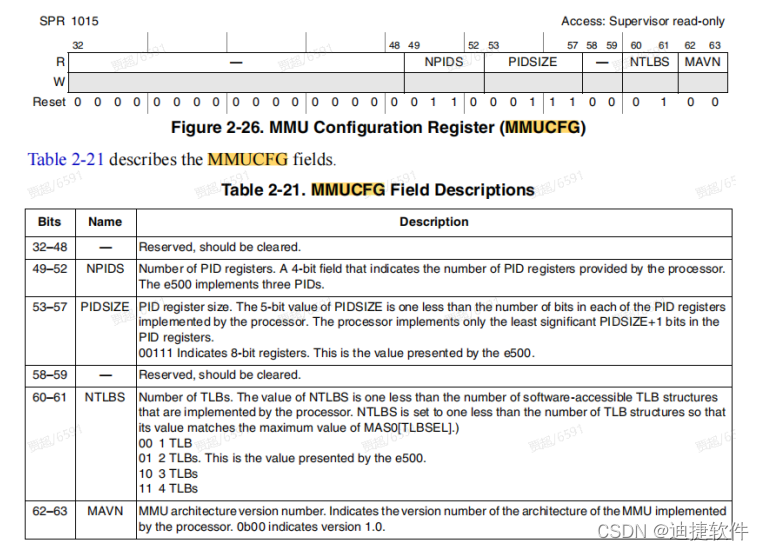

MMUCFG�Ĵ���:�������浱ǰMMU��������Ϣ,����PID�Ĵ�������,��С,TLB�������ȡ�

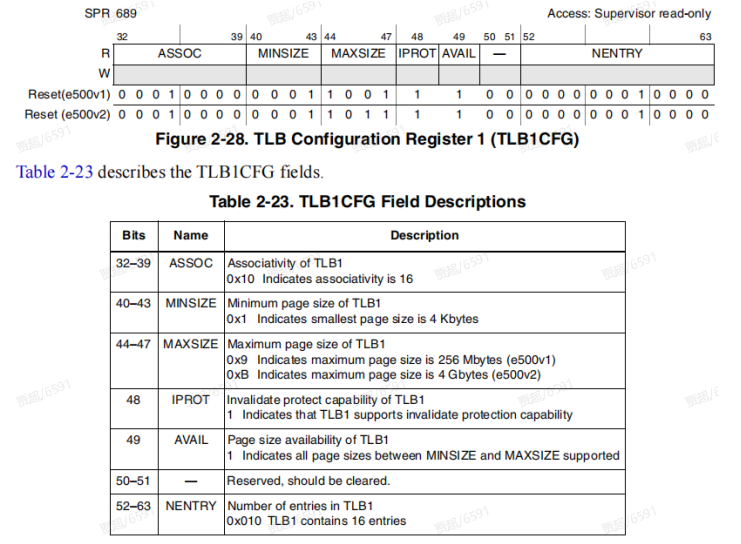

TLB0CFG��TLB1CFG�Ĵ���:��������TLB0��TLB1��������Ϣ,����entry����,ҳ����С����Ϣ��

MAS�����Ĵ���(MAS0�CMAS4, MAS6�CMAS7,û��ʵ��MAS5),��Ҫ���þ���ά��MMU��TLB��entry��

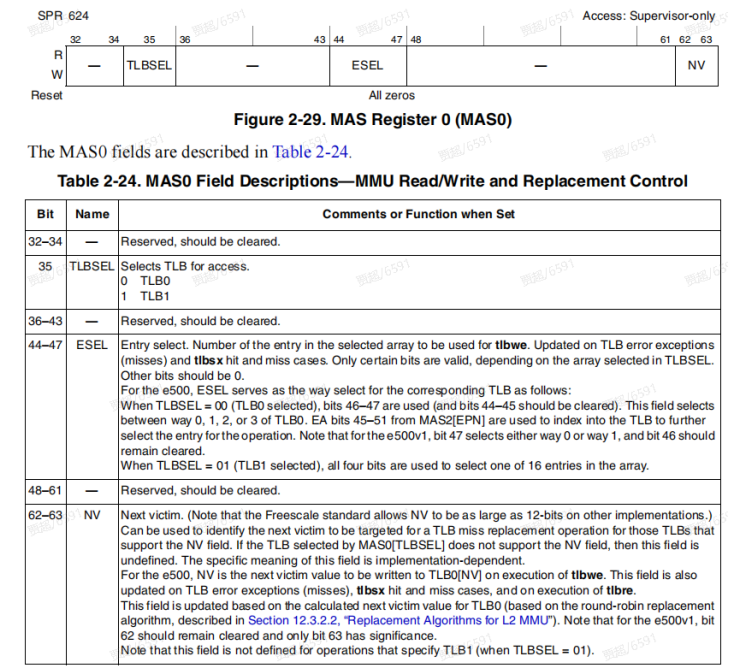

MAS0�Ĵ���:����д�ĸ�TLB���ĸ�entry��TLBSEL�ֶ�����ѡ��Ҫ������TLB,0��ʾTLB0,1��ʾTLB1��ESEL�ֶ�����ѡ��TLB��entry����ʹ��TLB1 ʱ,ESEL�ֶ��е�4λ��Ч,����ѡ��TLB1�е�entry����ʹ��TLB0ʱ,ESEL��ֻ�����λ��Ч,��ΪTLB0����·��������NVλ����ȷ������滻TLB0�е�entry��

MAS1-3�д�ŵĸ����ֶ���TLB entry�еĸ����ֶ�һһ��Ӧ��

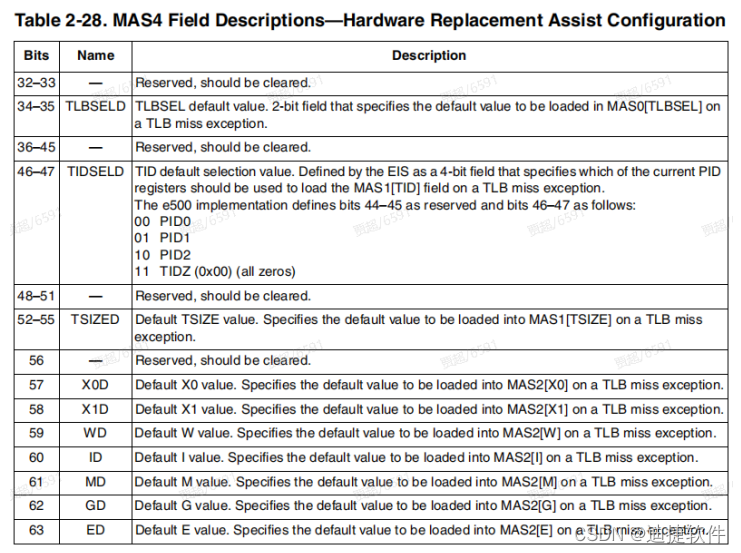

MAS4�Ĵ���

�üĴ�����Ҫ���ڴ�ŵ�TLB miss�쳣����ʱ,��MAS0-3�Ĵ����Զ����ض�ʹ�õ�Ĭ��ֵ,Ҳ����˵MAS4�Ĵ�����������Ӳ��д��ġ�Ϊ�����TLB miss�쳣��Ч��,���쳣����ʱ,E500����MAS4�Ĵ����е�ֵ,�Զ���дMAS0-2�Ĵ����е�һ��������:

? ? MAS0[TLBSEL] <- MAS4[TLBSELD]

? ? MAS1[TID] <- MAS4[TIDSELD]

? ? MAS1[TSIZE] <- MAS4[TSIZED]

? ? MAS2[X0,X1] <- MAS4[X0D,X1D]

? ? MAS2[WIMGE] <- MAS4[WD,ID,MD,GD,ED]

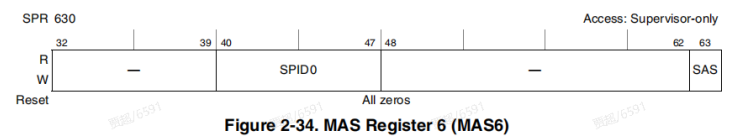

MAS6�Ĵ���:���ڶ�TLB���м���,MAS6�Ĵ����ṩSPID0��SAS,Ҳ����PID��AS�ֶΡ�

MAS7�Ĵ���(ֻE500v2֧��):����ʵ�ֵ�RPN�ĸ߽�ַλ֧�ֳ���32λ��������ַ��

2.4 TLB���ָ���ʵ��

SkyEye,����ȫ����Ŀȫ����ʵʱ��������,�ǻ��ڿ��ӻ���ģ��Ӳ����Ϊ������ƽ̨,֧���û�ͨ����ק�ķ�ʽ��Ӳ��������Ϊ����ķ���ͽ�ģ��SkyEye֧��PowerPC�ܹ�E500��������ָ�����,Ϊ��֧�����а���MMU��Ԫ�IJ���ϵͳ(����VxWorks��Linux��),��Ҫʵ�ֶ�MMU�ķ��湦��,���а���TLB(Translation Lookaside Buffer,ת��������)��ص�ָ��ʵ�ֺ�MMU��ʵ������̡�

��TLB��ص�ָ������:

-

tlbreָ��:tlbreָ���Ǵ�L2 MMU�ж�ȡ����TLB��Ŀ�ĸ��ֶ�����,��д�뵽MMU����(MAS)�Ĵ�������Ӧ�ֶ��С���ȡ��entry��Ŀ����MAS0��TLBSEL��ESEL��MAS2�Ĵ�����EPN�ֶ�ָ��,�ڶ�TLB1ʱ,ESEL��Ч,EPN��Ч;�ڶ�TLB0ʱ,ESEL��2λ��Ч,EPN��Ч��ע��,����E500v2,���HID0[EN_MAS7_UPDATE] = 1, MAS7Ҳ������ΪTLB�����������ַ��

-

tlbweָ��:��ָ���Ǵ�MMU�����Ĵ���(MAS)����ȡ���ֶ����ݲ�д�뵽L2 MMU�еĵ���TLB��Ŀ�С�д���entry��Ŀ����MAS0��TLBSEL��ESEL��MAS2�Ĵ�����EPN�ֶ�ָ��,��дTLB1ʱ,ESEL��Ч,EPN��Ч;��дTLB0ʱ,ESEL��2λ��Ч,EPN��Ч��ע��,����E500v2,MAS7�е�RPN�ֶ�Ҳд�뵽ѡ����TLB��Ŀ�� ��

-

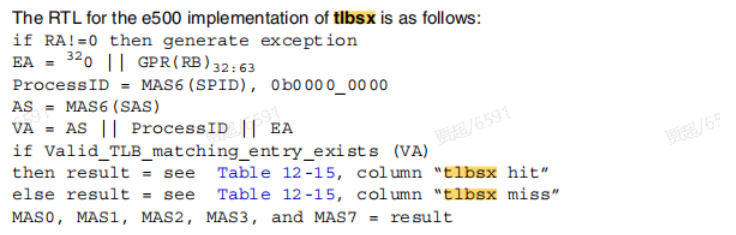

tlbsxָ��:ָ���ʽΪtlbsx RA,RB��ָ��������ʹ��RA+RB�ĵ�ַ,���MAS6�Ĵ�����TLB���в���,�������,�������MAS0-3�Ĵ�����

ָ��ʵ��:

-

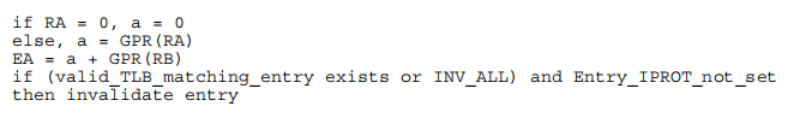

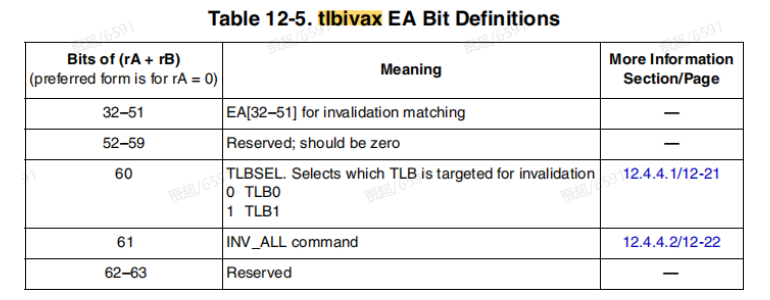

tlbivaxָ��:TLB��Ч����,����ָ�ʹ������˼�����������ַ���Ӧ��TLB����ʧЧ,ͬ��Ҳ��ʹ������������TLB�а�����TBL����ʧЧ��

������Ч��ַEA��Bit61λ�����Ƿ�����Чȫ����entry,�������,��������Ӧ��entry,Ȼ������entry->v = 0����ʹ����ʧЧ��

-

tlbsyncָ��:��ָ������ͬ����TLB entry�Ķ�д����Ҫ��;�ǽ�tlbivaxָ��ĸ���entry�㲥��ϵͳ������,����ͬ������������,��ָ��ֻ��SMPϵͳ����Ч��

2.5 ϵͳ��λ���TLB��ʼ״̬

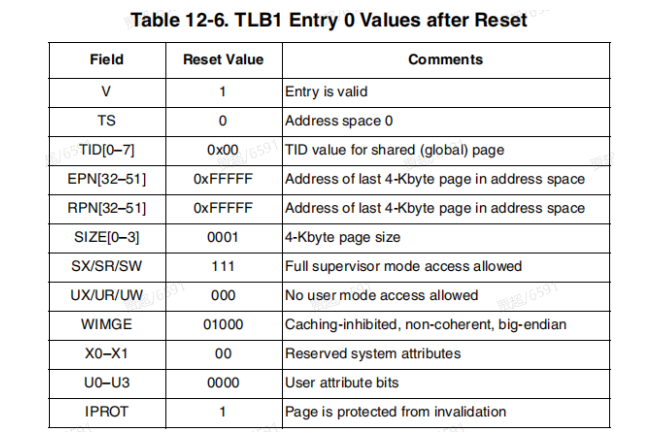

��λ��,L1��L2 MMU�е�TLB����ȫ��ʧЧ,TLB1�ĵ�һ��entry��Ҫ��ʼ����ֵ,������ʾ:

�����:

[1] PowerPC? e500 Core Family Reference Manual.pdf