1. 概述

注意:88EA6321/88EA6320 和 88E6321/88E6320软件上无区别,区别在于硬件外围电源上

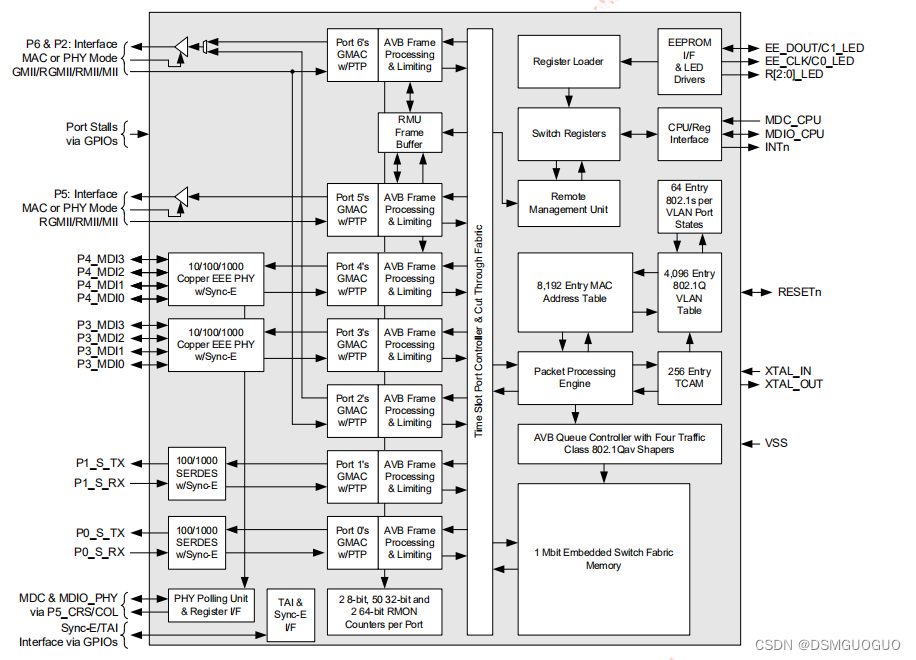

Marvell 88EA6321/88EA6320设备是一个集成了7端口千兆以太网交换机的单芯片,带有两个集成的千兆以太网收发器。该设备支持最新的IEEE 802.1音频视频桥接(AVB)标准。这些设备使用这些AVB技术为AVB流量流识别和预留网络资源,并支持精确的等时流处理能力。这些AVB协议使对时间敏感的多媒体流(如数字视频、音频或工业控制流量)能够通过Ethernet网络发送,具有低延迟和健壮的服务质量保证。

该设备包含两个10/100/1000三倍速度以太网收发器(phy),两个千兆SERDES和三个数字接口,在128针QFP包中支持GMII、RGMII和MII接口的组合。

该设备包含一个PHY轮询单元(PPU),将链路、速度、双工和暂停信息从外部PHY传输到其关联的MAC(内部PHY使用直接方法,即使PHY轮询被禁用为零端口偏移0x00)。只有当外部PHY的SMI地址与交换机中连接的物理端口号匹配时,PPU才能执行此作业(即,连接到端口5的PHY使用SMI地址0x05,连接到端口6的PHY使用SMI地址0x06等)。

即使PPU可以完全访问外部和内部的PHY的寄存器,软件也可以通过使用SMI命令和数据寄存器(Global2,偏移0x18和0x19)随时访问所有的PHY寄存器。

如果在端口上禁用PHY轮询(即端口的PHYDetect位为零),软件必须根据该端口的PHY寄存器的链接、速度、双工和暂停设置(在PCS控制寄存器偏置0x01)。链路必须是最后一个模式寄存器设置,而链路关闭必须是清除的第一个模式寄存器(即,端口的速度、双工和暂停模式只能在端口的链路关闭时更改)。

此外,该芯片通过SMI接口配置内部寄存,从而达到预期效果。SMI 地址基于 ADDR[4:0]n 的反转值。 默认配置上拉电阻(将 ADDR[4:0]n 引脚设置为 0x1F),反过来又将实际 SMI 地址设置为 0x0(这意味着设备在单片机中) 寻址模式)。 或者,如果 ADDR[4:0]n = 0x0,则 SMI 地址将设置为 0x1F。

2. 88EA6321/88EA6320 顶层框图

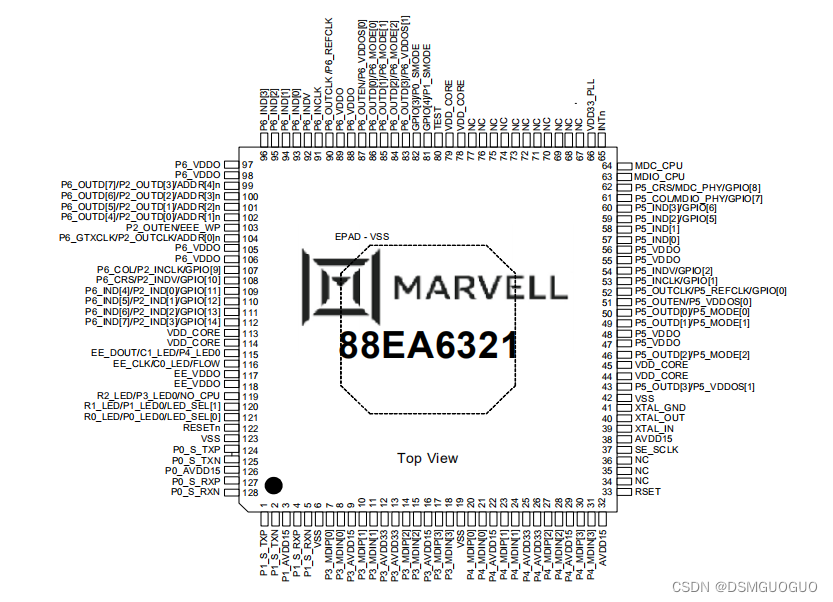

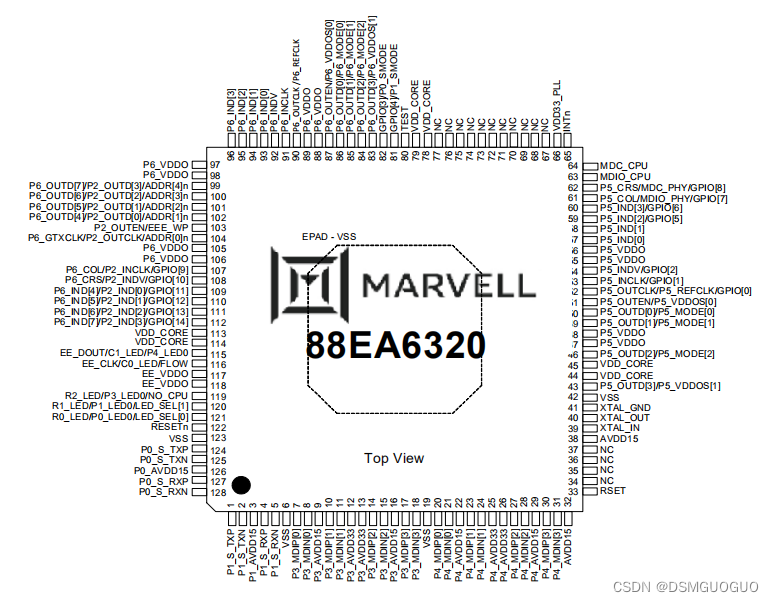

3. 芯片PIN脚图

3.1 88EA6321 Pin脚图

3.2 88EA6320 Pin脚图

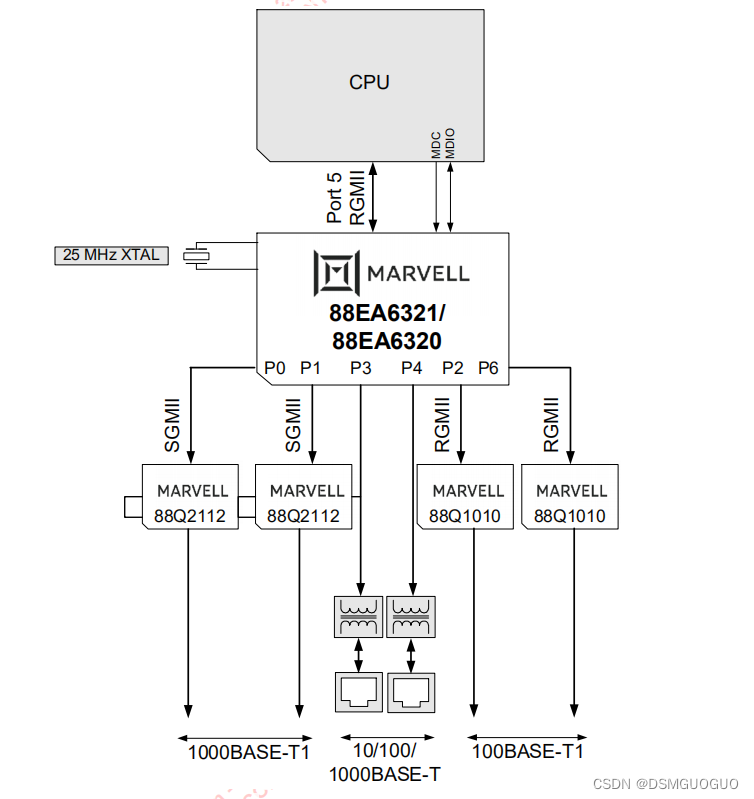

4. 应用实例

由下图可知88EA6321 共有7个Port口,其中一路Port口用作与主控芯片链接组网(图中为PORT5)。

系统时钟采用外部晶振提供(25MHZ), 剩余6个Port口中,两路Port口内部集成了千兆PHY。

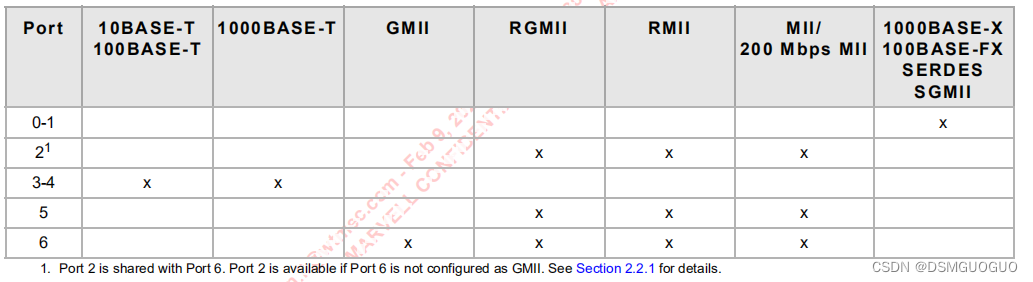

5. Port口分析

该设备包含许多支持铜质介质的接口。下图列出了在该设备的每个端口上所支持的接口。

返回总目录